Известны аналоговые дешифраторы, содержащие схемы сравнения входного и эталонного напряжений, имеющие «единичный и «нулевой выходы, и логические элементы И, ИЛИ.

Предложенное устройство отличается тем, ЧТО в нем «единичный выход схемы сравнения связан с первым входом соответствующей двухвходовой схемы И, второй вход которой соединен с «нулевым выходом соседней схемы сравнения, выходы схем Я попарно объединены схемой ИЛИ, а «единичные и «нулевые выходы всех схем сравнения, кроме ТОГО, подключены соответственно к двум многовходовым схемам И.

Это позволяет упростить устройство и расщирить ВОЗМОЖНОСТИ его применения при каскадном включении.

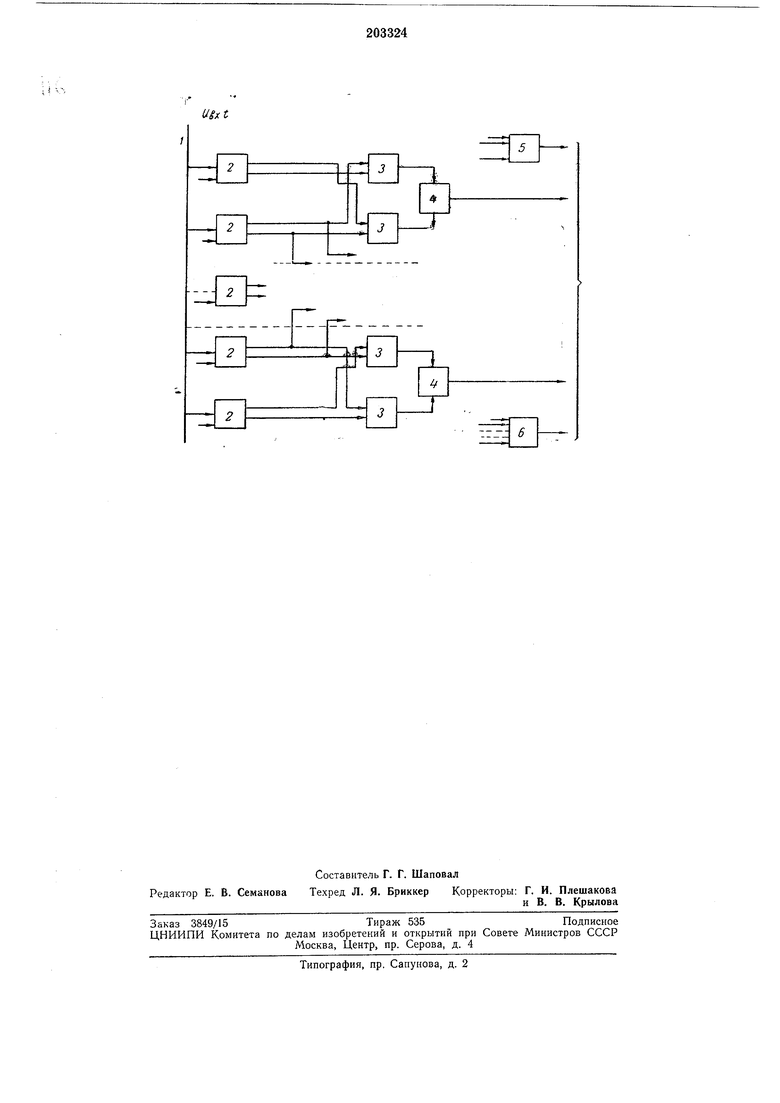

Блок-схема устройства представлена на чертеже.

Сигнал (t) с входной шины / подан параллельно на все схемы сравнения 2, на вторые входы которых подключены источники напряжений заданных уровней. Каждая из схем сравнения имеет два выхода: «единичный и «нулевой. «Единичные выходы каждой схемы сравнения подключены к схеме 3 И, S. «нулевые связаны со входом другой схемы 3 И, на вход которой подключен единичный вход последующей схемы сравнения, и Т. д.

Выходы соседних схем 3 связаны со схемами 4, ИЛИ, выходные шины которых образуЮТ выход всего устройства.

Такое включение выходов схемы сравнения, соответствует логике работы комбинационного двоичного полусумматора на два входа без цепи переноса.

Кроме перечисленных элементов, устройство содержит две многовходовые схемы 5 и 6 И. Входами цервой из них являются «единичные выходы всех схем сравнения 2, а входами второй - «нулевые выходы схем сравнения.

Предмет изобретения

Аналоговый дешифратор, содержащий схемы сравнения входного и эталонного напряжений, имеющие «единичный и «нулевой выходы, и логические элементы И, ИЛИ, отличающийся тем, ЧТО, с целью упрощения устройства, в нем каждый «единичный выход схемы сравнения связан с первым входом

соответствующей двухвходовой схемы И, второй вход которой соединен с «нулевым выходом соседней схемы сравнения, выходы схем И попарно объединены схемой ИЛИ, а «единичные и «нулевые выходы всех схем

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2000 |

|

RU2189110C2 |

| Устройство для автоматического контроля и поиска неисправностей | 1977 |

|

SU696463A1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1979 |

|

SU855648A1 |

| Способ следящего аналого-цифрового преобразования и устройство для его осуществления | 1983 |

|

SU1229954A1 |

| Устройство для цифровой магнитной записи | 1977 |

|

SU699546A1 |

| Параллельный комбинационныйСуММАТОР | 1978 |

|

SU798827A1 |

| АНАЛИЗАТОР ФУНКЦИЙ УОЛША | 2000 |

|

RU2203504C2 |

| Устройство для высокоплотной цифровой магнитной записи | 1977 |

|

SU690553A1 |

| Троичное счетное устройство | 1988 |

|

SU1580535A2 |

Даты

1967-01-01—Публикация