Изобретение относится к автоматике и вычислительной технике, в частности к пороговым логическим элементам.

Известен многопороговый логический элемент [1], состоящий из линейного сумматора и подключенного к нему многопорогового дискриминатора, в состав которого входят однопороговые последовательно включенные дискриминаторы на логических элементах И-НЕ с подключенным к выходу одного из них асинхронным RS-триггером.

Недостатком такого многопорогового логического элемента являются низкое быстродействие, а также способность реализовать только периодические переключательные функции [2].

Наиболее близким по технической сущности к предлагаемому является многопороговый логический элемент [3], содержащий линейный сумматор, состоящий из входных диодов, аноды которых через соответствующие резисторы подключены к положительному полюсу источника питания и к анодам соответствующих разделительных диодов, катоды которых соединены со входом резисторного делителя, выходы которого соединены с первыми входами соответствующих элементов И-НЕ, образующих однопороговые дискриминаторы, выходы нечетных однопороговых дискриминаторов соединены со входами многовходового логического элемента И-НЕ, второй вход каждого из них подключен к выходу соответствующего четного однопорогового дискриминатора с ближайшим большим порогом срабатывания, вторые входы четных однопороговых дискриминаторов подключены к положительному полюсу источника питания.

Недостатком этого многопорогового логического элемента является то, что при смене на его входах двоичных наборов на выходе элемента может иметь место риск сбоя из-за наличия в схеме последовательно включенных однопороговых дискриминаторов на логических элементах И-НЕ.

Задача, решаемая изобретением, - устранение рисков сбоя на выходе многопорогового логического элемента при изменении двоичных наборов на его входах.

Поставленная задача решена за счет того, что в известный многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов, аноды которых через соответствующие резисторы подключены к положительному полюсу источника питания и к анодам соответствующих разделительных диодов, катоды которых соединены со входом резисторного делителя, выходы которого соединены с первыми входами соответствующих элементов И-НЕ, образующих однопороговые дискриминаторы, выходы нечетных однопороговых дискриминаторов соединены со входами многовходового логического элемента И-НЕ, второй вход каждого из них подключен к выходу соответствующего четного однопорогового дискриминатора с ближайшим большим порогом срабатывания, вторые входы четных однопороговых дискриминаторов подключены к положительному полюсу источника питания, дополнительно введены асинхронный RS-триггер на логических элементах И-НЕ, двухвходовой логический элемент И-НЕ, одновибратор и усилитель, вход которого подключен к выходу линейного сумматора, выход соединен со входами запуска одновибратора, выход которого подключен к первому входу двухвходового логического элемента И-НЕ и дополнительному входу многовходового логического элемента И-НЕ, выход которого соединен со входом установки в единицу RS-триггера и вторым входом двухвходового логического элемента И-НЕ, выход которого связан со входом установки в ноль RS-триггера, прямой выход которого подключен к выходной клемме многопорогового логического элемента.

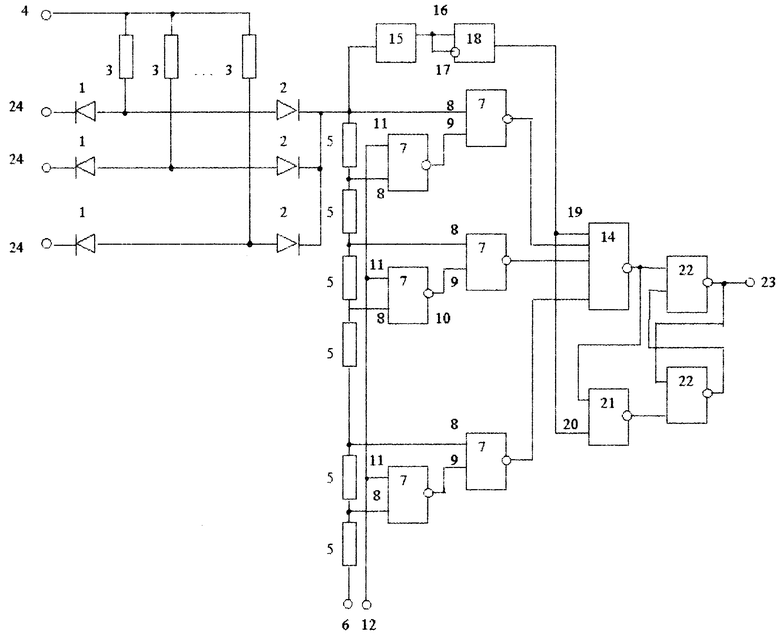

На чертеже представлена функциональная схема устройства.

Многопороговый логический элемент содержит n-входовой линейный сумматор, многопороговый дискриминатор, многовходовой логический элемент И-НЕ, усилитель, одновибратор, двухвходовой логический элемент И-НЕ и асинхронный RS-триггер на логических элементах И-НЕ. Линейный сумматор для каждого входа содержит попарно соединенные кремниевые диоды 1 и 2. Каждая пара диодов в точках, объединяющих их аноды через резисторы 3, управляющие весовыми коэффициентами по соответствующему входу, подключена к положительному полюсу источника 4 смещения. Катоды диодов 2 объединены и подключены через делитель из резисторов 5 к отрицательному полюсу источника 6 смещения. Многопороговый дискриминатор представляет собой несколько соединенных однопороговых дискриминаторов 7, выполненных на двухвходовых элементах И-НЕ. Вход 8 каждого однопорогового дискриминатора соединен с соответствующим делителем из резисторов 5, развязывая тем самым каждый последующий дискриминатор с большим порогом срабатывания от предыдущего. Входы 9 нечетных однопороговых дискриминаторов соединены с выходами 10 четных однопороговых дискриминаторов с ближайшим большим порогом срабатывания. Входы 11 четных однопороговых дискриминаторов объединены и подсоединены к положительному полюсу источника 12 питания. Выходы 13 нечетных однопороговых дискриминаторов соединены со входами многовходового логического элемента И-НЕ 14. Выход линейного сумматора соединен со входом усилителя 15, выход которого подключен к объединенным прямому 16 и инверсному 17 входам управления одновибратора 18, выход которого связан с дополнительным входом 19 многовходового логического элемента И-НЕ 14 и первым входом 20 двухвходового логического элемента И-НЕ 21. Второй вход элемента И-НЕ 21 соединен с выходом многовходового логического элемента И-НЕ 14 и входом установки в единицу RS-триггера на элементах И-НЕ 22, а выход - со входом установки в ноль RS-триггера.

Прямой выход RS-триггера соединен с выходной клеммой 23 многопорогового логического элемента. Клеммы 24 являются входами многопорогового логического элемента.

Многопороговый логический элемент работает следующим образом. Положим, что задержка распространения сигнала через логические элементы 7, 14 И-НЕ составляет τ. Одновибратор 18 в стабильном состоянии формирует на своем выходе уровень логической единицы. Переход в нестабильное состояние осуществляется под воздействием положительного перепада напряжения на входе 16 или отрицательного перепада напряжения на входе 17. Усилитель 15 необходим для увеличения уровней перепадов напряжений на входе резисторного делителя в уровни, достаточные для устойчивого запуска одновибратора 18. Пусть время нестабильного состояния одновибратора 18 составляет t, а переход из стабильного в нестабильное осуществляется через промежуток времени τ>τ1>0 от момента изменения уровня сигнала на входе резисторного делителя.

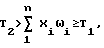

При поступлении на входные клеммы 24 многопорогового логического элемента двоичного набора, состоящего из одних нулей, диоды 1 проводят ток от источника смещения 4 через соответствующие резисторы 3. На входах 8 однопороговых дискриминаторов 7 присутствует потенциал логического нуля, одновибратор 18 находится в стабильном состоянии, нулевой сигнал с выхода многовходового логического элемента И-НЕ 14 устанавливает RS-триггер в единичное состояние, что приводит к появлению в клемме 23 высокого уровня сигнала, соответствующего "логической единице". Пусть теперь на входные клеммы 24 подан такой набор переменных, что

где X -значение входной переменной, ω - вес i-го входа, T1, T2 - пороги срабатывания первого и второго однопороговых дискриминаторов.

В этом случае ток от источника 4 смещения через резисторы 3 и соответствующие диоды 2 поступает в цепь делителя из резисторов 5, вызывая положительный перепад напряжения и запуск одновибратора 18 через промежуток времени τ1. Потенциал входа 8 однопорогового дискриминатора 7 с наименьшим порогом срабатывания становится достаточным, чтобы на его выходе 13 появился уровень напряжения, соответствующий "логическому нулю". Через промежуток времени τ1+t на выходе одновибратора 18 установится высокий потенциал, который, поступая на входы 19 и 20 элементов И-НЕ, вызовет переключение RS-триггера в нулевое состояние.

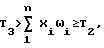

Если нулевой набор аргументов на входе многопорогового логического элемента сменяется набором, для которого выполняется

то на входах 8 дискриминаторов с порогами срабатывания Т1 и Т2 установится высокий уровень напряжения, достаточный для их срабатывания. Через промежуток времени τ на их выходах 13 появится низкий уровень напряжения, а через время 2τ на выходе 13 однопорогового дискриминатора с порогом срабатывания T1 высокий уровень напряжения восстановится. Таким образом, на выходе однопорогового дискриминатора с порогом срабатывания T1 на время τ появится уровень напряжения, соответствующий "логическому нулю" (риск сбоя в "1"). Чтобы этот "ложный ноль" не повлиял на правильность реализации функции многопороговым логическим элементом на выходе 23, величина τ1+t должна превышать 2τ.

В этом случае высокий уровень напряжения на выходе одновибратора 18 (после возвращения его в стабильное состояние) разрешит передачу сигнала с выхода многовходового логического элемента И-НЕ 14 на входы RS-триггера. Поскольку в рассматриваемом случае это будет уровень "логического нуля", то RS-триггер так и останется в единичном состоянии.

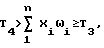

Рассмотрим теперь случай, когда j-тый входной набор переменных, для которого

сменяется (j+1)-ым набором входных сигналов, удовлетворяющим

Поскольку взвешенная сумма для j-го и (j+1)-го наборов равна или превышает нечетный порог, но меньше последующего четного, то выходная функция многопорогового логического элемента должна остаться равной нулю. Рассмотрим процессы, происходящие в схеме многопорогового логического элемента. При переходе от j-го набора входных переменных к (j+1)-му на входах 8 однопороговых дискриминаторов 7 с порогами срабатывания Т5 и Т4 устанавливается низкий уровень напряжения, запрещающий их срабатывание. Через промежуток времени τ на их выходах 13 и 10 установится уровень "логической единицы". Через промежуток времени 2τ на выходе однопорогового дискриминатора с порогом срабатывания Т3 установится уровень напряжения, соответствующий "логическому нулю". Таким образом, на всех входах многовходового логического элемента 14 И-НЕ, связанных с выходами однопороговых дискриминаторов 13, в течение времени τ будут присутствовать сигналы "логических единиц". Чтобы это не повлияло на правильность реализации функции многопороговым логическим элементом, должно соблюдаться условие τ1+t>2τ. Поскольку при переходе от j-го к (j+1)-му входному набору на входе резисторного делителя напряжение уменьшается, то одновибратор 18 переходит в нестабильное состояние под воздействием сигнала на входе 17. Высокий уровень напряжения на выходе одновибратора 18 после его возвращения через промежуток времени τ1+t в стабильное состояние разрешит передачу сигнала с выхода элемента 14 И-НЕ на входы RS-триггера. Поскольку это будет уровень "логической единицы", то триггер так и останется в нулевом состоянии.

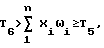

Аналогичным образом происходит работа многопорогового логического элемента и при других вариантах смены двоичных наборов на входах 24. При этом, если сменяющий набор удовлетворяет условию

то на выходе 23 устанавливается уровень "логического нуля". Если сменяющий входной набор удовлетворяет условию

то на выходе 23 после завершения переходных процессов устанавливается уровень "логической единицы".

Указанные изменения в структуре многопорогового логического элемента позволяют устранить на его выходе последствия рисков сбоя, возникающих на выходах его внутренних элементов. Это делает возможным использование многопорогового логического элемента в асинхронных цифровых устройствах.

ЛИТЕРАТУРА

1. Авторское свидетельство СССР 900455, кл. Н 03 К 19/12.

2. Пальянов И.А., Потапов В.И. Схемотехника и контроль элементов пороговой логики. Изд-во ОмГТУ, 1994, 154 с.

3. Авторское свидетельство СССР 788384, кл. Н 03 К 19/42.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1985 |

|

SU1272499A2 |

| Многопороговый логический элемент | 1979 |

|

SU788384A1 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

| Многопороговый логический элемент четности | 1980 |

|

SU900455A2 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| Многопороговый логический элемент четности | 1977 |

|

SU660261A2 |

| Многопороговый логический элемент четности | 1976 |

|

SU608266A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Многопороговый логический элемент | 1979 |

|

SU790341A1 |

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых устройствах. Техническим результатом изобретения является устранение рисков сбоя на выходе многопорогового логического элемента (МПЭ), возникающих при изменении двоичных наборов на его входах. МПЭ соержит линейный сумматор (ЛС), состоящий из входных диодов, аноды которых через соответствующие резисторы подключены к положительному полюсу источника питания и к анодам соответствующих разделительных диодов, катоды которых соединены со входом резисторного делителя, выходы которого соединены с первыми входами соответствующих элементов И-НЕ, образующих однопороговые дискриминаторы (ОПД). Выходы нечетных ОПД соединены со входами многовходового логического элемента И-НЕ, второй вход каждого из них подключен к выходу соответствующего четного ОПД с ближайшим большим порогом срабатывания. Вторые входы четных ОПД подключены к положительному полюсу источника питания. В МПЭ дополнительно введены асинхронный RS-триггер на логических элементах И-НЕ, двухвходовой логичеческий элемент И-НЕ, одновибратор и усилитель, вход которого подключен к выходу ЛС, выход соединен со входами запуска одновибратора. Выход одновибратора подключен к первому входу двухвходового логического элемента И-НЕ и дополнительному входу многовходового логического элемента И-НЕ, выход которого соединен со входом установки в единицу RS-триггера и вторым входом двухвходового логического элемента И-НЕ. Выход двухвходового логического элемента И-НЕ связан со входом установки в ноль RS-триггера, прямой выход которого подключен к выходной клемме МПЭ. 1 ил.

Многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов, аноды которых через соответствующие резисторы подключены к положительному полюсу источника смещения и к анодам соответствующих разделительных диодов, катоды которых через резисторный делитель подключены к отрицательному полюсу источника смещения, выходы резисторного делителя соединены с первыми входами соответствующих элементов И-НЕ, образующих однопороговые дискриминаторы, выходы нечетных однопороговых дискриминаторов соединены с соответствующими входами многовходового логического элемента И-НЕ, второй вход каждого однопорогового дискриминатора подключен к выходу соответствующего четного однопорогового дискриминатора с ближайшим большим порогом срабатывания, вторые входы четных однопороговых дискриминаторов подключены к положительному полюсу источника питания, отличающийся тем, что в него введены асинхронный RS-триггер на логических элементах И-НЕ, двухвходовой логический элемент И-НЕ, одновибратор и усилитель, вход которого подключен к выходу линейного сумматора, выход усилителя соединен со входами запуска одновибратора, выход которого подключен к первому входу двухвходового логического элемента И-НЕ и дополнительному входу многовходового логического элемента И-НЕ, выход которого соединен со входом установки в единицу RS-триггера и вторым входом двухвходового логического элемента И-НЕ, выход которого связан со входом установки в ноль RS-триггера, прямой выход которого подключен к выходной клемме многопорогового логического элемента.

| Многопороговый логический элемент | 1979 |

|

SU788384A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU900455A2 |

| Переключающее устройство | 1980 |

|

SU900453A1 |

| US 4879504 A, 07.11.1989. | |||

Авторы

Даты

2002-09-10—Публикация

2000-08-04—Подача