1

Изобретение относится к средствам вычислительной техники.

Уже известны устройства для иростра нственно-времекиого сейсмического анализа, содержащие циклический аналоговый коммутатор, информационные входы которого соединены с выходами датчиков, а выход через аналого-дифровой преобразователь подключен к ин.формационным входам буферного регистра записи, выходы которого соединены с иервой груипой входов блока оперативной намяти, синхронизатор с нодключеииым к двум его входам соответственно местным и внешним генераторами тактовых импульсов, наиель оператора и выходной нараллельный иакаплнпаюнций сум матор.

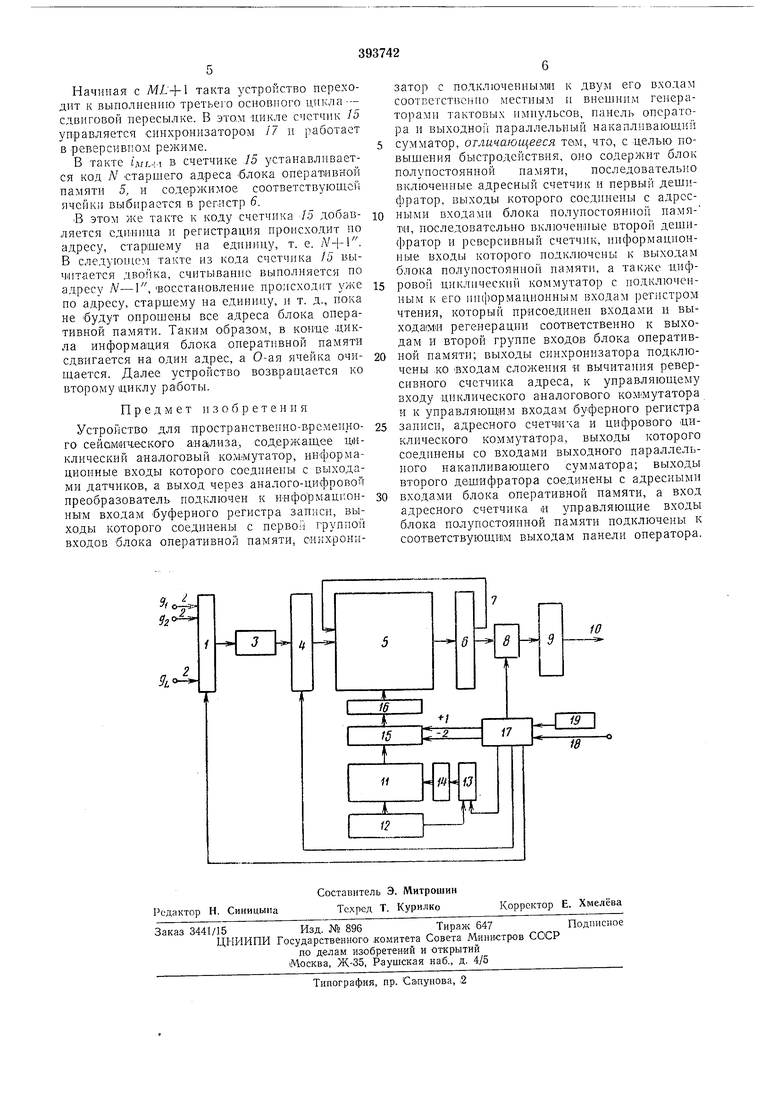

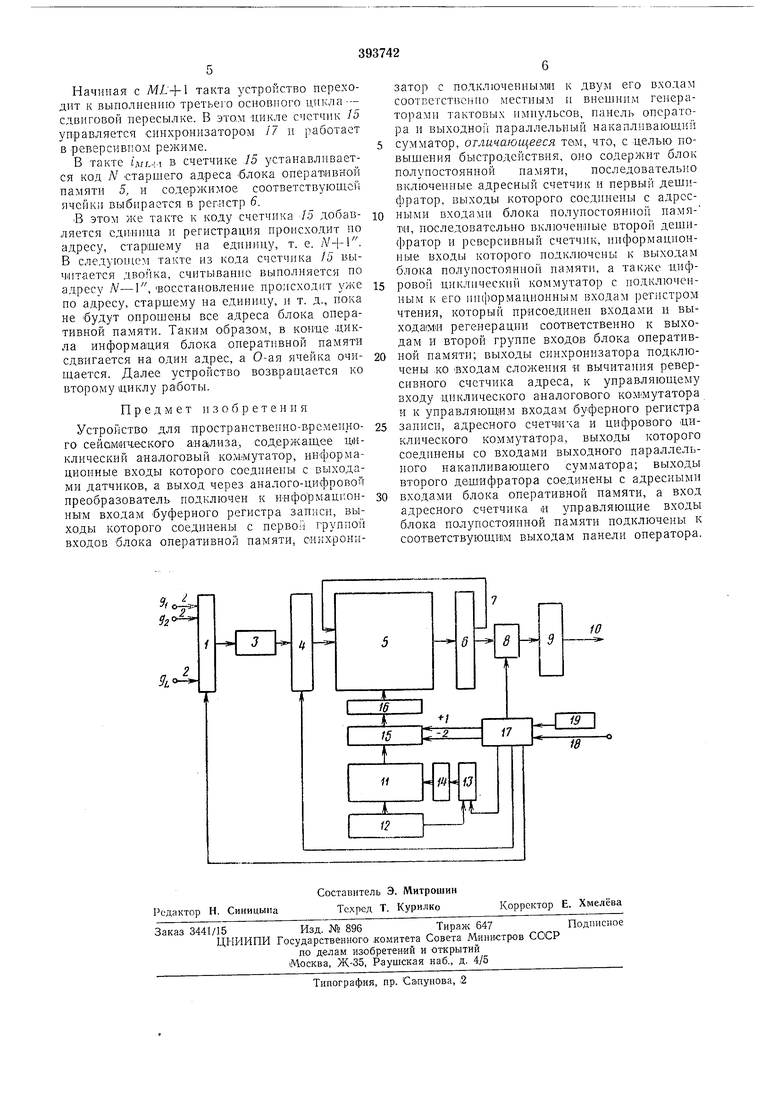

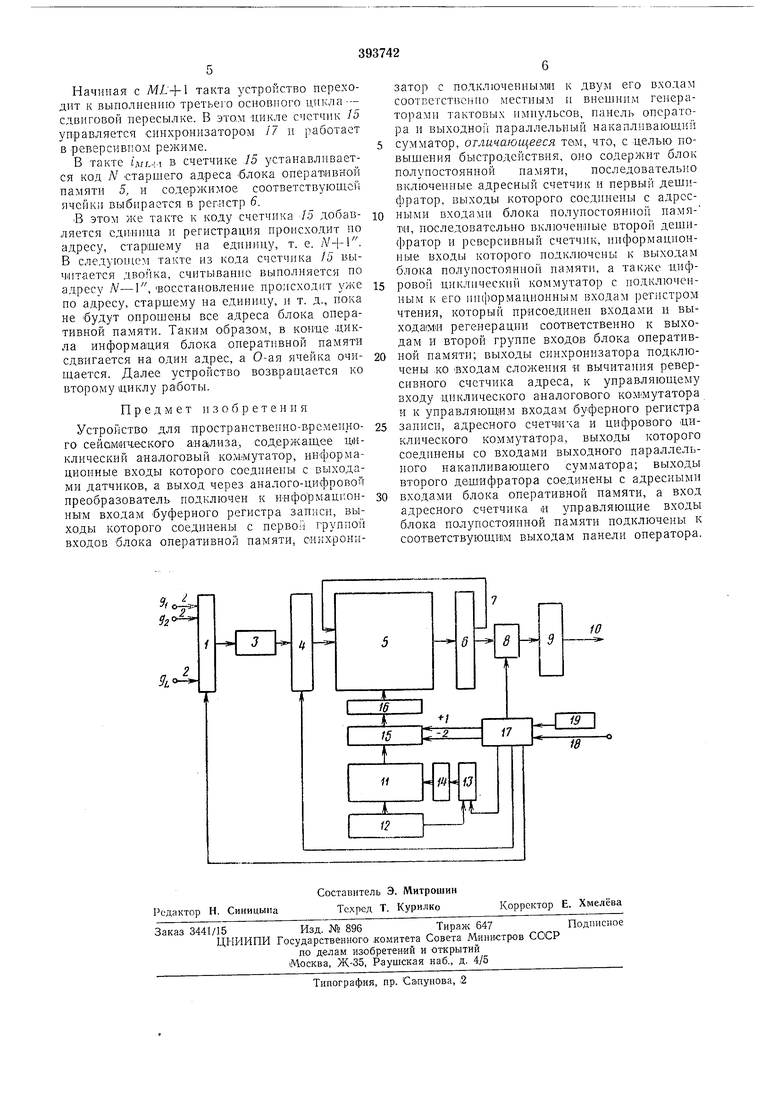

Цель изобретения - повышение быстродействия устройства. Достигается она, тем, что нредлагаелюе устройство содержит блок иолупостояппой памяти, последовательно включеиные адресиый счетчик и первый дешифратор, выходы которого соедииены с адресными входалти блока полуиостоянной иамяти, последовательно включенные второй дешифратор и реверсивный счетчик, информационные входы которого подключены к выходам блока нолуностоянной намяти, а также цифровой циклический коммутатор с подключенным к его информашюииым входам рспистром чтения, который присоединен входами и выходами регенерации соответственно к выходам и второй группе входов блока оперативной памяти; выходы синхронизатора подключены ко входам сложения и вычитания реверсивного счетчика адреса, к управляющему входу циклического аналогового коммутатора и к управляющим входам буферного регистра записи, адресного счетчика и цифрового циклического коммутатора, выходы которого соединены со входами выходного параллельного накапливающего сумматора; выходы второго дешифратора соединены с адресными входами блока оперативной памяти, а вход адресного счетчика и управляющие входы блока нолуиостояиной памяти иодключены к соответствующим выходам панелн оператора. На чертеже приведена схема устройства. Устройство содер кит входной цнклический аналоговый коммутатор /, связанный входны, мн тенями 2 с выходами датчиков gi, gz

gL; n-разрядный аналого-цифровой нреобразователь 3; входной-буферный nL-разрядный регистр записи 4; блок оперативной памяти 5 объемом Tmax-fg пЬ-разрядиых слов; выходной «.-разрядный регистр чтения 6, соединенный с блоком оперативной памятн 5 цепями регенерации 7; /i-разрядный цифровой циклический коммутатор 8; (rt+lg2.L)-разрядный параллельный накапливающий сумматор 9, выдающий результат (в UBA, накопитель либо на пороговый дифровой индикатор) по шипам 10; блок полупостоянной памяти // o6i;eМОМ Ilg2T,,,aa--/g-pa3p l,T, СЛОВ, СВКЗаП) l.li

с иа:пелью оператора 12, управляемый Igs/-разрядным адрссны;М счетчиком 13 через дешпфратор 14; lg2Tmox:fg-разрядный регистр - реверсиВНЫй счетчик 15 адреса блока оперативной -памяти 5 (он же является регистром ч«сла), дешифратор 16, синхронизатор 17, соедипеииый цепью 18 с источником в 1ешних тактируюш,их импульсов, и местный генератор TaivTOBbix имнульсов 19.

Аналоговый коммутатор / непрерывно опрашивает датчики по цепям 2 с частотой /g-.-. Аиалого-щпфровой преобразователь 3, ci-;;:хроинзируемый синхронизатором /7 с частотой fg-Ln, преобразует аналоговый сигнал в /гL-paзpядный двоичный код, который записывается в rt-/.-разрядный регистр 6, заполняемый за один такт временного квантования входього сигнала 4Процесс функционировання собственно схемы формирования результата Pi(tk) разбивается на три основных щнкла:

а)предварительное накопление первичного массива информаднн в блоке оперативной памяти 5 обтземом A Tmo.T-fg «-.-разрядных слов за время tmn.v; цнкл выполняется только один раз включении устройства (он равен /V тактам днскретнзадии сигнала);

б)выборка в регистр 6 слов из -блока оперативной памяти 5 по соответствующим адресам, фиксированным в блоке полупостоянпой памяти 11, дешифрация в каждом такте выборкн п-разрядиых кодов внутри регистра 6 с помощью циклического коммутатора 8, управляемого синхронизатором 17 в соответствии со сдвиго,м задержек при переходе от вычисления Pj(ti;) к Pj+i(th), п сложение окончательно выбранных кодов в схеме параллельного /г-разрядного накапливающего сумматора 9; в этом |цикле производятся /,-М выборок из блока оперативпо па.мяти 5 с регенерацпей ниформании и столько же параллельных сложений в сумматоре; )1осле ка/1;дых /. Сложенн |;ыдается результат lj(tii);

в)сдвиговая пе) по н.ниам 7 iiL.разрядных слов блока оперативной памяти 5 но адресам, стар.им1М на единицу; при этом слово по адресу вытллкииается из блока, а 5i4ei iKa 0-ным адресом очини1ется. 11Нформацня, иакопнвнгг;яся i; этому лгоменту в регнстре 4, за текущий такт //, записызается в освобод вн1уюся цнкл требует выполнеиня ;V выборок из блока оперативной памяти с регенерацией по нзменеииому .а «-|-1 адресу н одной записи текуи1,ей ииформацни.

В дальпейщем циклы бис иеирер Л) повторяются.

Аналнз циклов б и в работы устройсп а по объему операций, выполняемых в каждь; такт дискретизации 4, определяет требозг.:; к временным характерг.стикам -блока сператизной намяти 5, блока полупостоянноГ: // и логических схем формирования

Pj(t,)Ice циклы благодаря обнщости логических фуикци ; выполняется одиимн н темп же схемам 1 управления, с той лишь разницей, что в иервом цикле блокируется вход сумматора 9, и величины Pi(th) не вычисляются. Такая организация работы устройства унрощает схемы управления и сокран,ает объем аннаратуры.

Работа схемы тактируется сигналами частоты /./, задаваемой генератором тактовых мнульсов 19, либо импульсами от внещпего «CTO-iHHiia по цепн 18. Си хропизатор /7 предст.лЛзляет собой многоразрядный счетчнк с деП11:(|)ратором, схемами унравлення н расиределения тактирующих нмпульсов. Он вырабатывает путем деления основной частоты сигналы управления аналоговы;м ко.ммутатором

/, а 1алого-цифровы.м нреобразователем 5, а также управляет счетчиком адреса 13, регнстром-счетчнко.м адреса 15 и циклическим коммутатором 6.

Цикл вычисления начннается со второго

такта is главных импульсов. К началу такта i-i синхронизатор 17 устанавливает на счетчике }5 нуль, и дешифратор 16 заносит содержимое О-ой ячейки блока иолупостоянной памяти // в счетчик .13. Дешифратор 14 выбирает

слово по указанному адресу из блока оперативной памяти 5 в регистр 6 н восстанавливает считанное слово. К моменту занесення слова в регнстр 6 циклический коммутатор 8 устанавливается в нуль, и нмнульсом /з 0-ый

/г-разрядный код содержнмого регистра 6 считывается в сумматор 9 н складывается с его нулевым содержимым. Параллельно в такте ь пронсходнт установка (прибавлением едпни.цы к содерж1нмому счетчика 15} следующсго адреса бло;а нолупостоянной памяти 11, а ji такте г-гВыборка нз блока, онеративной намяти 5 второго слова. В такте /.( выбранный един1,.| код (циклический коммутатор в та:же /.; перешел в единичное состояние)

екл;;дь вается с ирсдыдущим кодом в регистре сумматора 9.

Тахнм образо:и, благодаря сов:мещеиню в одиом такте (л- выч5о|м-;и текун-iero слова из блока 5, устаиовки в счетчнке 15 следуюн1,его

адреса в блоке нолупостояниой памяти 11. установки текун1его состояния циклического ;.:()ммутатора 6 и сложення елова, выбранного нз блока 5 в нредыдущем такте, со словом, выбранным в TCicyHieM такте, вее выборкп пз

б.гока 5 для вычисления /Vf сумм нз L слагаеМ1ЛХ происходят в течение M-L тактов, а носледисе значение Ям(//;-) ноявляется на В1;:лолн1;;Х HuiTiax к yVf /,-)-2 та.кте.

1й: -;лическнй i oMMyTaTOp 6 ра-ботает в /.-тактном цикле, пробегая за каждый цикл псе состоян1 Я от пуля до ./-1. При этом в .;ле первого цикла коммутатор устанавливается в нуль, в начале второго - в еднниIHV п т. л.

Начиная с ML+l такта устройство переходит к выполнению третьего основного цикла - сдвиговой пересылке. В это.м цикле счетчик /5 управляется синхронизатором 17 и работает в реверсивном режиме.

В такте IML-VI в счетчике 15 устанавливается код Л старшего адреса блока оперативной памяти 5, и содержимое соответствующей ячейки выбирается в регистр 6.

В этом же такте к коду счетчика 15 добавляется едшпща и регистрация происходит по адресу, старшему на единицу, т. е. Л-|-1. В следующем такте нз кода счетчика /5 вычлтается двойка, считывание выполняется по адресу N-1, восстановление происходит уже по адресу, старшему на единИ|Цу, и т. д., пока не -будут опрогнены все адреса блока оперативной памяти. Таким о бразом, в коице .цикла информация блока оперативной памяти сдвигается на один адрес, а 0-ая ячейка очищается. Далее устройство возвращается ко второму циклу работы.

Предмет изобретения

Устройство для пространствеино-времеиного сейамического а1на|Лиза, содержащее Ц|Иклический аналоговый коммутатор, информациоиные входы которого соединены с выходами датчиков, а выход через аналого-цифровой преобразователь подключен к ияформационным входам буферного регистра записи, выходы которого соединены с первой группой входов блока оперативной памяти, синхронизатор с подключенными к двум его входам соответственно местным и внешним генераторами тактовых нмнульсов, панель оператора н выходной параллельный накапливаюплий сумматор, отличающееся тйм, что, с целью повышения быстродействия, оно содержит блок полупостоянной памяти, последовательно включенные адресный счетчнк и первый деш фратор, выходы которого соединены с адресными входами блока нолуностоянно памяTiH, последовательно включенз1ые второй дешифратор н реверсивный счетчик, информационные входы которого подключены к выходам блока полуностоянной памяти, а также цифровой циклический коммутатор с подключенным к его ииформационным входам регистром чтения, который прИСоединен входами и выходами регенерации соответственно к выходам и второй группе входов блока оперативной памяти; выходы синхронизатора подключены ко Входам сложения и вычитания реверсивного счетчика адреса, к управляющему входу циклического аналогового ком мутатора и к управляющим входам буферного регистра записи, адресного счетчича и цифрового Циклического коммутатора, выходы которого соединены со входами выходного параллельного накапливающего сумматора; выходы второго дбШифратора соединены с адресными входами блока оперативной памяти, а вход адресного счетчика и управляющие входы блока полупостояпной памяти подключеиы к соответствующим выходам панели оператора.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для модификации команд | 1974 |

|

SU542995A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Устройство для контроля памяти | 1981 |

|

SU1001180A1 |

| Цифровой формирователь спектра | 1984 |

|

SU1171804A1 |

Авторы

Даты

1973-01-01—Публикация