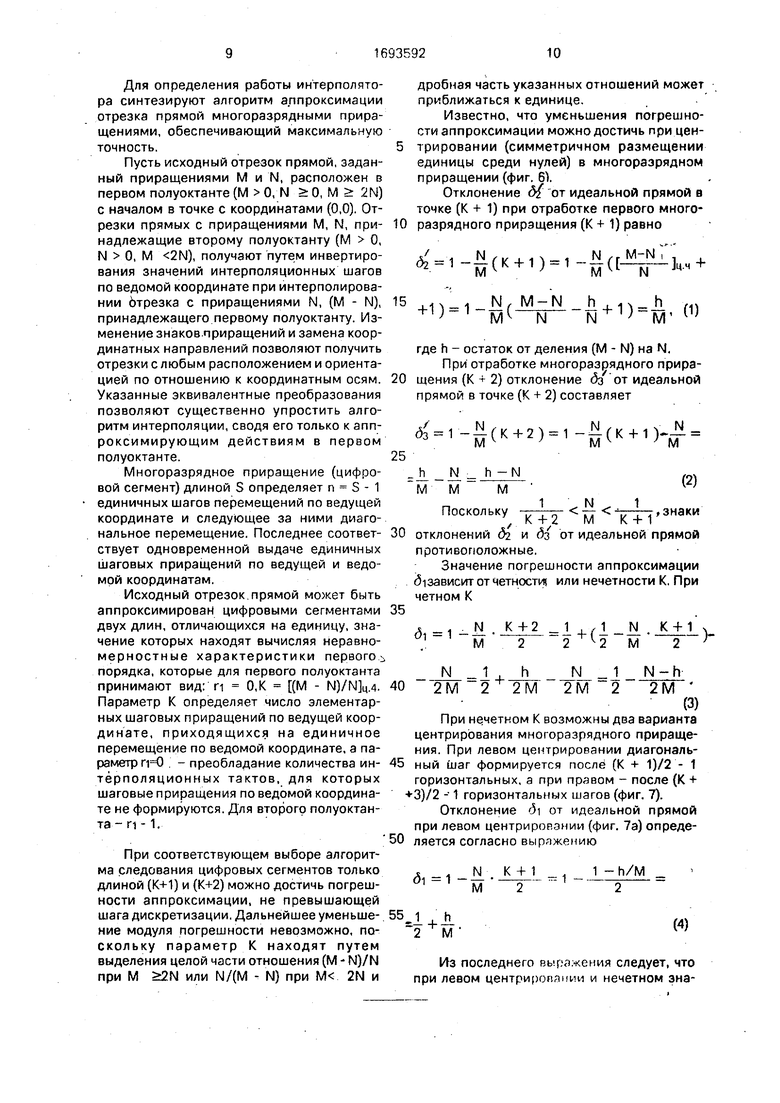

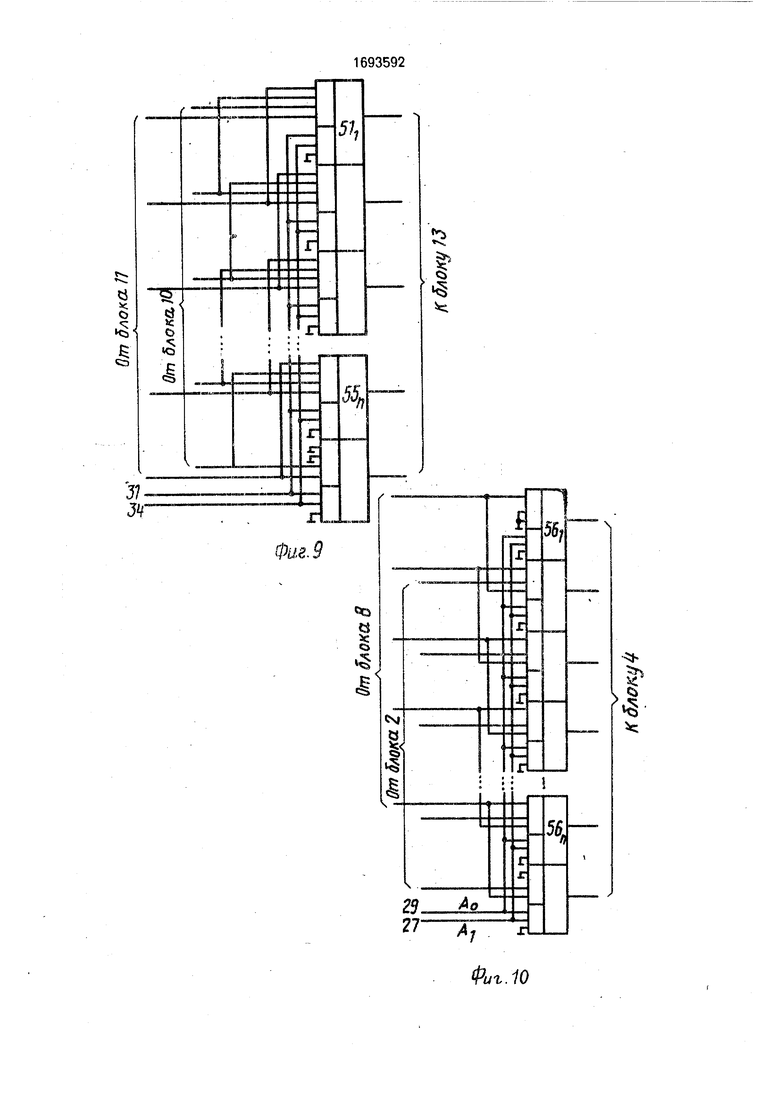

словии их центрирования; на фиг. 7 - схеы расположения единичного элемента при евом и правом центрировании; на фиг. 8 10 - схемы коммутаторов; на фиг, Л - сегенты.5

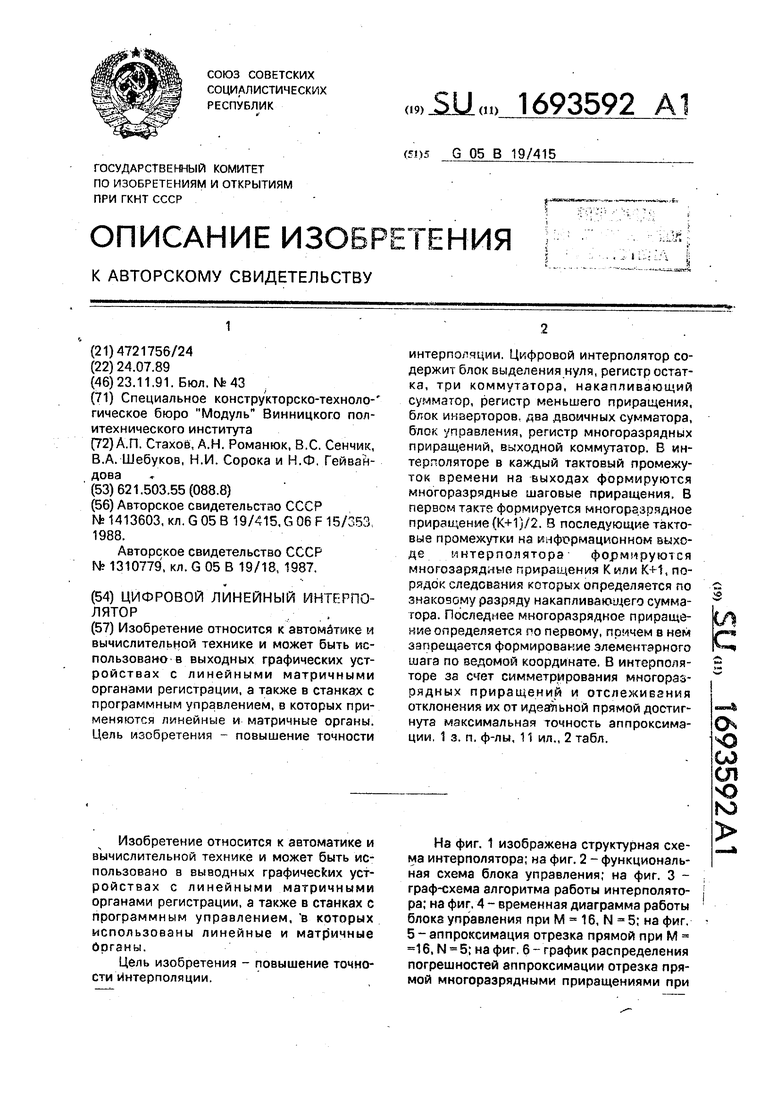

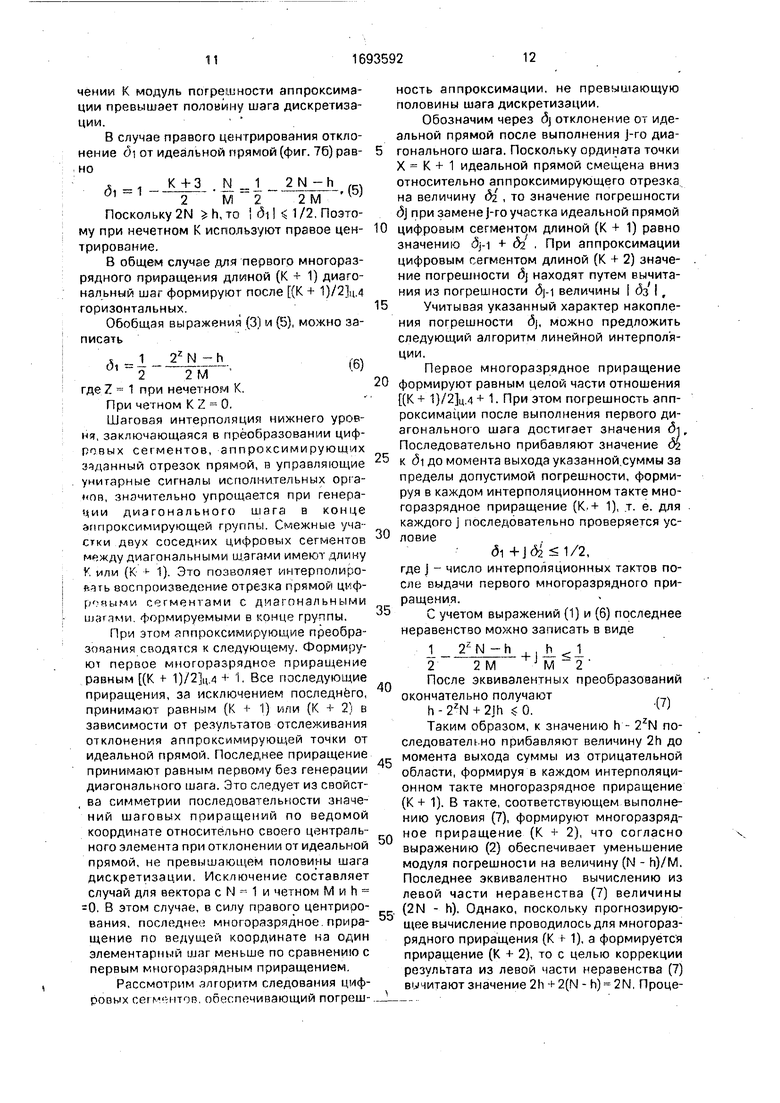

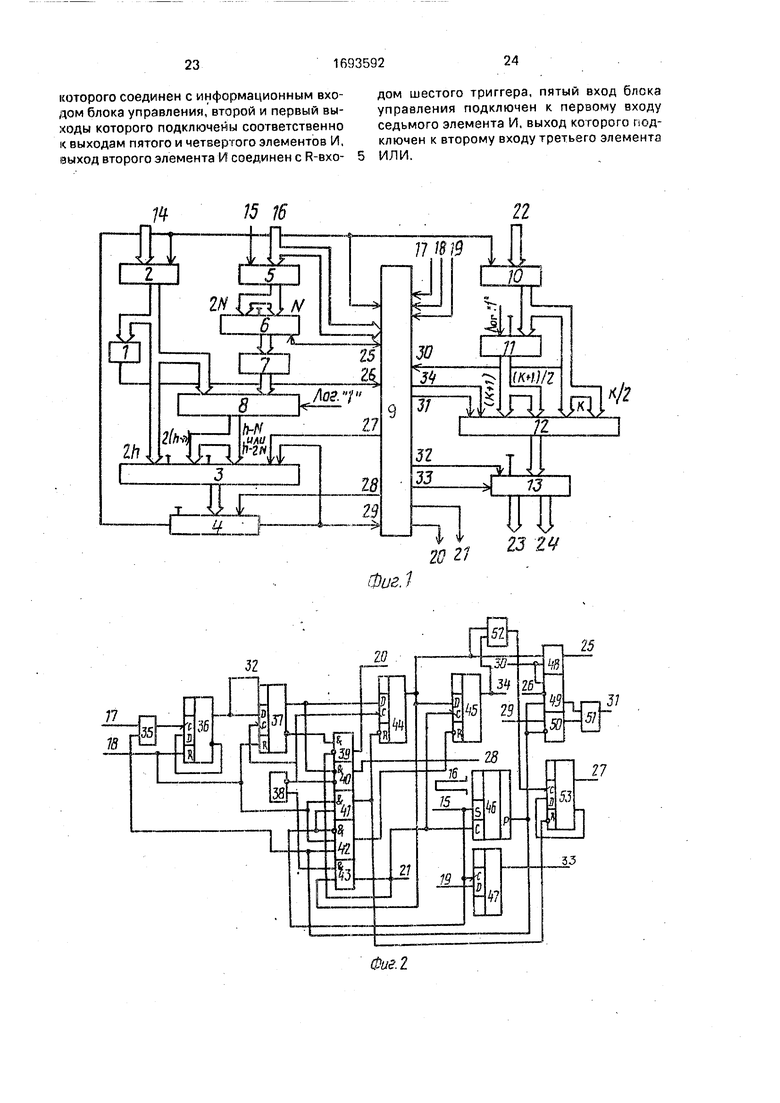

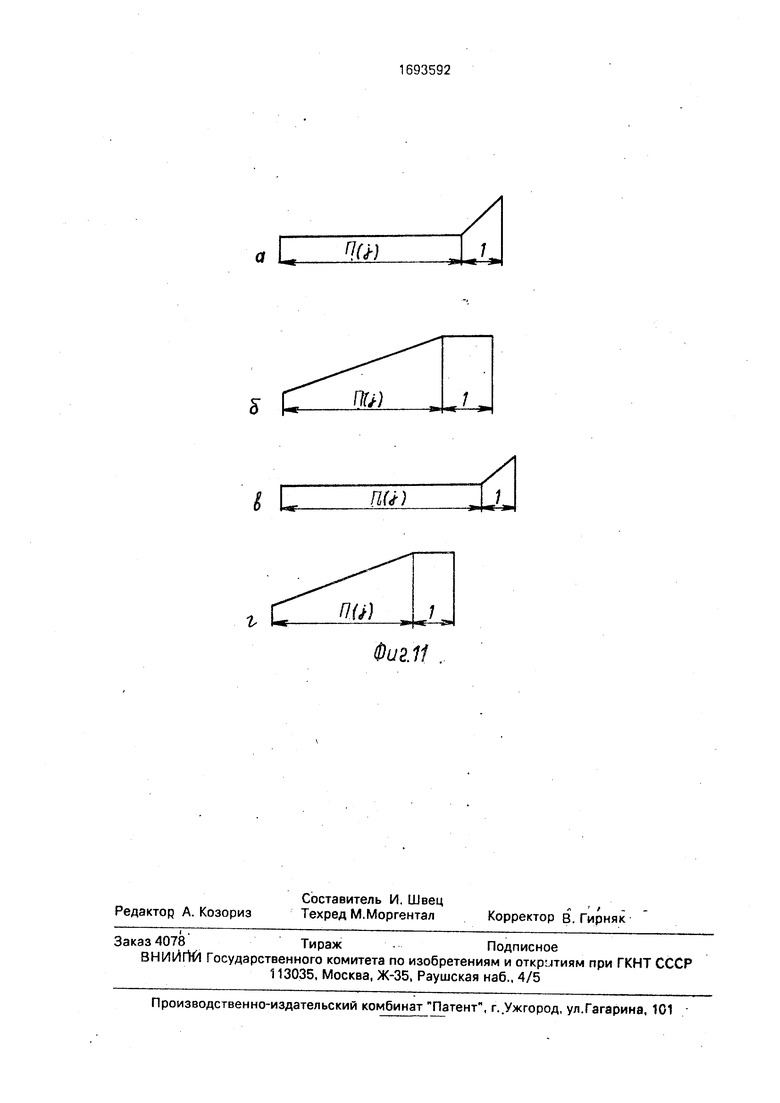

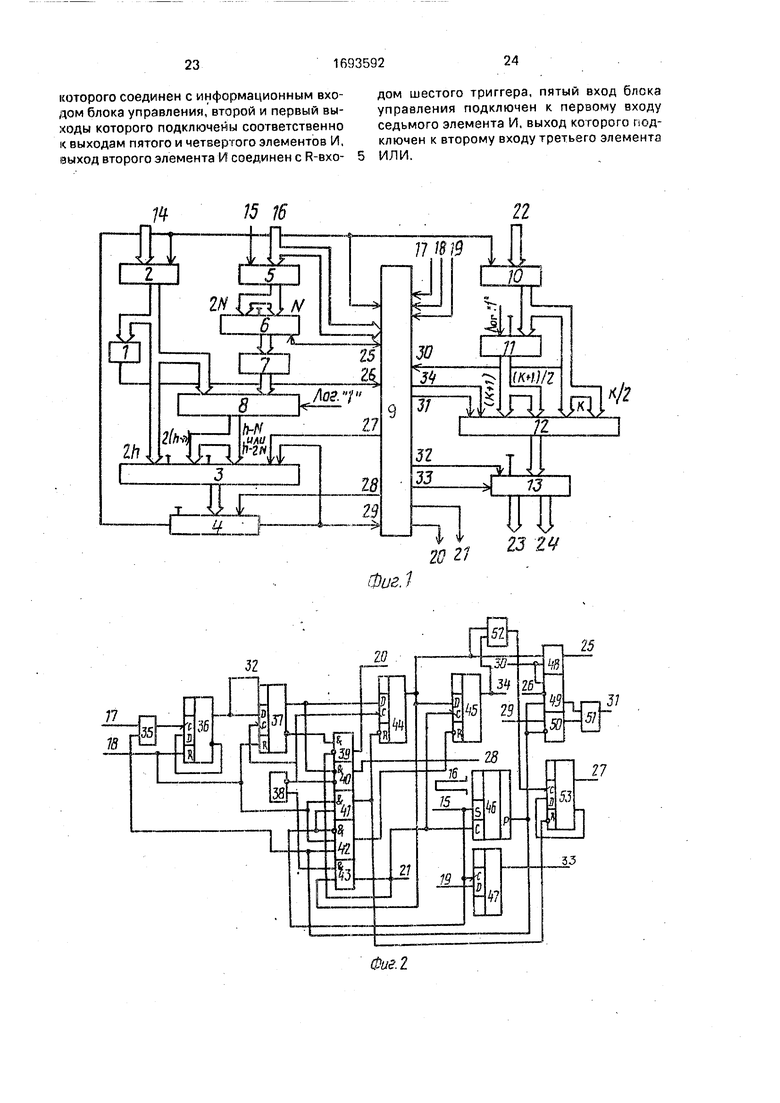

Цифровой линейный интерполятор фиг. 1) содержит блок 1 выделения нуля, регистр 2 остатка, первый коммутатор 3, накапливающий сумматор 4, регистр 5 меньшего приращения, второй коммутатор 10 б, блок 7 инверторов, первый двоичный сумматор 8, блок 9 управления, регистр S 0 мно- горазрядных приращений, второй двоичный сумматор 11, третий коммутатор 12, выходной коммутатор 13.15

Интерполятор имеет в код 14 остатка, вход 15 записи, вход 16 меньшего приращения, вход 17 Пуск, вхо,г-118 начальной установки, вход 19 признака, вход 22 цифрового сегмента, выход 20 конца интерполяции, 20 Стробирующий выход 21, первый информа- ционный выход 23 многоразрядных приращений, второй информационный выход 24 многоразрядных приращений. Позициями 25-34 обозначены входы и выходы блока 9. 25

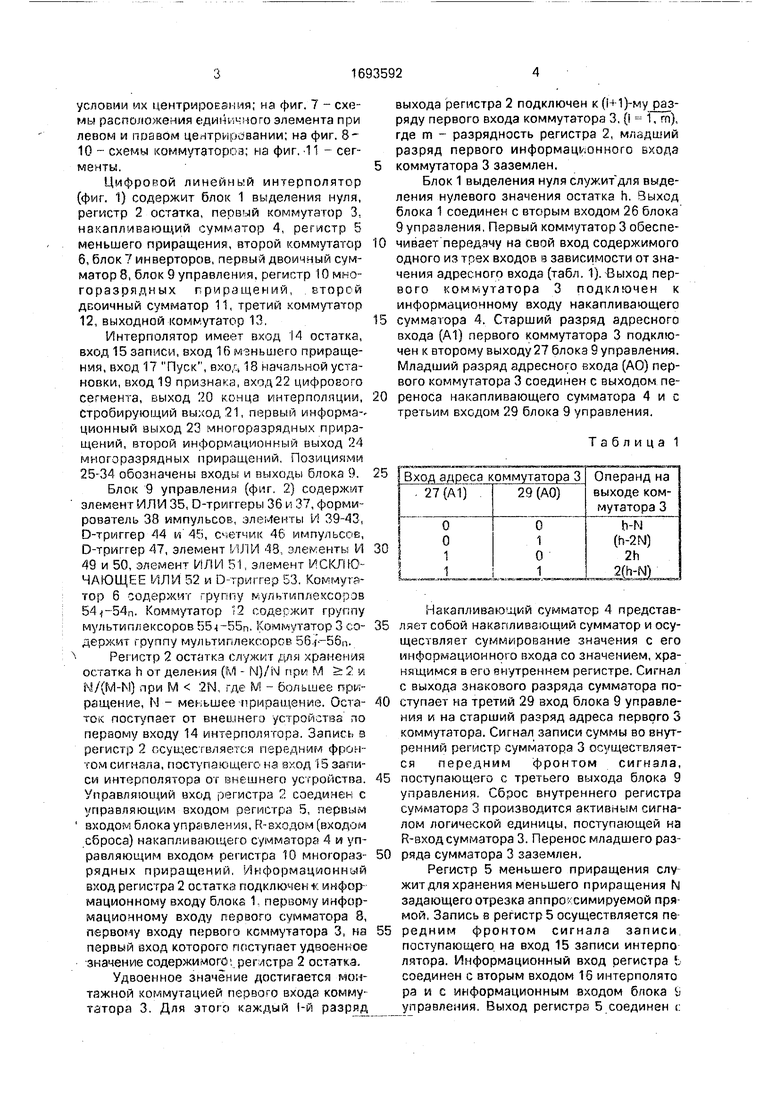

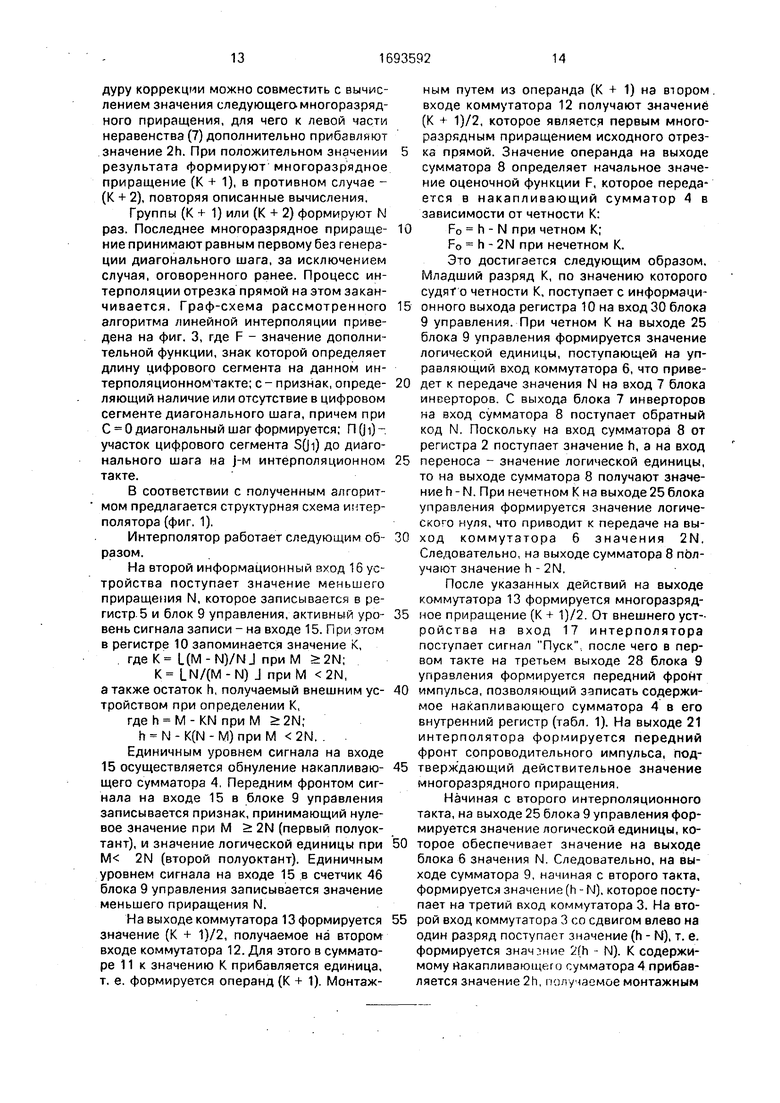

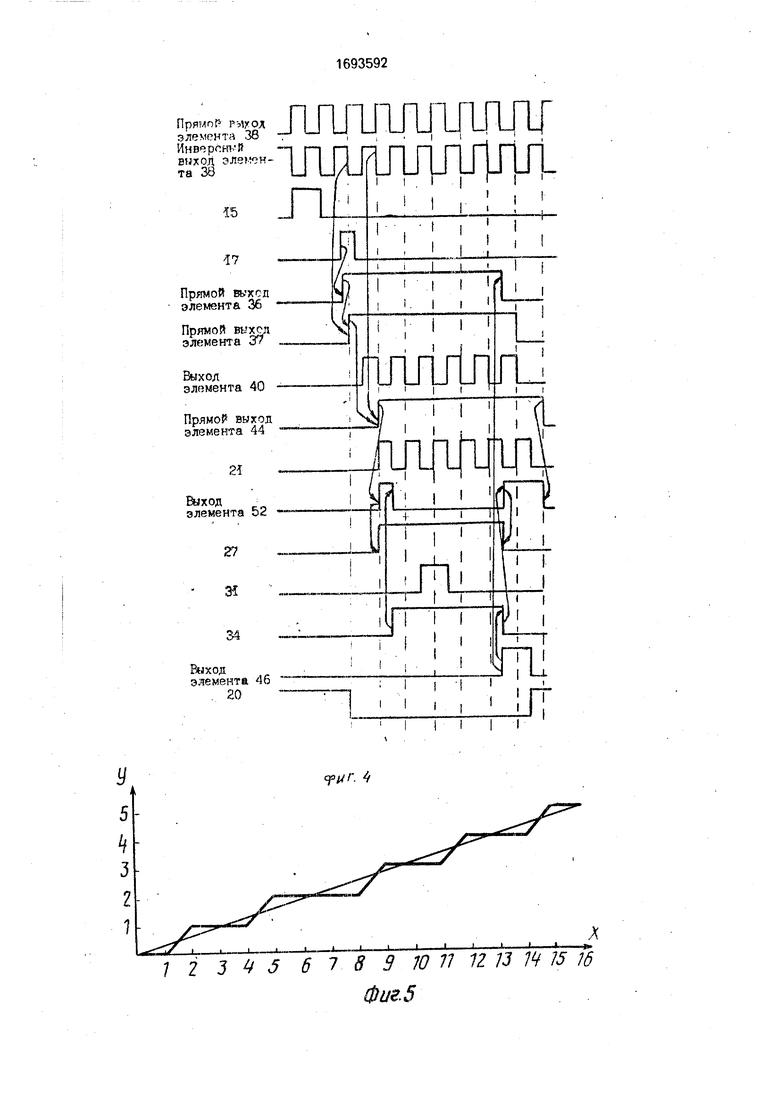

Блок 9 управления (фиг. 2) содержит элемент ИЛИ 35, D-триггеры 36 и 37, формирователь 38 импульсов., элементы И 39-43, D-триггер 44 и 45, сметчик 46 импульсов, D-триггер 47, элемент ПЛИ 48, элементы И 30 49 и 50, элемент ИЛИ 51, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 52 и D-григгер 53. Коммуга- тор 6 содержит группу мультиплексоров . Коммутатор 2 содержит группу мультиплексоров 554-55п. Коммутатор 3 со- 35 держит группу мультиплексоров 56.j--56n. Регистр 2 остатка служит для хранения остатка Ног деления (М - )/N при М 2 и N/(M-M) при М 2N, где М - большее приращение, N - меньшее приращение. Оста- 40 ток поступает от внешнего устройства по первому входу 14 интерполятора. Запись з регистр 2 осуществляется передним фронтом сигнала, поступающего на аход 15 записи интерполятора от внешнего устройства. 45 Управляющий вход регистра 2 соединен с управляющим входом регистра 5, первым входом блока управления, F -входом (входом сброса) накапливающего сумматора 4 и управляющим входом регистра 10 многораз- 50 рядных приращений, Информационный вход регистра 2 остатка подключен ; информационному входу блока 1. первому информационному входу первого сумматора 8, первому входу первого коммутатора 3, на 55 первый вход которого поступает удвоенное значение содержимого;.регистра 2 остатка. Удвоенное значение достигается монтажной коммутацией первого входа коммутатора 3. Для этого каждый 1-й разряд

выхода регистра 2 подключен к(Н1) ряду первого входа коммутатора 3, (i 1, m), где т - разрядность регистра 2, младший разряд первого информационного входа коммутатора 3 заземлен.

Блок 1 выделения нуля служит для выделения нулевого значения остатка h. выход блока 1 соединен с вторым входом 26 блока 9 управления, Первый коммутатор 3 обеспечивает передачу на свой вход содержимого одного из трех входов з зависимости от значения адресного входа (табл. 1). Выход первого коммутатора 3 подключен к информационному входу накапливающего сумматора 4. Старший разряд адресного входа (А1) первого коммутатора 3 подключен к второму выходу 27 блока 9 управления. Младший разряд адресного входа (АО) первого коммутатора 3 соединен с выходом переноса накапливающего сумматора 4 и с третьим входом 29 блока 9 управления.

Таблица 1

Накапливающий сумматор 4 представляет собой накапливающий сумматор и осуществляет суммирование значения с его информационного входа со значением, хранящимся в его внутреннем регистре. Сигнал с выхода знакового разряда сумматора поступает на третий 29 вход блока 9 управления и на старший разряд адреса первого 3 коммутатора. Сигнал записи суммы во внутренний регистр сумматора 3 осуществляется передним фронтом сигнала, поступающего с третьего выхода блока 9 управления. Сброс внутреннего регистра сумматора 3 производится активным сигналом логической единицы, поступающей на R-вход сумматора 3. Перенос младшего разряда сумматора 3 заземлен.

Регистр 5 меньшего приращения слу жит дня хранения меньшего приращения N задающего отрезка аппроксимируемой прямой, Запись в регистр 5 осуществляется передним фронтом сигнала записи поступающего на вход 15 записи интерпо лятора. Информационный вход регистра I соединен с вторым входом 16 интерполято ра и с информационным входом блока Ь управления. Выход регистра 5 соединен с

первым и вторым входами второго коммутатора, причем на первый вход коммутатора 6 поступает удвоенное значение регистра 5. Удвоенное значение достигается монтях-.- ной комутацией входа коммутаторов. Для этого каждый 1-й разряд выхода регистра 5 подключен к (1+1}-му разряду первого входа коммутатора 6, причем i 1, п, где п - разрядность выходной информационной шины регистра 5, младший разряд первого входа коммутатора 6 заземлен. При значении логического нуля на управляющем входе коммутатора б последний осуществляет передачу операнда со своего первого входа на выход. При значении логического нуля на управляющем входе коммутатора 6 последний осуществляет передачу операнда со своего первого входа на выход. При значений логической единицы на управляющем входе коммутатора 6 осуществляется передача операнда со своего второго входа на выход. Выход коммутатора б подключен к блоку 7 инверторов. Управляющий вход втог рого коммутатора б соединен с блоком 9 управления.

Сумматор 8 представляет собой комбинационный сумматор и осуществляет сложение операндов, поступающих из первый и второй суммирующие входы. Вход су.лма- тора 8 переноса подключен к выходу логической единицы.

Выход сумматора 8 соединен с вторым и третьим входами первого коммутатора 3, причем на его второй вход поступает удвоенное значение содержимого первого сумматора 8. Удвоенное значение достигается монтажной коммутацией входа коммутатора 3. Для этого каждый 1-й разряд выхода сумматора 8 подключают- к (1+1)-му разряду второго входа коммутатора 3, причем 1 1, п - 1, где п - разрядность информационной шины сумматора 8. Младший разряд второго информационного входа коммутатора 3 заземлен.

Блок 9 управления осуществляет управление операционными узлами интерполятора в соответствии с алгоритмом работы. По входу 17 интерполятора происходит запуск интерполятора передним фронтом сигнала. Вход интерполятора соединен с входом блока 9 управления. По входу 18 интерполятора уровнем логического нуля происходит начальная установка интерполятора. Единичное значение сигнала на четвертом входе 19 интерполятора указывает, что интерполирование будет происходить во втором полуоктзнте. Значение логического нуля на входе 19 указывает, что интерполирование производится в первом полуоктанте. Вход 19 соединен с входом блока 9

управления. Единичное значение младшего, разряда регистра 10, поступающее на вход 30 блока управления, указывает о нечетном значении К. На выходе 20 блока 9 управле- 5 ния формируется сигнал Конец интерполяции. Сигнал логического нуля на указанном выходе сигнализирует об интерполяции отрезка в заданный момент времени, т. е. о занятости интерполятора. При значении ло0 гической единицы на выходе 20 блока 9 управления интерполятор готов к приему исходного задания отрезка прямой. Выход 20 блока 9 управления соединен с выходом 20 конец интерполирования интерполятора.

5 Под воздействием сигнала, формируемого на стробирующем выходе 21 интерполятора, осуществляется стробирование выходных многоразрядных приращений. Стробирование происходит передним

0 фронтом сигнала. Выход 21 (стробирующий) интерпопятора соединен с выходом 21 блока 9 управления.

Регистр 10 многоразрядных приращений служит для хранения К, определяющего

5 число элементарных шаговых приращений по ведущей координате, приходящееся на единичное перемещение по ведомой координате. Информационный вход регистра 10 соединен с входом 22 интерполятора, а вы0 ход соединен с входом сумматора 11, с третьим и четвертым входами коммутатора 10, причем на четвертый вход коммутатора 12 поступает половина значения содержимого регистра 10, равного J.K/2J. Половина

5 значения содержимого регистра 10 достига-- ется монтажной коммутацией четвертого входа коммутатора 12. Для этого каждый 1-й разряд входа третьего коммутатора 12 подключают к (1+1)-му разряду регистра 10,

О причем I 1, п-1, где п - разрядность информационной шины регистра 10.

Двоичный сумматор 11 представляет собой комбинационный сумматор и осуществляет суммирование операнда, поступаю5 щего на его второй информационный вход со значением логической единицы, поступающей на его вход переноса. Информационный вход сумматора 11 заземлен. Половина значения содержимого сумматора 11 дости0 гается монтажной коммутацией второго входа коммутатора 12. Для этого каждый 1-й разряд входа коммутатора 12 подключают к (п-И)-му разряду сумматора 11, причем ,п-1, где n-разрядность информационной

5 шины. Коммутатор 12 обеспечивает передачу на свой выход значения содержимого из четырех его входов в зависимости от значения адресного входа (табл. 2). Выход коммутатора 12 подключен к входу выходного коммутатора. Старший рязряд адресного

эхода (А1) коммутатора 3 подключен к выходу 34 блока 9 управления, Младший разряд адресного входа (АО) кбммутатора З подключен к входу 31 блока 9 управления.

Таблица 2

Выходной коммутатор 13 обеспечивает передачу значений со своих входов на информационный выход 23 и информационный выход 24 интерполятора в зависимости от адресного входа.

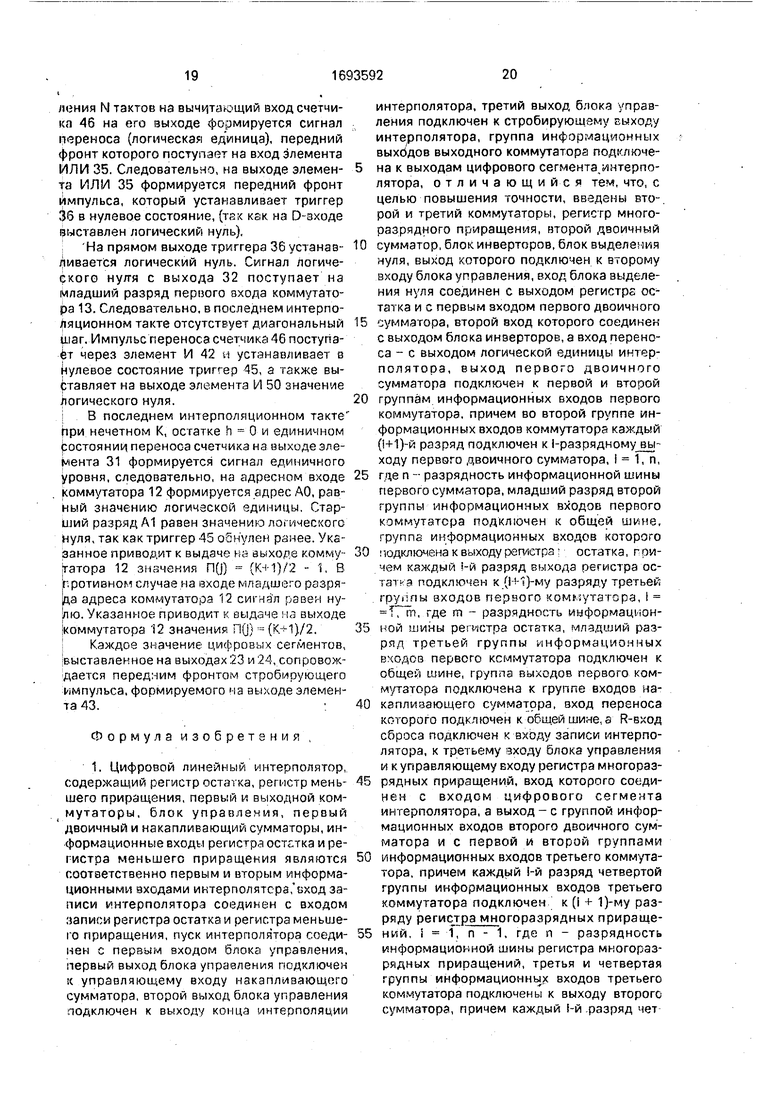

При г 0 (признак принадлежности отрезка прямой первому полуоктаиту) на выход 23 выдается значение многоразрядного приращения от коммутатора 12, а на выход 24 - значение логической единицы от входа коммутатора 13. Следовательно, внешним устройством будет воспринят цифровой сег- мент,показанный на фиг. 11а.

При г 1 (признак принадлежности отрезка прямой второму полуоктанту} на выход 24 выдается значение многоразрядного приращения от коммутатора 13. Внешним устройством будет воспринят цифровой сегмент, показанный на фиг. 116.

Таким образом, информация на выходе 24 определяет число диагональных шагов, а на выходе 23 - горизонтальных шагов.

Адресный вход коммутатора 13 соединен с выходом 33 блока 9 управления. Все разряды первого информационного входа заземлены за исключением младшего разряда, который подключен к выходу блока 9 управления.

Счетчик 46 предназначен для определения окончания процесса интерполяции. При задании отрезка прямой в него записывается значение меньшего приращения. Запись в счетчик 46 обеспечивается активным уровнем сигнала, поступающего с входа 15 записи интерполятора, соединенного с входом блока 9 управления.

Триггеры 36 и 37 предназначены для присинхронизированного канала-работы кйм- пульсной последовательности, вырабатываемой формирователем 38 импульсов после поступления сигнала Запуск интерполятора. Вход 17 блока 9 управления соединен с входом первого элемента ИЛИ 35, выход

которого подключен к управляющему С-вхо- ду D-триггера, выход которого - к выходу 32 блока 9 управления.

Сигнал Начальная установка служит

для обнуления первого 36, второго 37, третьего 44, четвертого 45, шестого 53 D-тригге- ров, Сигнал Начальная установка поступает на вход 18 блока 9 управления, на R-входы первого 36 и второго 37 D-триггеров и на первые входы третьего 41 и четвертого 42 элементов И.

Формирователь 38 импульсов служит для выработки импульсов, тактирующих работу блока 9 управления. Элемент И 39 совместно с инверсным выходом триггера 37 служит для выработки сигнала Конец интерполяции. Элемент И 40 служит для формирования требуемой импульсной последовательности для накапливающего

сумматора. Элемент И 43 служит для формирования требуемой импульсной последовательности стробирования значения на информационных выходах 23 и 24 интерполятора.

Триггеры 44, 45 и 53, элементы И 49 и 50, элемент ИЛИ 51 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 52 служат для формирования адреса для коммутаторов 3 и 12. Сигнал на прямом выходе триггера 45 соответствует

старшему разряду адреса коммутатора 12.

Сигнал на выходе элемента ИЛИ 51 соответствует младшему разряду адреса коммутатора 12. Сигнал на прямом выходе триггера 53 соответствует старшему разряду адреса коммутатора 3. Элемент ИЛИ 48 служит для управления зторого коммутатора 6.

Триггер 47 служит для хранения признака о принадлежности интерполируемого отрезка прямой и конкретному полуоктанту. Запись в триггеры 36,47 и 53 осуществляется передним фронтом сигнала, поступающего на их управляющие С-входы. Запись в триггеры 37, 44 и 45 осуществляется передним фронтом сигнала, поступающего на их управляющие С-входы.

В предлагаемом интерполяторе разрядность п регистров 5 и 10 совпадают. Максимальное значение К на единицу меньше

0 значения максимального большего приращения (при БПмакс 2 - 1, МПмакс 1,

Кмакс -г:- 2П - 2), а разрядность большего приращения равняется разрядности меньшего приращения (БПмакс 2 - 1; МПмаКс БП-1 2п-2 Кмакс).

Максимальное значение остатка не превышает половины большего приращения, а следовательно, разрядность m регистра 2 равна п -1, т. е. m п -1.

Для определения работы интерполятора синтезируют алгоритм аппроксимации отрезка прямой многоразрядными приращениями, обеспечивающий максимальную точность.

Пусть исходный отрезок прямой, заданный приращениями М и N, расположен в первом полуоктанте (М О, N О, М 2N) с началом в точке с координатами (0,0). Отрезки прямых с приращениями М, N, принадлежащие второму полуоктанту (М О, N О, М 2N), получают путем инвертирования значений интерполяционных шагов по ведомой координате при интерполировании отрезка с приращениями N, (М - N), принадлежащего первому полуоктанту. Изменение знаков приращений и замена координатных направлений позволяют получить отрезки с любым расположением и ориентацией по отношению к координатным осям. Указанные эквивалентные преобразования позволяют существенно упростить алгоритм интерполяции, сводя его только к аппроксимирующим действиям в первом полуоктанте.

Многоразрядное приращение (цифровой сегмент) длиной S определяет n S - 1 единичных шагов перемещений по ведущей координате и следующее за ними диагональное перемещение. Последнее соответствует одновременной выдаче единичных шаговых приращений по ведущей и ведомой координатам.

Исходный отрезок прямой может быть аппроксимирован цифровыми сегментами двух длин, отличающихся на единицу, значение которых находят вычисляя неравно- мерностные характеристики первого порядка, которые для первого полуоктанта принимают вид: п О,К (М - N).4. Параметр К определяет число элементарных шаговых приращений по ведущей координате, приходящихся на единичное перемещение по ведомой координате, а параметр - преобладание количества интерполяционных тактов, для которых шаговые приращения по ведомой координате не формируются. Для второго полуоктанта - п - 1,

При соответствующем выборе алгоритма следования цифровых сегментов только длиной (К+1) и (К+2) можно достичь погрешности аппроксимации, не превышающей шага дискретизации. Дальнейшее уменьшение модуля погрешности невозможно, поскольку параметр К находят путем выделения целой части отношения (М - N)/N при М 2N или N/(M - N) при М 2N и

0

дробная часть указанных отношений может приближаться к единице.

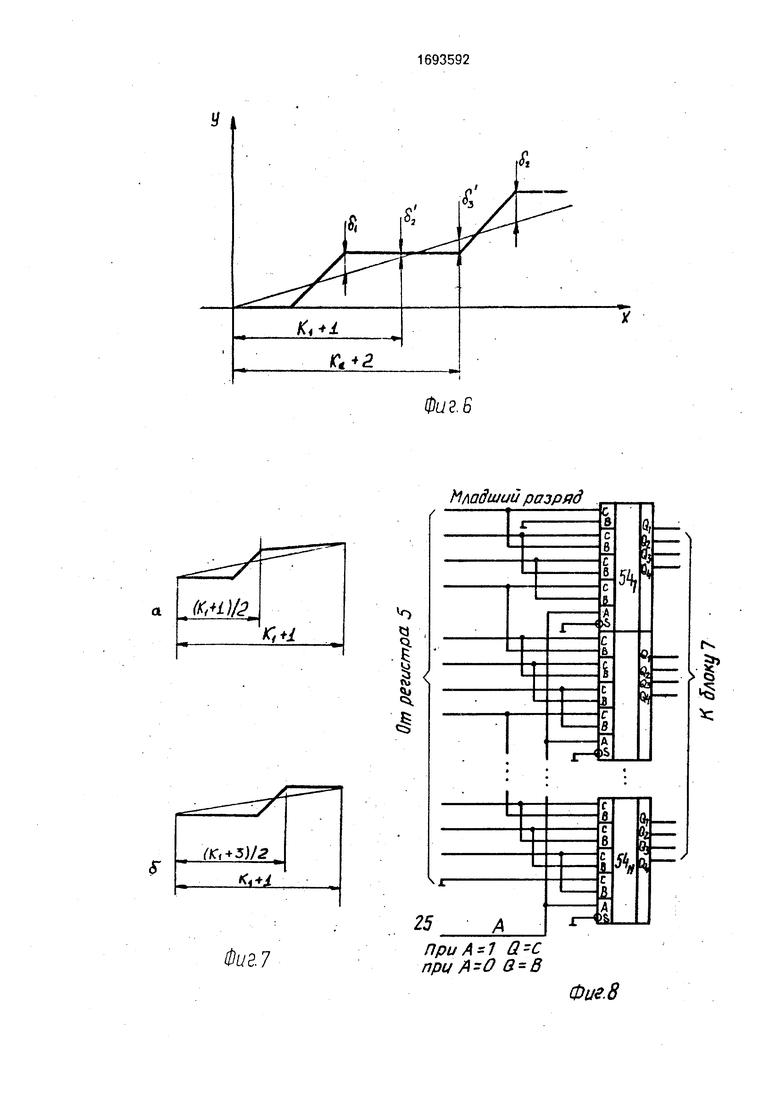

Известно, что уменьшения погрешности аппроксимации можно достичь при центрировании (симметричном размещении единицы среди нулей) в многоразрядном приращении (фиг. 6).

Отклонение (5/ от идеальной прямой в точке (К + 1) при отработке первого многоразрядного приращения (К + 1) равно

- -й( +

5

М

N

M-N Ь.-ч h м + 1) мN

N

(D

где h - остаток от деления (М - N) на N,

При отработке многоразрядного прира- 20 щения (К ч- 2) отклонение дз от идеальной прямой в точке (К + 2) составляет

25

-1-йск+2 + -Ј-Jl И

М М

h -N

М Поскольку

1

1

ii ,

К+2 М К + Г

(2) знаки

0 отклонений 62 и дз от идеальной прямой

противоположные.

Значение погрешности аппроксимации

бчзависит от четности или нечетности К. При

четном К 5

1Л . JL±2.

М2

l+rl-N..

Г v О М

К + 1

М

JN 2М

J 2

N-h 2М

(3)

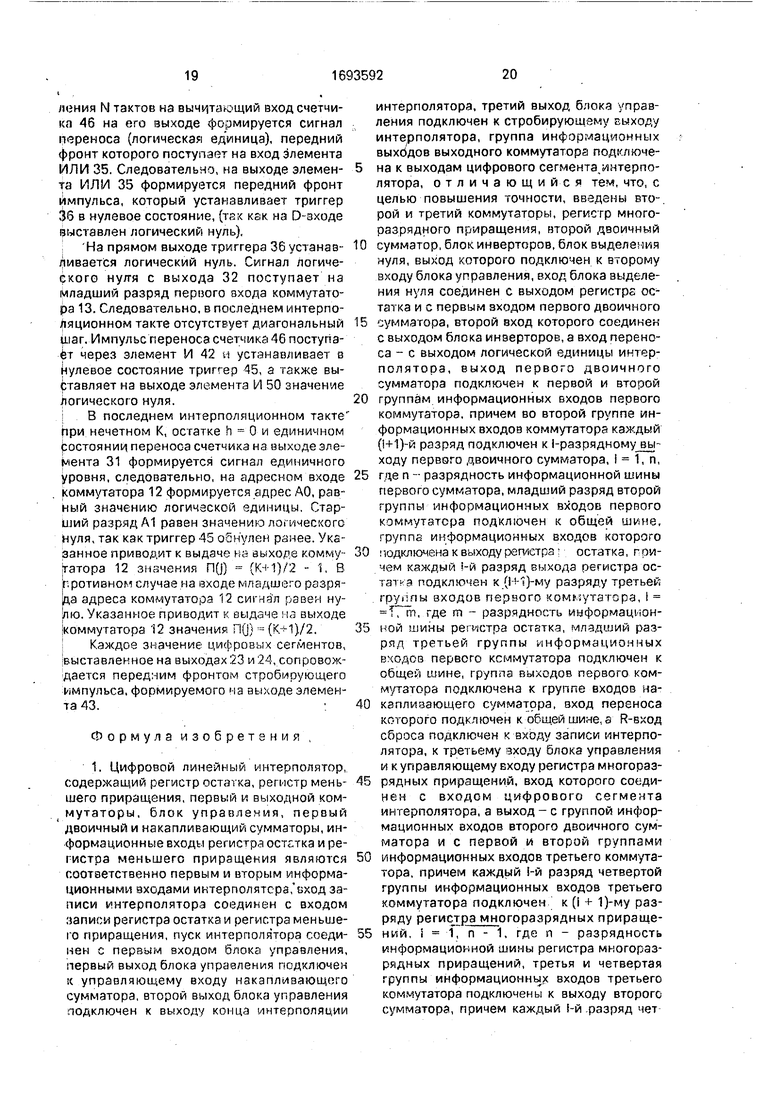

При нечетном К возможны два варианта центрирования многоразрядного приращения. При левом центрировании диагональ- ный шаг формируется после (К + 1)/2 - 1 горизонтальных, а при правом - после (К + 3)/2 - 1 горизонтальных шагов (фиг. 7).

Отклонение д от идеальной прямой при левом центрировании (фиг. 7а) опреде- ляется согласно выражению

. К + 1 2

1 -Н/М

(4)

Из последнего выражения следует, что при левом центрировании и нечетном значении К модуль погрешности аппроксимации превышает половину шага дискретизации.

В случае правого центрирования отклонение д от идеальной прямой (фиг. 76) равно

К +3 . N J М

di l

2N-h ,,

-Тм (5)

2 М 2

Поскольку 2N h,TO (3i I 1/2, Поэтому при нечетном К используют правое центрирование.

В общем случае для первого многоразрядного приращения длиной (К + 1) диагональный шаг формируют после (К + 1).4 горизонтальных.

Обобщая выражения (3) и (5), можно записать

5,1

01 2

2ZN -h

(6)

2 М где 7. - 1 при нечетном К. При четном К Z 0.

Шаговая интерполяция нижнего уровня, заключающаяся в преобразовании цифровых сегментов, аппроксимирующих заданный отрезок прямой, в управляющие унитарные сигналы исполнительных органов, значительно упрощается при генерации диагонального шага в конце Аппроксимирующей группы. Смежные участки двух соседних цифровых сегментов между диагональными шагами имеют длину У, или (К - 1). Это позволяет интерполиро- ячть воспроизведение отрезка прямой циф- р -чыми сегментами с диагональными шагами, формируемыми в конце группы.

При этом аппроксимирующие преобразования сводятся к следующему. Формируют первое многоразрядное приращение равным (К + 1).4 + 1. Все последующие приращения, за исключением последнего, принимают равным (К + 1) или (К + 2) в зависимости от результатов отслеживания отклонения аппроксимирующей точки от идеальной прямой. Последнее приращение принимают равным первому без генерации диагонального шага. Это следует из свойства симметрии последовательности значений шаговых приращений по ведомой координате относительно своего центрального элемента при отклонении от идеальной прямой, не превышающем половины шага дискретизации. Исключение составляет случай для вектора с N -- 1 и четном М и h 0. В этом случае, в сипу правого центрирования, последнее многоразрядное приращение по ведущей координате на один элементарный шаг меньше по сравнению с первым многоразрядным приращением.

Рассмотрим алгоритм следования цифровых сегментов, обеспечивающий погреш

ность аппроксимации, не превышающую половины шага дискретизации.

Обозначим через dj отклонение от идеальной прямой после выполнения j-ro диа5 тонального шага. Поскольку ордината точки X К + 1 идеальной прямой смещена вниз относительно аппроксимирующего отрезка на величину д{ , то значение погрешности 5) при замене j-ro участка идеальной прямой

10 цифровым сегментом длиной (К + 1) равно значению 5j-i + 62 , При аппроксимации цифровым сегментом длиной (К + 2) значение погрешности dj находят путем вычитания из погрешности 5j-i величины I бз I,

15 Учитывая указанный характер накопления погрешности д, можно предложить следующий алгоритм линейной интерполяции.

Первое многоразрядное приращение

20 формируют равным целой части отношения (К + .4 + 1. При этом погрешность аппроксимации после выполнения первого диагонального шага достигает значения 5i. Последовательно прибавляют значение $

25 к 5i до момента выхода указанной.суммы за пределы допустимой погрешности, формируя в каждом интерполяционном такте многоразрядное приращение (К.+ 1), т. е. для каждого последовательно проверяется ус30 ловие

di+jd2 l/2,

где j - число интерполяционных тактов после выдачи первого многоразрядного приращения.

35

учетом выражений (1) и (6) последнее неравенство можно записать в виде

1 2Z N - h

1

I

22 MJ М 2

n После эквивалентных преобразований окончательно получают, ,

h-2zN + 2jh $0. (

Таким образом, к значению h - 2ZN последовательно прибавляют величину 2h до

р. момента выхода суммы из отрицательной области, формируя в каждом интерполяционном такте многоразрядное приращение (К + 1). В такте, соответствующем выполнению условия (7), формируют многоразрядQ ное приращение (К + 2), что согласно выражению (2) обеспечивает уменьшение модуля погрешности на величину (N - h)/M. Последнее эквивалентно вычислению из левой части неравенства (7) величины

., (2N - h). Однако, поскольку прогнозирующее вычисление проводилось для многоразрядного приращения (К t- 1), а формируется приращение (К + 2), то с целью коррекции результата из левой части неравенства (7) вычитают значение 2h + 2(N- h) 2N, Процедуру коррекции можно совместить с вычислением значения следующего-многоразрядного приращения, для чего к левой части неравенства (7) дополнительно прибавляют значение 2h. При положительном значении результата формируют многоразрядное приращение (К + 1), в противном случае - (К + 2), повторяя описанные вычисления.

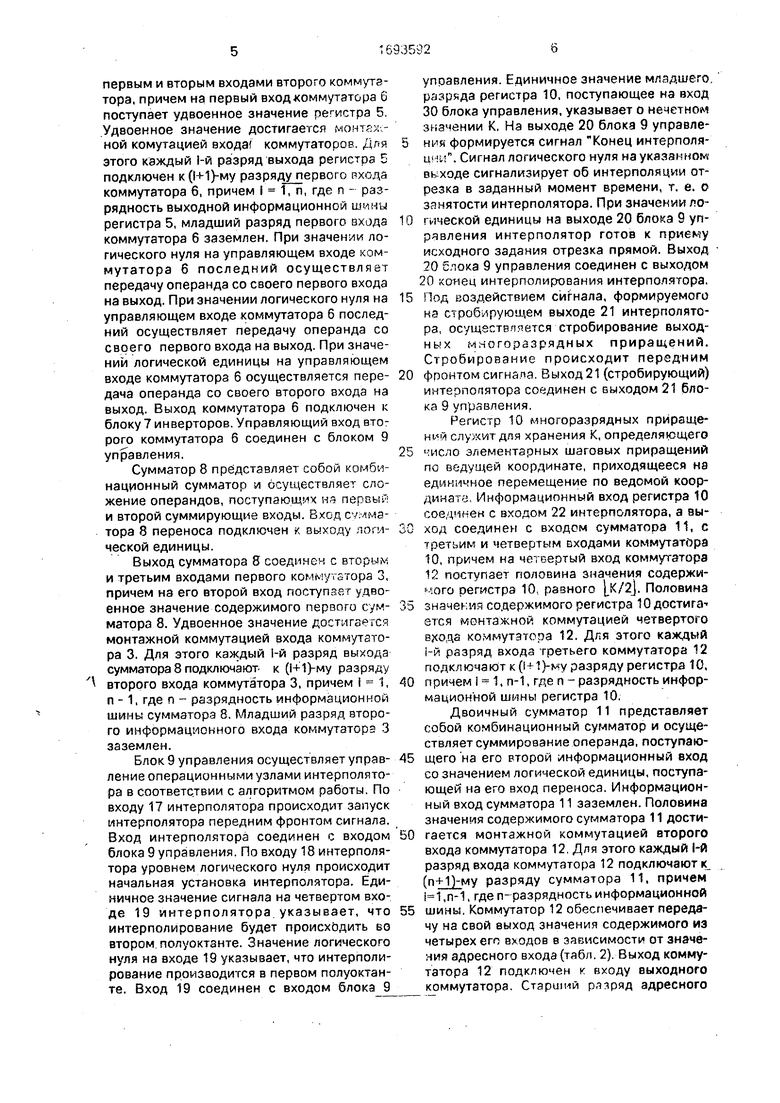

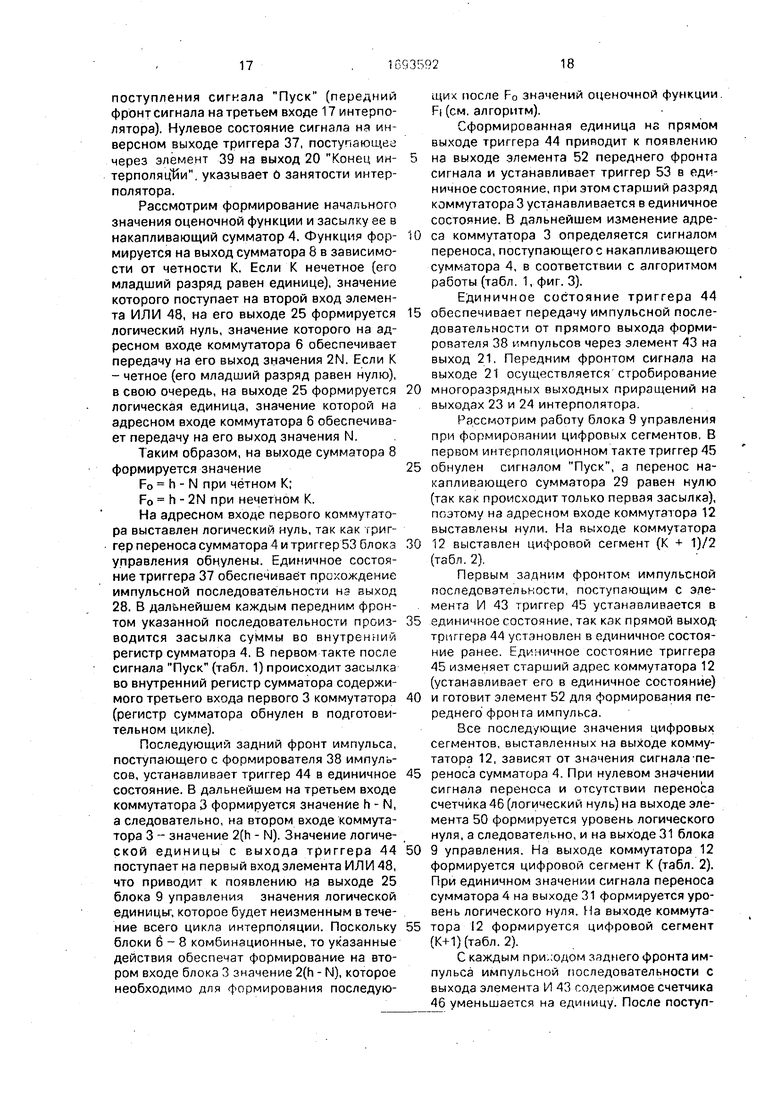

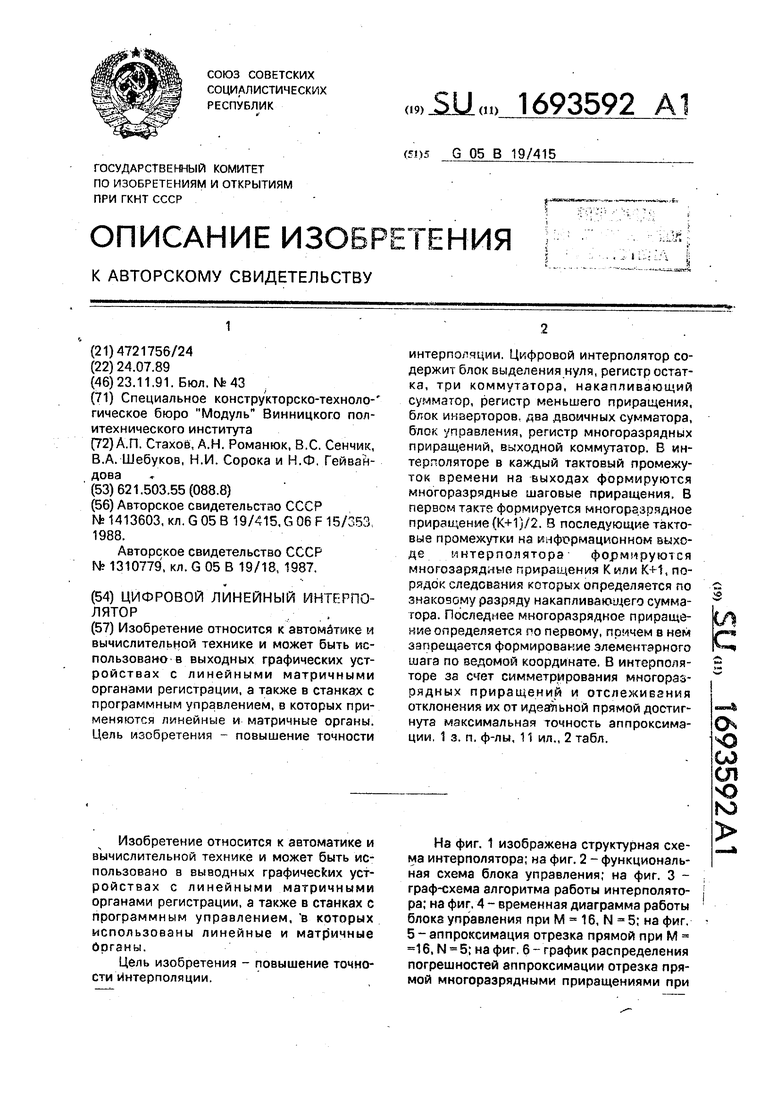

Группы (К + 1) или (К + 2) формируют N раз. Последнее многоразрядное приращение принимают равным первому без генерации диагонального шага, за исключением случая, оговоренного ранее. Процесс интерполяции отрезка прямой на этом заканчивается. Граф-схема рассмотренного алгоритма линейной интерполяции приведена на фиг. 3, где F - значение дополнительной функции, знак которой определяет длину цифрового сегмента на данном ин- терполяционномчтакте; с- признак, определяющий наличие или отсутствие в цифровом сегменте диагонального шага, причем при С 0 диагональный шаг формируется; П (j i) - участок цифрового сегмента S(Ji) до диагонального шага на j-м интерполяционном такте.

В соответствии с полученным алгоритмом предлагается структурная схема иятер- полятора (фиг. 1).

Интерполятор работает следующим образом.

На второй информационный аход 16 устройства поступает значение меньшего приращения N, которое записывается в регистр 5 и блок 9 управления, активный уровень сигнала записи - на входе 15. При этом в регистре 10 запоминается значение К,

где К L(M-N)/NJ приМ 2N; К LN/(M-N) J приМ 2N, а также остаток h, получаемый внешним устройством при определении К,

где h M- KN при М 2М; h N - K(N - М) при М 2N.

Единичным уровнем сигнала на входе 15 осуществляется обнуление накапливающего сумматора 4, Передним фронтом сигнала на входе 15 в блоке 9 управления записывается признак, принимающий нулевое значение при М 2N (первый полуоктант), и значение логической единицы при М 2N (второй полуоктант). Единичным уровнем сигнала на входе 15 в счетчик 46 блока 9 управления записывается значение меньшего приращения N.

На выходе коммутатора 13 формируется значение (К + 1)/2, получаемое на втором входе коммутатора 12. Для этого в сумматоре 11 к значению К прибавляется единица, т, е. формируется операнд (К + 1). Монтажным путем из операнда (К + 1) на втором входе коммутатора 12 получают значение (К + 1)/2, которое является первым многоразрядным приращением исходного отрез- 5 кз прямой. Значение операнда на выходе сумматора 8 определяет начальное значение оценочной функции F, которое переда ется в накапливающий сумматор 4 в зависимости от четности К:

0 Fo h -N при четном К;

Fo h - 2N при нечетном К. Это достигается следующим образом. Младший разряд К, по значению которого судят о четности К, поступает с информаци5 онного выхода регистра 10 на вход 30 блока 9 управления. При четном К на выходе 25 блока 9 управления формируется значение логической единицы, поступающей на управляющий вход коммутатора 6, что приве0 дет к передаче значения N на вход 7 блока инверторов. С выхода блока 7 инверторов на вход сумматора 8 поступает обратный код N. Поскольку на вход сумматора 8 от регистра 2 поступает значение h, а на вход

5 переноса - значение логической единицы, то на выходе сумматора 8 получают значение h - N. При нечетном К на выходе 25 блока управления формируется значение логического нуля, что приводит к передаче на вы0 ход коммутатора 6 значения 2N. Следовательно, на выходе сумматора 8 получают значение h-2N.

После указанных действий на выходе коммутатора 13 формируется многоразряд5 ное приращение (К + 1)/2. От внешнего устройства на вход 17 интерполятора поступает сигнал Пуск после чего в первом такте на третьем выходе 28 блока 9 управления формируется передний фронт

0 импульса, позволяющий ззписать содержимое накапливающего сумматора 4 в его внутренний регистр (табл. 1). На выходе 21 интерполятора формируется передний фронт сопроводительного импульса, под5 тверж дающий действительное значение многоразрядного приращения.

Начиная с второго интерполяционного такта, на выходе 25 блока 9 управления формируется значение логической единицы, ко0 торое обеспечивает значение на выходе блока 6 значения N. Следовательно, на выходе сумматора 9, начиная с второго такта, формируется значение (h - N), которое поступает на третий вход коммутатора 3. На вто5 рой вход коммутатора 3 со сдвигом влево на один разряд поступает значение (h - N), т. е. формируется значение 2(h - N). К содержимому Накапливающего сумматора 4 прибавляется значение 2h, полу аемое монтажным

путем на первом входе первого коммутатора 3, т. е. формируется значение Fi Fo + 2h.

Наличие единичного сигнала на выходе знакового разряда накапливающего сумматора 4 указывает на положительное значение оценочной функции, в противном случае оценочная функция принимает отрицательное значение.

По знаку оценочной функции FI на выход коммутатора 12 передается одно из значений П(2) К; П(2) К + 1, Отрицательному значению оценочной функции Fi соответствует приращение П(2) К, а положительному -П(2) К+1.

В дальнейшем оценочная функция вычисляется в соответствии со следующими соотношениями:

Рн-1 FH-2H при Fi 0; FI+I Fi - 2(N - h) при Fi 0, При FI 0 на выходе коммутатора 12 формируется операнд П К, а при FI 0 - П г К+ 1.

Операнды 2h, 2(N - h) суммируются соответственно на первом и втором входах коммутатора 3, а операнды П К и П К+1 - на третьем и первом входах коммутатора 12, Значения оценочной функции определяются в накопительном сумматоре 4.

С каждым интерполяционным ТРКТОМ содержимое счетчика 46 блока управления уменьшается на единицу. При достижении им нулевого состояния на его выходе переноса формируется сигнал единичного уровня, указывающий о необходимости, выдачи последнего многоразрядного приращения. Согласно алгоритму работы последнее многоразрядное приращение может принимав одно из двух значений:

П(М + 1) - П(1)- I при h О, К - нечетное; П(Ы + 1) П(1) - в остальных случаях.

При h 0 на выходе элемента ИЛИ I формируется сигнал нулевого1 уровня, который поступает на вход 26 блока 9 управления. При единичном уровне сигнала на входе 30 блока 9 управления на входах 34 л 31 формируются сигналы соответственно нулевого и единичного уровней, что, в свою очередь, приводит к передаче на выход коммутатора 12 значения I.K/2J, т. е, П(1)- 1,

Во всех остальных случаях в последнем интерполяционном такте на входам 34 и 31 блока 9 управления формируются нулевые значения, что обеспечивает передачу на выход коммутатора 12 значения ()/2, т. е,

П(1).

В последнем интерполяционном такте на выходе 32 формируется сигнал нулевого уровня, запрещающий формирование диагонального шага при М 2N или горизонтального шага при М N.

Выдача шагов, приращений на ьыход коммутатора осуществляется в соответствии со значением признака, определяющего соответствие генерируемого отрезка первому или второму полуоктанту.

При г 0 (признак принадлежности отрезка прямой первому полуоктанту) на вы0 ход 23 выдается знамение многоразрядного приращения от коммутатора 12, а на выход 24 - значение логической единицы от первого входа коммутатора 13.

Следовательно, внешним устройством

5 воспринимается цифровой сегмент, показанный на фиг. 11 в.

При г 1 (признак принадлежности отрезка прямой второму полуоктанту) на выход 24 выставляется значение многораз0 рядного приращения от коммутатора 12, а на выход 23 - значение логической единицы с первого входа коммутатора 13. Внешним устройством воспринимается цифровой сегмент, показанный на фиг. 11г.

5 Таким образом, информация на выходе 24.определяет число диагональных шагов, а на выходе 23 - горизонтальных шагов. Граф- схема алгоритма работы интерполятора приведена на фиг. 3.

0 Рассмотрим работу блока 9 управления. Для избежания гонок и состязаний при синтезе блока использован принцип единой зр осиной организации.

В цикле подготовкч в триггер 47 пере5 дним ф ронтом сигнала на входе 15 записи интерполятора запоминается признак, оп- редепяющим принадлежность интерполиру- емого отрезка первому или второму полуоктанту, г 0 - соответствует принэд0 лежности отрезка прямой первому полуоктанту, а г 1 - второму,

Единичное значение сигнала на входе 15 интерполятора производит запись меньшего приращения N в счетчик 45, а также

5 устанавливает в нулевое состояние триггеры 44, 45 и 53.

Передним фронтом сигнала Пуск на входе 17 интерполятора разрешается работа интерполятора. В этом случае устанавли0 вается в единичное состояние триггер 36. При появлении после этого заднего фронта сигнала на выходе формирователя 38 импульсов триггер 37 устанавливается в единичное состояние, что разрешает

5 прохождение импульсной последовательности or формирователя 38 на выход элемента 40. Указанные действия по запуску интерполятора обеспечивают присинхрони- зированную его работу к импульсной последовательности от формирователя 38 после

поступления сигнала Пуск (передний фронт сигнала на третьем входе 17 интерполятора). Нулевое состояние сигнала на инверсном выходе триггера 37, поступающее через элемент 39 на выход 20 Конец интерполяции, указывает о занятости интерполятора.

Рассмотрим формирование начального значения оценочной функции и засылку ее в накапливающий сумматор 4. Функция формируется на выход сумматора 8 в зависимости от четности К. Если К нечетное (его младший разряд равен единице), значение которого поступает на второй вход элемента ИЛИ 48, на его выходе 25 формируется логический нуль, значение которого на адресном входе коммутатора 6 обеспечивает передачу на его выход значения 2N. Если К - четное (его младший разряд равен нулю), в свою очередь, на выходе 25 формируется логическая единица, значение которой на адресном входе коммутатора 6 обеспечивает передачу на его выход значения N.

Таким образом, на выходе сумматора 8 формируется значение

Fo h - N при четном К;

Fo h - 2N при нечетном К.

На адресном входе первого коммутатора выставлен логический нуль, так как триггер переноса сумматора 4 и триггер 53 блока управления обнулены. Единичное состояние триггера 37 обеспечивает прохождение импульсной последовательности на выход 28. В дальнейшем каждым передним фронтом указанной последовательности производится засылка суммы во внутренний регистр сумматора 4. В первом такте после сигнала Пуск (табл. 1) происходит засылка во внутренний регистр сумматора содержимого третьего входа первого 3 коммутатора (регистр сумматора обнулен в подготовительном цикле).

Последующий задний фронт импульса, поступающего с формирователя 38 импульсов, устанавливает триггер 44 в единичное состояние. В дальнейшем на третьем входе коммутатора 3 формируется значение h - N, а следовательно, на втором входе коммутатора 3 - значение 2(h - N). Значение логиче- ской единицы с выхода триггера 44 поступает на первый вход элемента ИЛИ 48, что приводит к появлению на выходе 25 блока 9 управления значения логической единицы, которое будет неизменным в течение всего цикла интерполяции. Поскольку блоки 6-8 комбинационные, то указанные действия обеспечат формирование на втором входе блока 3 значение 2(h - N), которое необходимо для формирования последующих после Fo значений оценочной функции FJ (см. алгоритм).

Сформированная единица нз прямом выходе триггера 44 приводит к появлению 5 на выходе элемента 52 переднего фронта сигнала и устанавливает триггер 53 в единичное состояние, при этом старший разряд коммутатора 3 устанавливается в единичное состояние. В дальнейшем изменение адреса коммутатора 3 определяется сигналом переноса, поступающего с накапливающего сумматора 4, в соответствии с алгоритмом работы (табл. 1, фиг. 3).

Единичное состояние триггера 44

5 обеспечивает передачу импульсной последовательности от прямого выхода формирователя 38 импульсов через элемент 43 на выход 21. Передним фронтом сигнала на выходе 21 осуществляется стробирование

0 многоразрядных выходных приращений на выходах 23 и 24 интерполятора.

Рассмотрим работу блока 9 управления при формировании цифровых сегментов, В первом интерполяционном такте триггер 45

5 обнулен сигналом Пуск, а перенос накапливающего сумматора 29 равен нулю (так как происходит только первая засылка), поэтому на адресном входе коммутатора 12 выставлены нули. На выходе коммутатора

0 12 выставлен цифровой сегмент (К + 1)/2 (табл. 2)

Первым задним фронтом импульсной последовательности, поступающим с элемента I/I 43 триггер 45 устанавливается в

5 единичное состояние, так как прямой выход триггера 44 установлен в единичное состояние ранее. Единичное состояние триггера

45изменяет старший адрес коммутатора 12 (устанавливает его в единичное состояние)

0 и готовит элемент 52 для формирования переднего фронта импульса.

Все последующие значения цифровых сегментов, выставленных на выходе коммутатора 12, зависят от значения сигнала-пе5 реноса сумматора 4. При нулевом значении сигнала переноса и отсутствии переноса счетчика 46 (логический нуль) на выходе элемента 50 формируется уровень логического нуля, а следовательно, и на выходе 31 блока

0 9 управления. На выходе коммутатора 12 формируется цифровой сегмент К (табл. 2). При единичном значении сигнала переноса сумматора 4 на выходе 31 формируется уровень логического нуля. Нз выходе коммута5 тора 12 формируется цифровой сегмент (К+1) (табл. 2).

С каждым приводом заднего фронта импульса импульсной последовательности с выхода элемента И 43 содержимое счетчика

46уменьшается на единицу. После поступления N тактов на вычитающий вход счетчика 46 на его выходе формируется сигнал переноса (логическая единица), передний фронт которого поступает на вход элемента ИЛИ 35. Следовательно, на выходе элемен- та ИЛИ 35 формируется передний фронт импульса, который устанавливает триггер 36 в нулевое состояние, (так как на D-зходе выставлен логический нуль),

На прямом выходе триггера 36 устанав- ливается логический нуль. Сигнал логического нуяя с выхода 32 поступает на младший разряд первого входа коммутатора 13. Следовательно, в последнем интерполяционном такте отсутствует диагональный шаг. Импульс переноса счетчика 46 поступает через элемент И 42 и устанавливает в нулевое состояние триггер 45, а также выставляет на выходе элемента И 50 значение логического нуля.

В последнем интерполяционном такте при нечетном К, остатке h 0 и единичном состоянии переноса счетчика на выходе элемента 31 формируется сигнал единичного уровня, следовательно, на адресном входе коммутатора 12 формируется адрес АО, равный значению логической единицы. Старший разряд А1 равен значению логического нуля, так как триггер 45 обнулен ранее. Указанное приводит к выдаче ни выходе комму-- татора 12 значения ПО) (К+1)/2 - 1, В противном случае на входе младшего разряда адреса коммутатора 12 сигнал равен нулю. Указанное приводит к выдаче на выходе коммутатора 12 значения П(|) (,

Каждое значение цифровых сегментов, выставленное на выходах 23 и 24, сопровождается передним фронтом стробирующего импульса, формируемого ча выходе элемента 43.

Формула изобретения ,

1. Цифровой линейный интерполятор, содержащий регистр остатка, регистр мень- шего приращения, первый и выходной коммутаторы, блок управления, первый двоичный и накапливающий сумматоры, информационные входы регистра остатка и регистра меньшего приращения являются соответственно первым и вторым информационными входами интерполятора, «ход записи интерполятора соединен с входом записи регистра остатка и регистра меньшего приращения, пуск интерполятора соеди- йен с первым входом блока управления, первый выход блока управления подключен к управляющему входу накапливающего сумматора, второй выход блока управления подключен к выходу конца интерполяции

интерполятора, третий выход блока управления подключен к стробирующему выходу интерполятора, группа информационных выхбдов выходного коммутатора подключена к выходам цифрового сегмента, мнтерпо- лятора, отличающийся тем, что, с целью повышения точности, введены вто. рой и третий коммутаторы, регистр многоразрядного приращения, второй двоичный сумматор, блок инверторов, блок выделения нуля, выход которого подключен к второму входу блока управления, вход блока выделения нуля соединен с выходом регистра остатка и с первым входом первого двоичного сумматора, второй вход которого соединен- с выходом блока инверторов, а вход переноса - с выходом логической единицы интерполятора, выход первого двоичного сумматора подключен к первой и второй группам информационных входов первого коммутатора, причем во второй группе информационных входов коммутатора каждый (1+1)-й разряд подключен к 1-разрядному вы- ходу первого двоичного сумматора, I 1, п, где п - разрядность информационной шины первого сумматора, младший разряд второй группы информационных входов первого коммутатора подключен к общей шине, группа информационных входов которого подключена к выходу регистра остатка, г ои- чем каждый -и разряд выхода регистра ос- тат-а подключен к (Н-1}-му разряду третьей группы входов первого коммутатора, 1 Т, т, где т - разрядность информационной шины pes метра остатка, младший разряд третьей группы информационных входов первого коммутатора подключен к общей шине, группа выходов первого коммутатора подключена к группе входов накапливающего сумматора, вход переноса которого подключен к общей шине, а R-вход сброса подключен к входу записи интерполятора, к третьему входу блока управления и к управляющему входу регистра многоразрядных приращений, вход которого соединен с входом цифрового сегмента интерполятора, а выход - с группой информационных входов второго двоичного сумматора и с первой и второй группами информационных входов третьего коммутатора, причем каждый i-й разряд четвертой группы информационных входов третьего коммутатора подключен к (i + 1)-му разряду регистра многоразрядных приращений, i f, п - 1, где л - разрядность информационной шины регистра многоразрядных приращений, третья и четвертая группы информационных входов третьего коммутатора подключены к выходу второго сумматора, причем каждый i-й разряд чет

вертой группы информационных входов третьего коммутатора подключен к (1+1)-му разряду второго сумматора, I 1, п -1, где п - разрядность информационной ш /жы второго сумматора, младший разряд четвертой группы информационных входов первого коммутатора подключен к общей шине, а вход переноса подключен к выходу логической единицы: старший и младший разряды адресного входа третьего коммутатора подключены соответственно к четвертому и пятому выходам блока управления, четвертый вход которого подключен к младшему разряду регистра многоразрядных приращений, шестой выход блока управления подключен к младшему разряду первой группы информационных входов выходного коммутатора, старшие разряды которой подключены к общей шине, вторая группа информационных входов выходного коммутатора подключена к группе выходов третьего коммутатора, адресный вход выходного коммутатора соединен с седьмым выходом блока управления, восьмой выход которого подключен к адресному входу второго коммутатора, группа выходов которого подключена к группе входов блока инверторов, а первая и вторая группы информационных входов - к разрядным выходам регистра меньшего приращения, причем каждый -й разряд регистра меньшего приращения соединен с (1+1)-м разрядом первой группы информационных входов второю коммутатора, I 1, п, где п - разрядность первой группы информационных входов второго коммутатора, младший разряд которой соединен с общей шиной, девятый выход блока управления подключен к старшему разряду адресного входа первого коммутатора, младший разряд адресного входа которого соединен с выходом знакового разряда накапливающего сумматора и с пятым входом блока управления, шестой и седьмой входы которого подключены соответственно к входу начальной установки и входу признака интерполятора, информационный вход блока управления соединен с входом меньшего приращения интерполятора.

2. Интерполятор по п. 1, отличающийся тем, что блок управления содержит с первого по шестой D-триггеры, семь элементов И, первый, второй и третий элементы ИЛИ, счетчик, формирователь импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к управляющему С-входу первого D-триггера, инверсный выход которого подключен к информационному D-входу первого D-триггера, прямой выход которого подключен к девятому выходу блока управления, седьмой выход которого соединен с прямым вы-, ходом второго D-триггера, информационный D-вход которого подключен к седьмому входу блока управления, восьмой вход кото- 5 рого подключен к управляющему С-входу второго D-триггера, к управляющему S-вхо- ду счетчика и к вторым инверсным входам первого и второго элементов И. шестой вход блока управления соединен с инверсными

0 R-входами третьего и четвертого D-тригге- ров и с первыми входами первого и второго элементов И, выход первого элемента И подключен к инверсным R-входам пятого и первого D-триггеров,- первый вход блока уп5 равления подключен к первому входу первого элемента ИЛИ, выход которого соединен с управляющим С-входом третьего D-триггера, инверсный выход которого подктючен к информационному D-входу третьего триг0 гера, прямой выход которого соединен с ин- формационным D-входом четвертого триггера и с шестым выходом блока управления, восьмой выход которого подключен к выходу второго элемента ИЛИ, первый вход

5 которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, прямым выходом пятого триггера, с информационным D-входом шестого триггера и с вторым входом третьего элемента И, первый вход кото0 рого подключен к прямому выходу формирователя импульсов, инверсный выход которого соединен с вторым входом чет- вертого элемента И, управляющим С-входом четвертого D-триггера и с управ5 ляющим С-входом пятого D-триггера, управ-- ляющий D-вход которого подключен к первому входу четвертого элемента И и к прямому выходу четвертого триггера, инверсный выход которого соединен с первым

0 входом пятого элемента И, инверсный вход которого соединен с выходом третьего элемента И, третьим выходом блока управления, управляющим С-входом счетчика и с управляющим С-входом шестого триггера,

5 прямой выход которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к четвертому выходу блока управления, четвертый вход которого соединен с инверсным вторым входом второго элемента ИЛИ

0 и с первым входом шестого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого подключен к пятому выходу блока управления, второй вход которого соединен с ин5 версным вторым входом шестого элемента И, третий вход которого соединен с вторым инверсным входом седьмого элемента И, третьим инверсным входом второго элемента И, вторым входом первого элемента ИЛИ и выходом счетчика, информационный вход

которого соединен с информационным вхо-дом шестого триггера, пятый вход блока

дом блока управления, второй и первый вы-управления подключен к первому входу

ходы которого подключейы соответственноседьмого элемента И, выход которого подк выходам пятого и четвертого элементов И,ключей к второму входу третьего элемента

выход второго элемента И соединен с R-BXO-5 ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

| Цифровой линейный интерполятор | 1988 |

|

SU1624406A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Устройство для формирования векторов на газоразрядной индикаторной панели | 1988 |

|

SU1642509A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1675849A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| Цифровой линейный интерполятор | 1988 |

|

SU1624405A2 |

| Круговой интерполятор | 1985 |

|

SU1359772A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в выходных графических устройствах с линейными матричными органами регистрации, а также в станках с программным управлением, в которых применяются линейные и матричные органы. Цель изобретения - повышение точности Изобретение относится к автоматике и вычислительной технике и может быть использовано в выводных графических устройствах с линейными матричными органами регистрации, а также в станках с программным управлением, в которых использованы линейные и матричные Органы. Цель изобретения - повышение точности интерполяции. интерполяции. Цифровой интерполятор содержит блок выделения нуля, регистр остатка, три коммутатора, накапливающий сумматор, регистр меньшего приращения, б/ток инверторов, два двоичных сумматора, блок управления, регистр многоразрядных приращений, выходной коммутатор. В интерполяторе в каждый тактовый промежуток времени на выходах формируются многоразрядные шаговые приращения. В первом такте формируется многоразрядное приращение (К+1)/2. В последующие тактовые промежутки на информационном выходе интерполятора формируются многозарядные приращения Кили К-И, порядок следования которых определяется по знаковому разряду накапливающего сумма- гора. Последнее многоразрядное приращение определяется по первому, причем в нем запрещается формирование элементарного шага по ведомой координате. В интерполяторе за счет симметрирования многораа- рядных приращений и отслеживания отклонения их от идеальной прямой достигнута максимальная точность аппроксимации, 1 з. п. ф-лы, 11 ил., 2 табл. На фиг. 1 изображена структурная схема интерполятора; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - граф-схема алгоритма работы интерполятора; на фиг. 4 - временная диаграмма работы блока управления при М 16, N 5; на фиг, 5 - аппроксимация отрезка прямой при М 16, N 5; на фиг. 6-график распределения погрешностей аппроксимации отрезка прямой многоразрядными приращениями при ч (Л о ю ы СП ю ю

п

15 16

22

Фиг. 1

CM

05

LD

со o о

PT

C)

I

i is

- I Д

$

vy

JirUTJlRJlTUlRr 1ЖШДЛЛШ1

Прямой выхсд элемента 3fi

Прямой шхся элемеш а

Выход элемента 40

Прямой выход элемента 44

Л

Выход элемента 52

27

35

34

Выход элемента

20

цг. 4

/

1 2 3 Ч 5 б 7 8 9 10 11 1213 W 15 16

Фие.5

finjirlnrL;

I А1А,

X

(К + 3)/2

Фиг.7

Фиг 6

х

о

ПриA l Q-C при в-В

Фие.8

tf

V.

о

Ј

I

55

n

r

JT Ј

31- 34

Фае. 9

Й

I

56

«M

i

s

n

l

43

Ao

Фиг.10

Фиг.11

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-11-23—Публикация

1989-07-24—Подача