1

Изобретение относится к вычислительной технике, а именно к устройствам контроля и диагностики ЭВМ.

Цель изобретения - расширение области применения путем обеспечения возможности анализа информации с асинхронным периодом поступления.

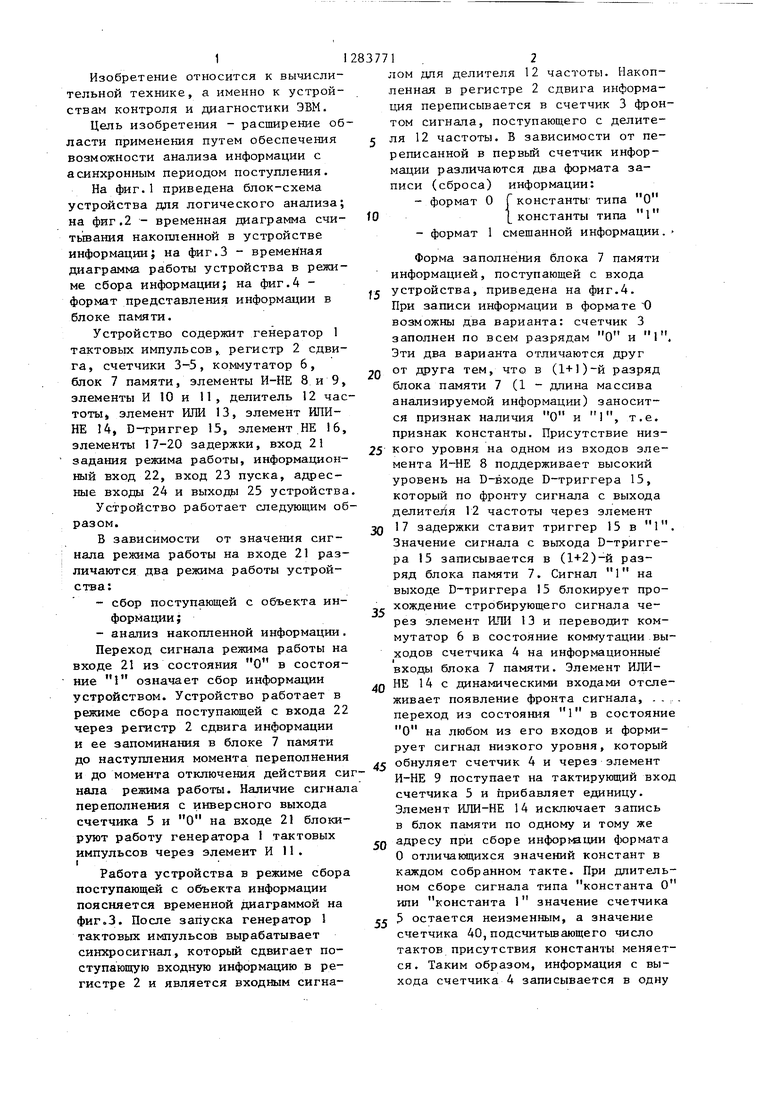

На фиг.1 приведена блок-схема устройства для логического анализа; на фиг.2 - временная диаграмма счи- тьЬания накопленной в устройстве информации; на фиг.З - временная диаграмма работы устройства в режиме сбора информации; на фиг.4 - формат представления информации в блоке памяти.

Устройство содержит генератор 1 тактовых импульсов, регистр 2 сдвига, счетчики 3-5, коммутатор 6,

блок 7 памяти, элементы И-НЕ 8 и 9, элементы И 10 и 11, делитель 12 частоты элемент ИЛИ 13, элемент ИПИ- НЕ 14, D-триггер 15, элемент.НЕ 16, элементы 17-20 задержки, вход 2 i задания режима работы, информационный вход 22, вход 23 пуска, адресные входы 24 и выходы 25 устройства.

Устройство работает следующим образом.

В зависимости от значения сигнала режима работы на входе 21 различаются два режима работы устройства:

-сбор поступающей с объекта информации ;

-анализ накопленной информации. Переход сигнала режима работы на

входе 21 из состояния О в состояние 1 означает сбор информации устройством. Устройство работает в режиме сбора поступающей с входа 22 через регистр 2 сдвига информации и ее запоминания в блоке 7 памяти до наступления момента переполнения

20

25

30

35

40

Форма заполнения блока 7 памяти информацией, поступающей с входа 12 устройства, приведена на фиг.4. При записи информации в формате Ю возможны два варианта: счетчик 3 заполнен по всем разрядам О и 1 Эти два варианта отличаются друг от друга тем, что в (1+1)-и разряд блока памяти 7 (1 - длина массива анализируемой информации) заносится признак наличия О и , т.е. признак константы. Присутствие низ кого уровня на одном из входов эле мента И-НЕ 8 поддерживает высокий уровень на D-входе D-триггера 15, который по фронту сигнала с выхода делитеЛя 12 частоты через элемент 17 задержки ставит триггер 15 в 1 Значение сигнала с выхода D-тригге ра 15 записывается в (1+2)-й разряд блока памяти 7. Сигнал 1 на выходе В триггера 15 блокирует про хождение стробирующего сигнала через элемент ИЛИ 13 и переводит ком мутатор 6 в состояние коммутации в ходов счетчика 4 на информационные входы блока 7 памяти. Элемент ИЛИ- НЕ 14 с динамическими входами отсл живает появление фронта сигнала, . переход из состояния 1 в состоян О на любом из его входов и форми рует сигнал низкого уровня, который

4 обнуляет счетчик 4 и через элемент и до момента отключения действия сиг- м.т, о

нала режима работы. Наличие сигнала переполнения с инверсного выхода счетчика 5 и О на входе 21 блокируют работу генератора 1 тактовых

импульсов через элемент И 11. I

Работа устройства в режиме сбора поступающей с объекта информации поясняется временной диаграммой на фиг.З. После запуска генератор 1 тактовых импульсов вырабатывает синхросигнал, который сдвигает поступающую входную информацию в регистре 2 и является входным сигна50

55

поступает на тактирующий вх счетчика 5 и прибавляет единицу. Элемент ШШ-НЕ 14 исключает запись в блок памяти по одному и тому же адресу при сборе инфорьации 4хэрмат О отличающихся значений констант в каждом собранном такте. При длител ном сборе сигнала типа константа или константа 1 значение счетчика 5 остается неизменным, а значение счетчика 40, подсчитьшающего число тактов присутствия константы меняе ся. Таким образом, информация с вы хода счетчика 4 записывается в одну

2

лом для делителя 12 частоты. Накопленная в регистре 2 сдвига информация переписывается в счетчик 3 фронтом сигнала, поступающего с делителя 12 частоты. В зависимости от переписанной в первьй счетчик информации различаются два формата записи (сброса) информации:

-формат О Г константы- типа О

константы типа 1

-формат 1 смешанной информации.

Форма заполнения блока 7 памяти информацией, поступающей с входа устройства, приведена на фиг.4. При записи информации в формате Ю возможны два варианта: счетчик 3 заполнен по всем разрядам О и 1. Эти два варианта отличаются друг от друга тем, что в (1+1)-и разряд блока памяти 7 (1 - длина массива анализируемой информации) заносится признак наличия О и , т.е. признак константы. Присутствие низкого уровня на одном из входов элемента И-НЕ 8 поддерживает высокий уровень на D-входе D-триггера 15, который по фронту сигнала с выхода делитеЛя 12 частоты через элемент 17 задержки ставит триггер 15 в 1. Значение сигнала с выхода D-триггера 15 записывается в (1+2)-й разряд блока памяти 7. Сигнал 1 на выходе В триггера 15 блокирует прохождение стробирующего сигнала через элемент ИЛИ 13 и переводит коммутатор 6 в состояние коммутации выходов счетчика 4 на информационные входы блока 7 памяти. Элемент ИЛИ- НЕ 14 с динамическими входами отслеживает появление фронта сигнала, . . ,. переход из состояния 1 в состояние О на любом из его входов и формирует сигнал низкого уровня, который

обнуляет счетчик 4 и через элемент м.т, о

поступает на тактирующий вход счетчика 5 и прибавляет единицу. Элемент ШШ-НЕ 14 исключает запись в блок памяти по одному и тому же адресу при сборе инфорьации 4хэрмата О отличающихся значений констант в каждом собранном такте. При длительном сборе сигнала типа константа О или константа 1 значение счетчика 5 остается неизменным, а значение счетчика 40, подсчитьшающего число тактов присутствия константы меняется. Таким образом, информация с выхода счетчика 4 записывается в одну

3

я и-:мку блока 7 ггамяти до тех пор, пока НС произойдет переполнения этого счетчика 4, сигнал с выхода переполнения которого прибавляет 1 к значению счетчика 5, получив новый адрес следующей ячейки блока памяти 7. Вход записи блока памяти в режиме сбора поступающей информации нахо 0

дится в состоянии

, вход записи

которого согласно временной диаграмме на фиг.З обрабатывает процедуру записи. Элемент 19 задержки с инверсией необходим дпя компенсации времени срабатывания элементов И-НЕ 9, счетчика 5 и элемента ШШ-НЕ с динамическими входами.

При записи поступающей с объекта информации в формате 1 в счетчик 3 переписывается смешанная информация. В результате на выходах счетчика -3 присутствуют сигналы 1, Таким образом, D-триггер первым тактирующим сигналом устанавливается в значение О, сигнал с KiDTOporo переключает коммутатор 6 на трансляцию информации с выходов счетчика 3 на информационную группу входов блока 7 памяти, по информационному входу которого записывается О - признак формата 1 . Сигнал О на входе элемента ИЛИ 13 разрешает прохождение сигнала на вход элемента И-НЕ 9, с выхода которого сигнал поступает на вход счета счетчика 5, который прибавляет единицу к текущему адресу и т.д. Элементы 17 задержки и элементы 18 и 19 задержки с инверсией необходимы дпя устойчивой безошибочной работы устройства в режиме сбора информации с объекта диагностирования. При поступлении на вход 21 сигнала О устройство переходит в режим анализа накопленной в блоке памяти 7 информации. Считывание и анализ . накоппенной информации осуществляется согласно временной диаграмме, представленной на фиг.2.

Формирование информации, записываемой в память 7, позволяет анализировать большие массивы поступающей информации, не снижая частот14 ее сканирования.

Формула изобретения

Логический анализатор, содержащий генератор тактовых импульсов, регистр сдвига, три счетчика, блок памяти, элемент НЕ, первь1Й элемент И,

8377I4

элеменч- задержки, причем ход первог о элемента задержки соединен с первым входом первого элемента И, выход генератора тактовых .с импульсов соединен с синхровходом регистра сдвига, информационный вход которого является информационным входом анализатора, группа выходов регистра соединена с группой инфор- fO мационных входов первого счетчика, адресные входы анализатора соединены с информационными входами второго счетчика, группа разрядных выходов которого соединена с адресной )5 группой входов блока памяти, выходы которого являются выходами анализатора, вход задания режима которого соединен через элемент НЕ с входом записи блока памяти, вход синхрони- 20 зации которого соединен с выходом первого элемента И, вход пуска анализатора соединен с входом записи второго счетчика и входом первого элемента задержки, отличающий - 25 с я тем, что, с целью расширения области применения путем обеспечения возможности анализа информации с асинхронным периодом поступления, анализатор содержит коммутатор, де- 30 литель частоты, D-триггер, два элемента И-НЕ, второй элемент И, элемент ИЛИ-НЕ , элемент ИЛИ, второй, третий и четвертый элементы задержки, причем выход генератора тактовых 35 импульсов соединен с входом делителя частоты, выход которого соединен с входом записи первого счетчика и через второй элемент задержки с синхровходом D-триггера, синхровхо- 40 дом третьего счетчика и входами третьего и четвертого элементов задержки, инверсные выходы которых соединены с первым входом элемента ИЛИ и вторым входом первого элемента И, вы- 5 ход D-триггера соединен с управляющим входом коммутатора, вторым вхо-. дом элемента ИЛИ и информационным входом блока памяти, информационные входы которого соединеьго с выходами 0 коммутатора, первая группа информационных входов которого соединена с группой разрядш Х выходов первого счетчика, вторая группа информационных входов коммутатора соединена с 5 разрядными выходами третьего счетчика и выходом старшего разряда первого счетчика, вход записи первого счетчика соединен с входом задания режима работы анализатора, инверс 1

ный выход перенслнения гречч ет О счетчика соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с выходом элемента ИЛИ-НЕ, с инверсным входом сброса третьего счетчика, выход переполнения второго счетчика соединен с вторым входом второго элемента И, выход которого соединен с входом пуска генератора тактовых импульсов инверсный выход переполнения гтервоВ)од 2 5ло( 7

В3771и

го (. соединен с первь м тчходоч второго элемента И-НЕ и элемента ИЛИ-НЕ, инверсный выход заема ггерво- го счетчика соединен с вторыми вхо- 5 дами второго элемента И-НЕ и элемента ИЛИ-НЕ, выход элемента ИЛИ соединен с третьим входом нервого элемента И-НЕ, выход которого соединен-с синхровходом первого счетчика, вы- 10 ход второго элемента И-НЕ со единен с D-ВХОДОМ D-триггера.

Инфор 1аи,ионньгй

Ф1Аг2

Инсрормация доспюверна

3anyci PP

Выход делителя частоты

Второй упр. СТ25

Второй упр, Ьл. 7

HHqj- Входы дл. 7

opMQm ЗначениеVt/c/io тактов константы при ФО

.константыЗначение сигнала при 1

Фиг,.Ц

- Ин(рормаи,ия достоверна

Фие,3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации результатов контроля | 1985 |

|

SU1406596A1 |

| Логический анализатор | 1988 |

|

SU1587511A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для сбора и анализа данных о работе информационно-вычислительной системы | 1990 |

|

SU1795476A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для воспроизведения изображения на матричном экране | 1987 |

|

SU1596487A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для передачи и приема информации | 1984 |

|

SU1269174A1 |

Изобретение относится к области .вычислительной техники, а именно к устройствам контроля и диагностики ЭВМ. Цель изобретения - расширение области применения. Сущность изобретения состоит в том, что в известное устройство, содержащее генератор тактовых импульсов, регистр, первый, второй, третий счетчики, блок памяти, элемент НЕ, элемент И и элемент задержки, дополнительно введены мультиплексор, делитель частоты, D- триггер, два элемента И-НЕ, элемент И, формирователь импульсов, элемент ИЛИ и три элемента задержки. 4 ил.

| Устройство для многоканального контроля | 1976 |

|

SU608126A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США № 4373193, :.: | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-07-31—Подача