(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для функционального контроля цифровых блоков | 1983 |

|

SU1196875A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке тестового диагностического обеспечения выпускаемых устройств. Цель изобретения - обеспечение режима формирования тестовой информации для субблока логического блока с собственной синхронизацией. Устройство содержит эталонный субблок 1, эталонный логический блок 2, коммутатор 4, блок 7 регистрации, таймер 6, блок 5 промежуточного накопления тестов. Происходит формирование тестов для субблоков и логических блоков по отношению к системам внешней синхронизации. 3 ил.

сд

Од

СД

00

315

Изобретение относится к техническому диагностированию дискретных устройств автоматики, вычислительной техники и связи, а именно к устройствам автоматического формирования тестов проверки работоспособности их логических субблоков.

Целью изобретения является обеспечение режима формирования тестовой информации для субблока логического блока с собственной синхронизацией.,

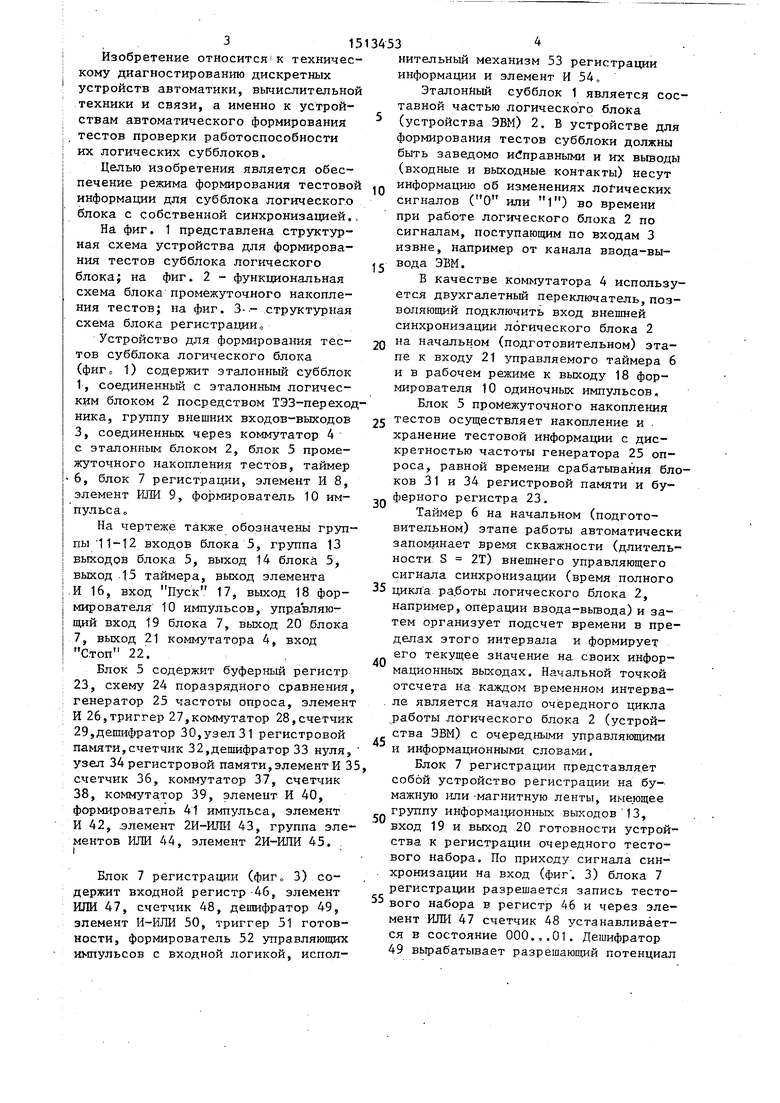

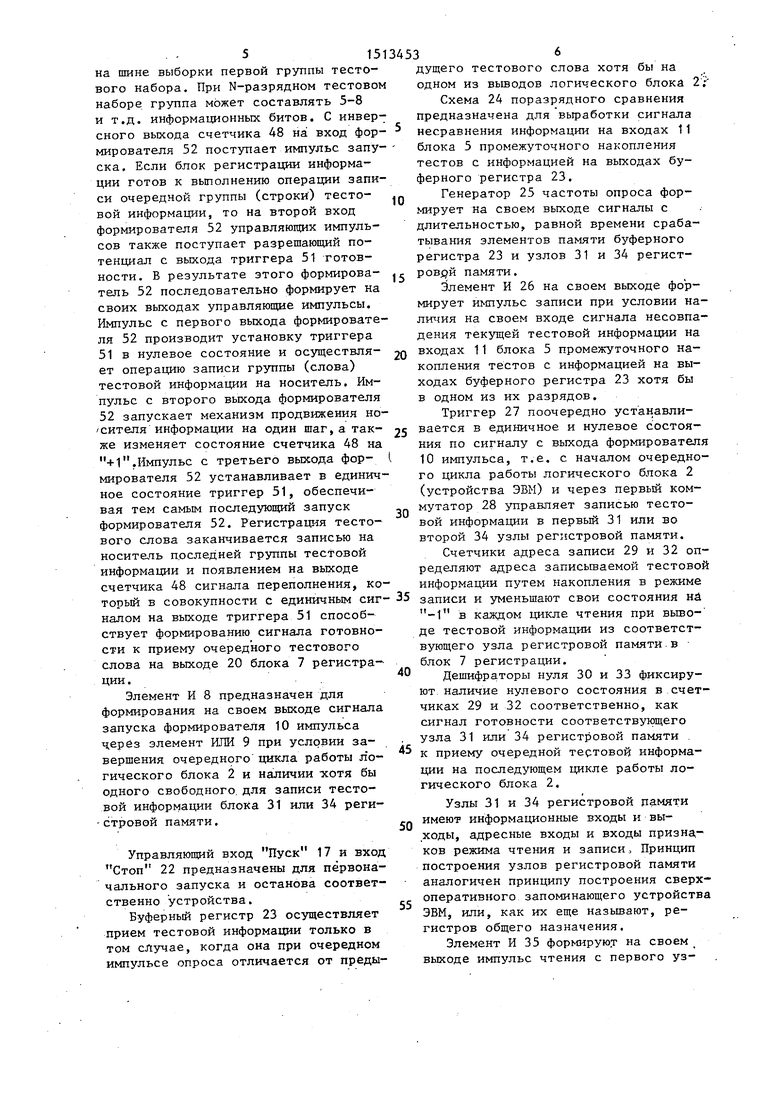

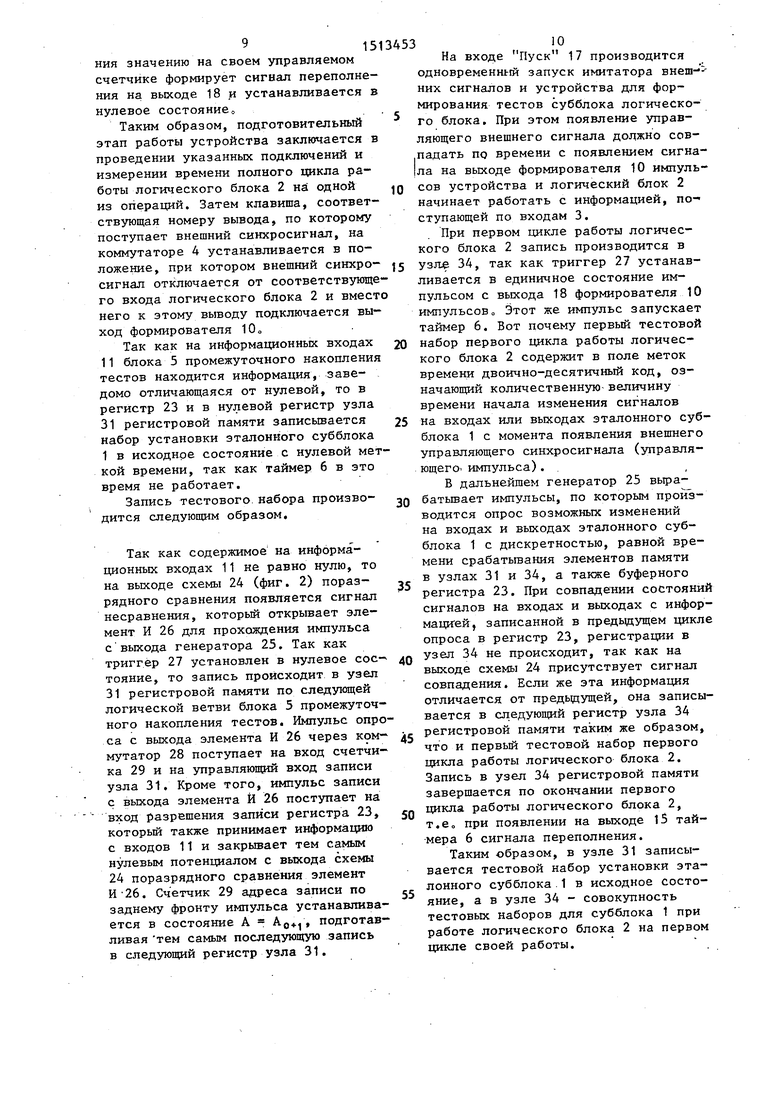

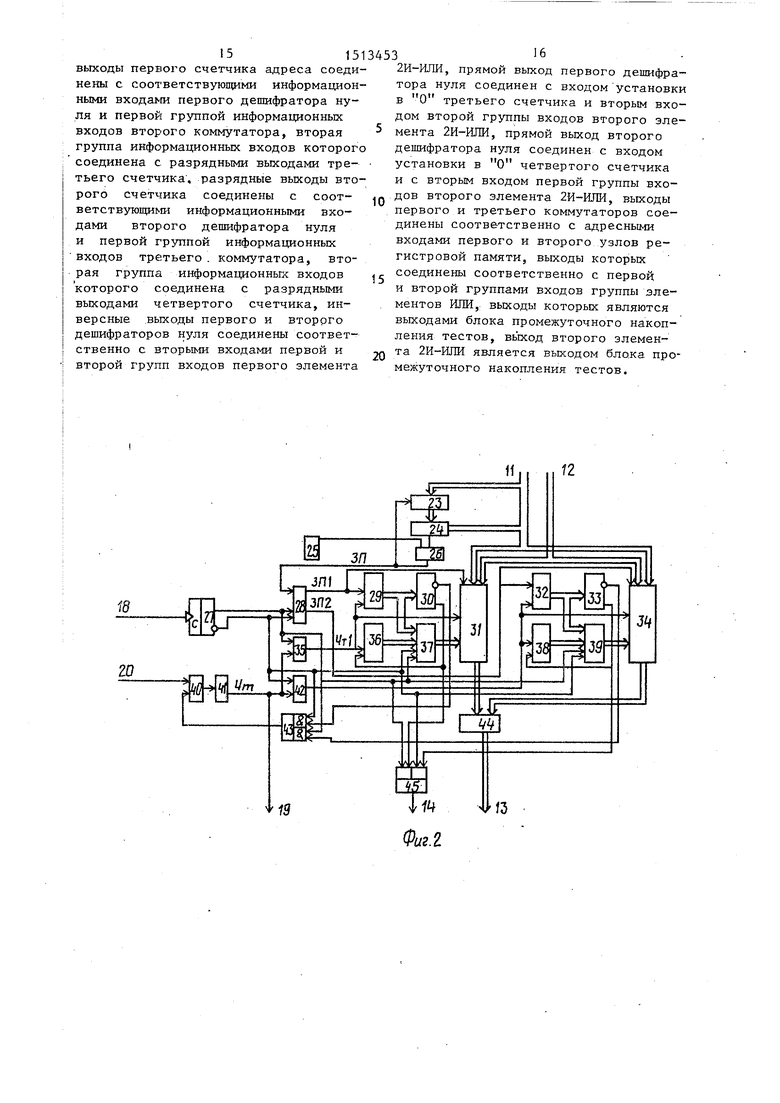

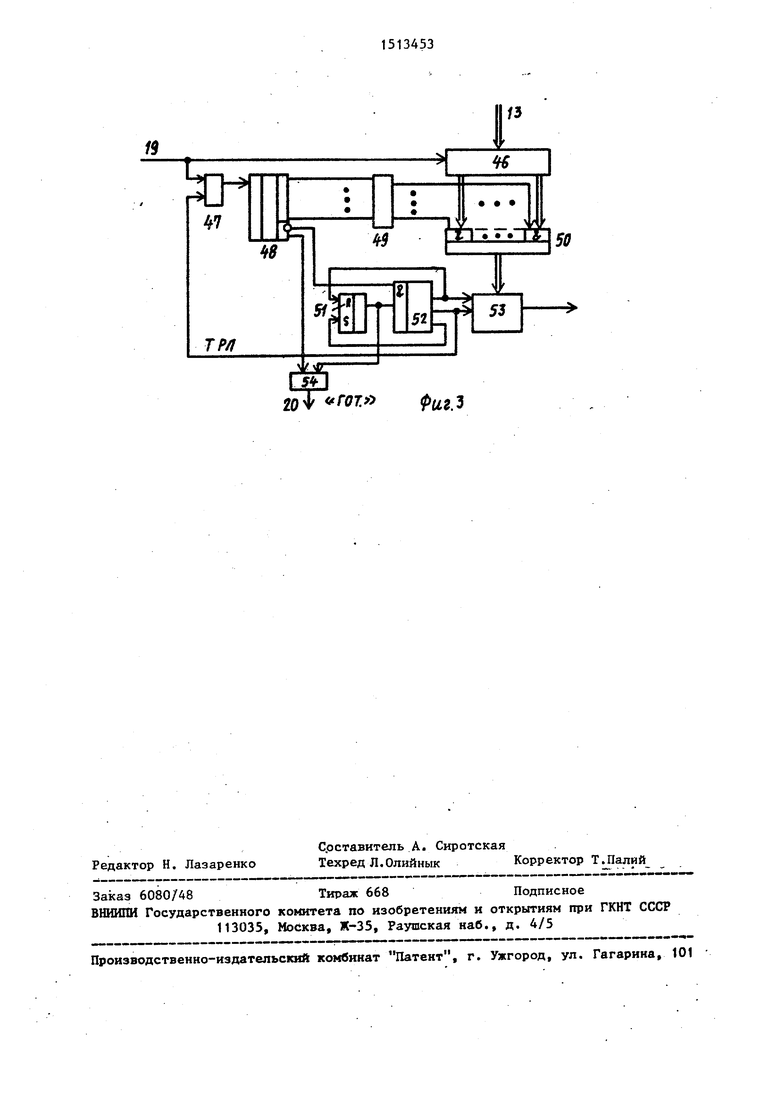

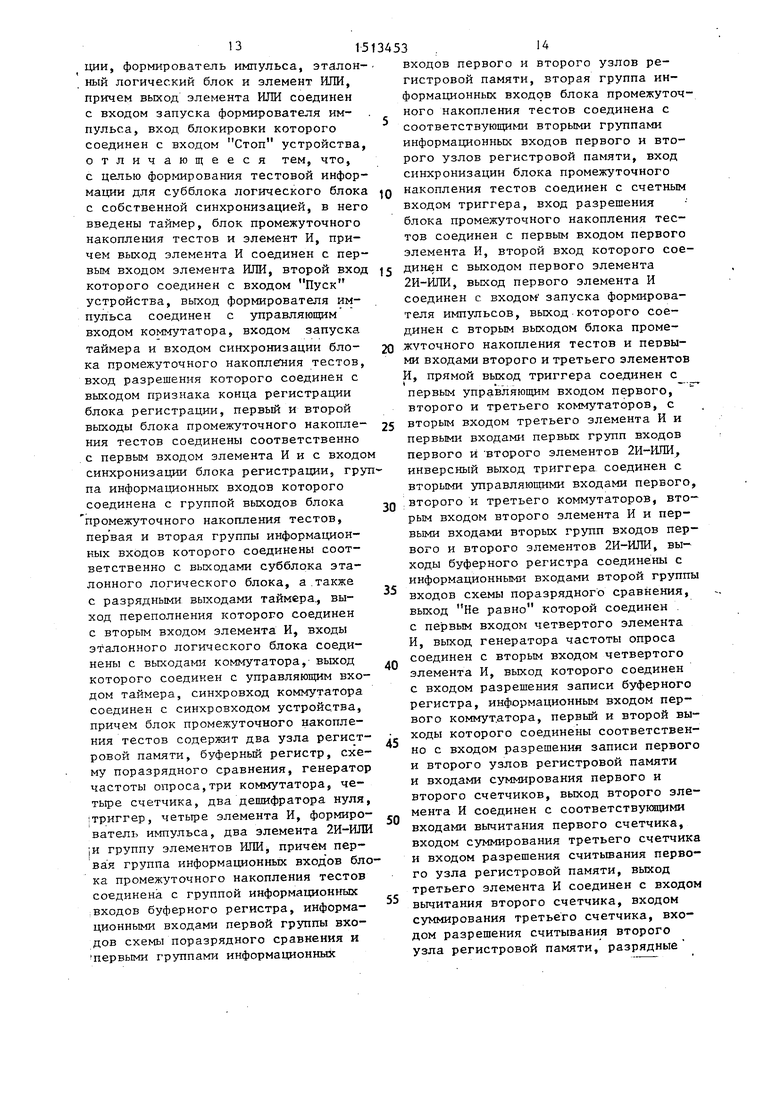

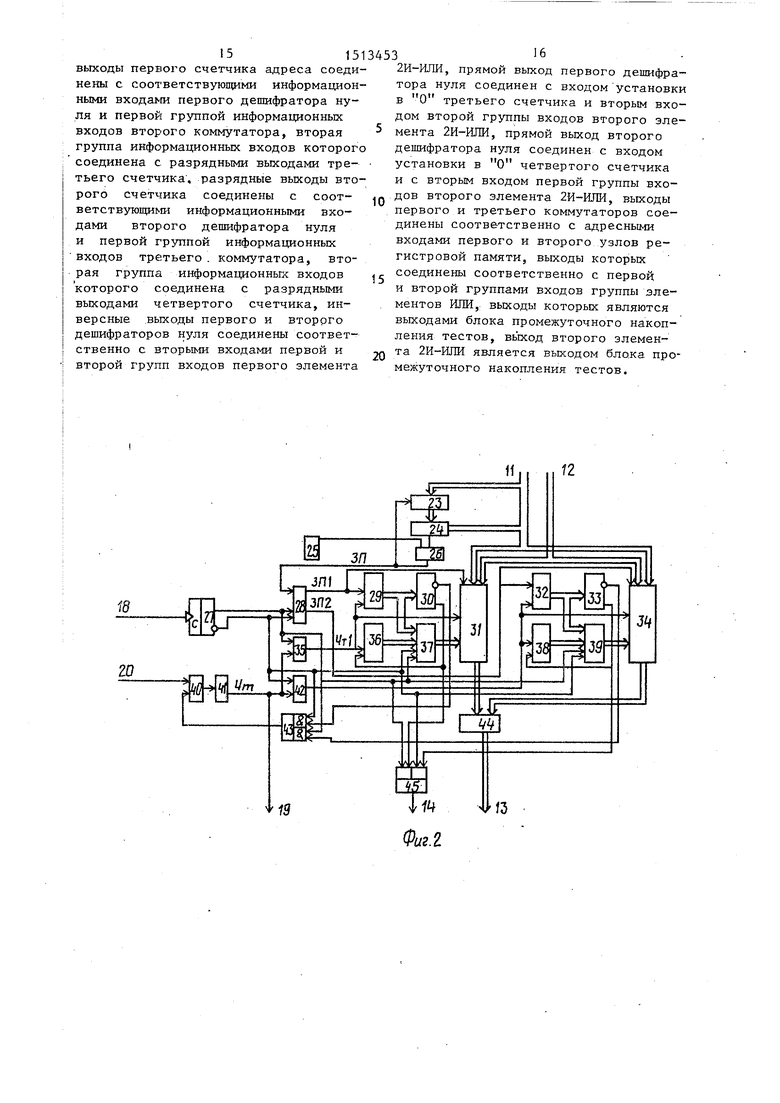

На фиг. 1 представлена структур™ ная схема устройства для формирования тестов субблока логического блокад на фиг. 2 - функциональная схема блока промежуточного накопления тестов; на фиг. 3-- структурная схема блока регистрациио

Устройство для формирования тестов субблока логического блока (фиго 1) содержит эталонный субблок 1, соединенный с эталонным логическим блоком 2 посредством ТЭЗ-переход ника, rpjmny внешних входов-выходов 3, соединенных через коммутатор 4 с эталонным блоком 2, блок 5 промежуточного накопления тестов, таймер

6,блок 7 регистрации, элемент И 8, элемент ШШ 9, формирователь 10 импульса о

На чертеже также обозначены грзш- пы 11-12 входов блока 5, группа 13 выходов блока 5, выход 14 блоки 5, выход .15 таймера, выход элемента ,И 16, вход Пуск 17, выход 18 формирователя 10 импульсов, управляющий вход 19 блока 7, выход 20 блока

7,выход 21 коммутатора 4, вход Стоп 22.

Блок 5 содержит буферный регистр 23, схему 24 поразрядного сравнения, генератор 25 частоты опроса, элемент И 26,триггер 27,коммутатор 28,счетчик 29,дешифратор 30,узел 31 регистровой памяти,счетчик 32,дешифратор 33 нуля, узел 34 регистровой памяти, элемент И 3 счетчик 36, коммутатор 37, счетчик 38, коммутатор 39, элемент И 40, формирователь 41 импульса, элемент И 42, элемент 2И-ИЛИ 43, группа элементов ИЛИ 44, элемент 2И-ИПИ 45. , I

Блок 7 регистрации (фиг„ 3) содержит входной регистр 46, элемент ИЛИ 47, счетчик 48, дешифратор 49, элемент И-ИЛИ 50, триггер 51 готовности, формирователь 52 управляющих и.тульсов с входной логикой, испол453

нительный механизм 53 регистрации информации и элемент И 54„

Эталонный субблок 1 является составной частью логического блока (устройства ЭВМ) 2. В устройстве для формирования тестов субблоки должны быть заведомо исправными и их вьюоды (входные и выходные контакты) несут информацию об изменениях логических сигналов (О или 1) во времени при работе логического блока 2 по сигналам, поступающим по входам 3 извне, например от канала ввода-вы- вода ЭВМ.

В качестве коммутатора 4 используется двухгалетный переключатель,позволяющий подключить вход внешней синхронизации логического блока 2 0 на начальном (подготовительном) этапе к входу 21 управляемого таймера 6 и в рабочем режиме к выходу 18 формирователя 10 одиночных импульсов.

Блок 5 промежуточного накопления 5 тестов осуществляет накопление и хранение тестовой информации с дискретностью частоты генератора 25 опроса, равной времени срабатьгаания блоков 31 и 34 регистровой памяти и буферного регистра 23.

Таймер 6 на начальном (подготовительном) этапе работы автоматически запоминает время скважности (длительности S 2Т) внешнего управляющего сигнала синхронизации (время полного 35 здикла работы логического блока 2, например, операции ввода-вьшода) и затем организует подсчет времени в пределах этого интервала и формирует его текущее значение на своих информационных выходах. Начальной точкой отсчета на каждом временном интерва- . ле является начало очередного цикла работы логического блока 2 (устройства ЭВМ) с очередными управляющими и информационными словами,

Блок 7 регистрации представляет собой устройство регистрации на бумажную 1-ши -магнитную лентьг, имеющее группу информа1Д10нных выходов 13, вход 19 и выход 20 готовности устройства к регистрации очередного тестового набора. По приходу сигнала син- . хронизахщи на вход (фиг . 3) блока 7

регистрации разрешается запись тесто- 55 вого набора в регистр 46 и через элемент ИЛИ 47 счетчик 48 устанавливается в состояние 000.,.01. Дешифратор 49 вырабатывает разрешающий потенциал

30

40

45

50

на шине выборки первой группы тестового набора. При N-разрядном тестовом наборе группа может составлять 5-8 и т.д. информационных битов. С инверсного выхода счетчика 48 Hai вход формирователя 52 поступает импульс запуска. Если блок регистрации информации готов к выполнению операции записи очередной группы (строки ) тестовой информации, то на второй вход формирователя 52 управляющих импульсов также поступает разрешающий потенциал с выхода триггера 51 готовности. В результате этого формирователь 52 последовательно формирует на своих выходах управляющие импульсы. Импульс с первого выхода формирователя 52 производит установку триггера

51в нулевое состояние и осуществляет операцию записи группы (слова) тестовой информации на носитель. Импульс с второго выхода формирователя

52запускает механизм продвижения но- сителя информации на один шаг,а также изменяет состояние счетчика 48 на +1.Импульс с третьего выхода фор- мирователя 52 устанавливает в единичное состояние триггер 51, обеспечивая тем самым последующий запуск формирователя 52. Регистрация тестового слова заканчивается записью на носитель п.оследней группы тестовой информации и появлением на выходе счетчика 48 сигнала переполнения, который в совокупности с единичным сигналом на выходе триггера 51 способствует формированию сигнала готовности к приему очередного тестового слова на выходе 20 блока 7 регистрации.

Элемент И В предназначен для формирования на своем выходе сигнала запуска формирователя 10 импульса через элемент ИЛИ 9 при условии завершения очередного цикла работы гического блока 2 и наличии хотя бы одного свободного, для записи тестовой информации блока 31 или 34 реги- -стровой памяти.

УпpaвляюшJ й вход Пуск 17 и вход Стоп 22 предназначены для первоначального запуска и останова соответственно устройства.

Буферный регистр 23 осуществляет прием тестовой информации только в том сЛзгчае, когда она при очередном импульсе опроса отличается от преды0

5

0

5

0

5

0

5

0

5

дущего тестового слова хотя бы на одном из вьшодов логического блока 2:

Схема 24 поразрядного сравнения предназначена для выработки сигнала несравнения информации на входах 11 блока 5 промежуточного накопления тестов с информацией на выходах буферного регистра 23.

Генератор 25 частоты опроса формирует на своем выходе сигналы с длите«тьностью, равной времени срабатывания элементов памяти буферного регистра 23 и узлов 31 и 34 регист- ровдй памяти.

Элемент И 26 на своем выходе формирует импульс записи при условии на- на своем входе сигнала несовпадения текущей тестовой информации на входах 11 блока 5 промежуточного накопления тестов с информацией на выходах буферного регистра 23 хотя бы в одном из их разрядов.

Триггер 27 поочередно устанавливается в единичное и нулевое состояния по сигналу с выхода формирователя 10 импульса, т.е. с началом очередного цикла работы логического блока 2 (устройства ЭВМ) и через первьй коммутатор 28 управляет записью тестовой информации в первый 31 или во второй 34 узлы регистровой памяти.

Счетчики адреса записи 29 и 32 определяют адреса записываемой тестовой информации путем накопления в режиме записи и зт еньшают свои состояния ни -1 в каждом цикле чтения при вьшо- де тестовой информации из соответствующего узла регистровой памяти.в блок 7 регистрации.

Дешифраторы нуля 30 и 33 фиксируют наличие нулевого состояния в счетчиках 29 и 32 соответственно, как сигнал готовности соответствующего узла 31 или 34 регистровой памяти . к приему очередной тестовой информации на последующем цикле работы логического блока 2.

Узлы 31 и 34 регистровой па.мяти имеют информационные входы и выходы, адресные входы и входы призна,- ков режима чтения и записи. Принцип построения узлов регистровой памяти аналогичен принципу построения сверхоперативного запоминающего устройства ЭВМ, или, как их еще назьшают, регистров общего назначения.

Элемент И 35 формируют на своем выходе импульс чтения с первого узла 31 регистровой памяти в случае рулевого состояния триггера 27. Э-тот импульс своим отрицательным ф|ронтом (срезом и myльca) увели- ч|ивает на +1 состояние счетчика . считывания и уменьшает на -1

стояние счетчика 29 адреса записи. Коммутатор 37 пропускает на адсные входы первого узла 3.1 региствой памяти сигналы с выходов счетчика 29 адреса записи в режиме записи и выходов счетчика 36 адреса считывания в режиме вывода тестовой информации в блок 7 регистрации.

Коммутатор 39 пропускает на адресные входы второго узла 34 регистровой памяти сигналы с выходов второго счетчика 32 адреса записи в режиме записи и с выходов счетчика 38 ацреса считывания в режиме вывода в блок 7 регистрации тестовой информации .

Элемент И 40 формирует на своем в|ыходе сигнал запуска формирователя 4|1 импульса при условии готовности dnoKa 7 регистрации к приему очеред- rioro тестового слова (разрешающий потенциал на выходе 20 блока 5 промежуточного накопления тестов) и наличии сигнала занятости тестовой информацией соответствующего узла

1 или 34 регистровой памяти, на- одящегося в режиме чтения.

Элемент И 42 формирует на своем фкоде импульс чтения со второго 34 регистровой памяти при еди- 1|ичном состоянии триггера 27. Этот импульс считывания производит счи- т ывание информации из узла 34 и своим

10

15

20

25

45

отрицательным фронтом увеличивает состояние счетчика 38 и уменьшает Состояние счетчика 32 на единицу.

Элемент 2И-ИЛИ 43 пропускает через свои первую и вторую группы нходов сигнал незавершенного считывания из соответствующего узла 31 и 34 регистровой памяти, находяще- в режиме чтения, т.е. в режиме вывода уже накопленной тестовой информации, в блок 7 регистрации.

Группа элементов ИЛИ 44 пропускает сигналы с первого 31 или второго 34 узлов регистровой памяти, находящихся в режиме чтения, на инфор-. мационные входы 13 блока 7 регистра-55 :ции.

Элемент 2И-ИЛИ 45 пропускает на свой выход 14 сигнал готовности

15134538

соответствующего узла регистровой памяти к приему очередного массива тестовых наборов, сформированного на последующем цикле работы логичес- 5 кого блока 2„ Заметим, что данный узел ранее находился в режиме чтения (вывод тестовых наборов в блок 7 регистрации) и вся тестовая информация бьта считана и зарегистрирована на носителе информации.

Устройство для формирования тестов субблока логического блока работает следующим образом.

Эталонный субблок 1 подключается к логическому блоку 2 (устройству ЭВМ) через кросс-плату (ТЭЗ-пере- ходник), позволяющий подключить к их выводам первую группу информационных входов 11 блока 5 промежуточного накопления тестов.

Внещние входы 3 (входы извне) подключаются к входам коммутатора 4, а его выходы подключены к входам логического блока 2 (например, как подключается последовательно интерфейс ввода-вывода ЭВМ ЕС). Затем к устройству для формирования тестов субблока логического блока с помощью соответствующей клавиши галетного переключателя коммутатора 4 подключается внешний вход, по которому поступают сигналы внешней синхронизации (в некоторых случаях в качестве этого сигнала можно использовать управляющий сигнал начала цикла обмена или цикла работы, например наличие одновременно сигналов ВБР-К и РВБ-К для интерфейса ввода-вывода) к управляющему входу 21 таймера 6. Далее производится включение питания устройства для формирования тестов субблока логического блока, логического блока 2 и эталонного субблока 1. Производится общий сброс логического блока 2 и устройства (цепи установки в исходное сост ояние элементов и узлов устройства не показаны).

Нажатием кнопки, подключенной к внешней синхронизации, на таймере 6 проводится измерение длительности цикла работы логического блока 2 (время между двумя положительными фронтами импульса внешней синхронизации) , численное значение которого запоминается в управляемом счетчике таймера 6. В дальнейшем таймер 6 при достижении своего текущего значе30

35

40

50

15

ния значению на своем управляемом

счетчике формирует сигнал переполнения на выходе 18 и устанавливается в нулевое состояние,,

Таким образом, подготовительный этап работы устройства заключается в проведении указанных подключений и измерении времени полного цикла работы логического блока 2 на одной из операций. Затем клавиша, соответствующая номеру вывода, по которому поступает внешний синхросигнал, на коммутаторе 4 устанавливается в положение, при котором внешний синхросигнал отключается от соответствунще го входа логического блока 2 и вмест него к этому выводу подключается выход формирователя 10с

Так как на информационных входах 11 блока 5 промежуточного накопления тестов находится информация, заведомо отличающаяся от нулевой, то в регистр 23 и в нулевой регистр узла 31 регистровой памяти записывается набор установки эталонного субблока 1 в исходное состояние с нулевой меткой времени, так как таймер 6 в это время не работает.

Запись тестового, набора производится следуюЕцим образом.

Так как содержимое на информационных входах 11 не равно нулю, то на выходе схемы 24 (фиг. 2) поразрядного сравнения появляется сигнал несравнения, который открывает элемент И 26 для прохождения импульса с выхода генератора 25. Так как триггер 27 установлен в нулевое сое- тояние, то запись происходит в узел 31 регистровой памяти по следующей логической ветви блока 5 промежуточного накопления тестов. Импульс опроса с выхода элемента И 26 через коммутатор 28 поступает на вход счетчика 29 и на управляющий вход записи узла 31. Кроме того, импульс записи с выхода элемента И 26 поступает на вход разрешения записи регистра 23, который также принимает информацию с входов 11 и закрывает тем самым нулевым потенциалом с выхода схемы 24 поразрядного сравнения элемент И-26. Счетчик 29 адреса записи по заднему фронту импульса устанавливается в состояние А AQ, подготавливая тем самым последующую запись в следующий регистр узла 31.

45310

На входе Пуск 17 производится одновременный запуск имитатора внеш- -- них сигналов и устройства для формирования тестов субблока логического блока. При этом появление управляющего внешнего сигнала должно сов- .падать по времени с появлением сигна- |ла на выходе формирователя 10 импуль0 сов устройства и логический блок 2 начинает работать с информацией, по- ступающей по входам 3.

При первом цикле работы логического блока 2 запись производится в

5 уэдъе 34, так как триггер 27 устанавливается в единичное состояние импульсом с выхода 18 формирователя 10 импульсов Этот же импульс запускает таймер 6. Вот почему первый тестовой

0 набор первого цикла работы логического блока 2 содержит в поле меток времени двоично-десятичный код, означающий количественную-величину времени начала изменения сигналов

5 на входах или выходах эталонного субблока 1 с момента появления внешнего управляющего синхросигнала (управля- ющего импульса) .

В дальнейшем генератор 25 выра0 батывает импульсы, по которым проиЪ- водится опрос возможных изменений на входах и выходах эталонного субблока 1 с дискретностью, равной времени срабатьшания элементов памяти в узлах 31 и 34, а также буферного регистра 23. При совпадении состояний сигналов на входах и выходах с информацией, записанной в предьщущем цикле опроса в регистр 23, регистрации в

0 узел 34 не происходит, так как на выходе схемы 24 присутствует сигнал совпадения. Если же эта информация отличается от предьщущей, она записывается в следующий регистр узла 34

., регистровой памяти таким же образом, что и первый тестовой набор первого цикла работы логического блока 2. Запись в узел 34 регистровой памяти завершается по окончании первого

n цикла работы логического блока 2, т.е„ при появлении на выходе 15 таймера 6 сигнала переполнения.

Таким образом, в узле 31 записывается тестовой набор установки эталонного субблока.1 в исходное состояние, а в узле 34 - совокупность тестовых наборов для субблока 1 при работе логического блока 2 на первом цикле своей работы.

Для повьшения быстродействия устройства реализовано совмещение режимов промежуточного накопления тестов с режимом вывода накопленной тестовой информации в блок 7 регистрации (для блока 5 промежуточного накоп- ления тестов - режимы записи и чтения соответственно ) .

Совмещение режима чтения и режима записи осуществляется слёдзпощим образ ом , В момент приема в узел 31 тестового набора установки, в исходное. состояние эталонного блока 1 счетчик

29 адреса записи принимает состояние, j5 ° появляется сигнал готовности равное 000.01, и на инверсном выходе узла 31 (в данном случае) к приему

дешифратора 30 появляется высокий логический уровень сигнала, который, поступая на второй вход первой группы входов элемента 2И-РШИ 43, открывает эту группу входов для формирования сигнала готовности узла 31 к режиму чтения (к выводу записанного набора в блок 7 регистрации). Как только триггер 27 установится в единичное состояние, то высокий логический уровень сигнала с выхода, элемента 2И-ИЛИ 43 поступит на вход элемента И 40, При готовности блока 7 регистрации к приему тестового слова (высокий логический уровень сигнала на выходе 20) на вход формирователя 4 Г импульса поступает сигнал запуска положительным фронтом. Импульс с выхода формирователя 41 поступает на вход 19 блока 5 промежуточного накопления тестов как сигнал запуска блока 7 регистрации и на входы элементов И 35 и 42.

Так как в это время установлен режим записи в узел 34 регистровой памяти (триггер 27 находится в единичном состоянии), то импульс чтения проходит через элемент И 35 и поступает на вход режима чтения узла 31, вход вычитания счетчика 29 адреса записи и на вход накопления счетчика 36 адреса считывания. В результате этого информация с выходов узла 31, поступает через группу элементов ИЛИ 44 на.выход блока 5 промежуточного накопления, тестов и по срезу импульса чт€ .ния устанавливает счетчик 29 в нулевое состояние, а счетчик 36 - в состояние 000.. .01 (счетчик 29 в большинстве случаев на начальном этапе после режима записи находится в состоянии 000о..01, так как тестовый набор установки в исходное

новой совокупности тестовых наборов формируемых на втором цикле работы логического блока 2.

20 Если же за это время был законче режим записи тестовой информации в узел 34, элемент И 8 (фиг. 1) форми рует на своем выходе высокий логиче кий уровень сигнала, который через

25 элемент ИЛИ 9 запускает формирователь 10 импульса и который означает что начался третий цикл работы логи ческого блока 2.

Совмещение режима записи в узел

30 и режима чтения из узла 34 на треть цикле работы логического блока.2 осуществляется аналогичным образом, Тое на третьем цикле работы логиче кого блока 2 осуществляется запись совокупности тестов для эталонного субблока 1 в узел 31 и чтение (выво тестов в блок 7 регистрации) из узл 34 регистровой памяти.

По окончании вывода тестовой информации из узла 34 в-блок 7 регист рации формирователем 10 запускается четвертый цикл работы логического блока 2 и т.д.

Регистрация тестов для субблока логического блока 2 завершается при окончании заданного режима проверки логического блока 2 от имитатора внешних сигналов. На устройстве подается сигнал Стоп. Работа устрой ства заканчивается.ре гистрацией бло ком 7 из соответствующего узла 31 и 34 регистровой памяти совокупности тестовых наборов последнего цикла работы логического блока 2.

55 Формула изобретени

Устройство для формирования тестов субблока логического блока, содержащее коммутатор, блок регистра

35

40

45

50

состояние эталонного субблока 1 чаще всего оказывается в единственном числе)о Итак, счетчик 29 устанавливается в нулевое состояние ив резуль- «тате этого на прямом выходе дешифратора 30 появляется высокий логический уровень сигнала, а на его инверсном выходе - низкий логический уровень сигнала. Первая группа входов элемента 2И-ШШ 43 закрьшается и открывается вторая группа входов элемента 2И-ИЛИ 45 На выходе 14 блока 5 промежуточного накопления тесновой совокупности тестовых наборов, формируемых на втором цикле работы логического блока 2.

Если же за это время был закончен режим записи тестовой информации в узел 34, элемент И 8 (фиг. 1) формирует на своем выходе высокий логический уровень сигнала, который через

элемент ИЛИ 9 запускает формирователь 10 импульса и который означает, что начался третий цикл работы ческого блока 2.

Совмещение режима записи в узел 31

и режима чтения из узла 34 на третьем цикле работы логического блока.2 осуществляется аналогичным образом, Тое на третьем цикле работы логического блока 2 осуществляется запись совокупности тестов для эталонного субблока 1 в узел 31 и чтение (вывод тестов в блок 7 регистрации) из узла 34 регистровой памяти.

По окончании вывода тестовой информации из узла 34 в-блок 7 регистрации формирователем 10 запускается четвертый цикл работы логического блока 2 и т.д.

Регистрация тестов для субблока 1 логического блока 2 завершается при окончании заданного режима проверки логического блока 2 от имитатора внешних сигналов. На устройстве подается сигнал Стоп. Работа устройства заканчивается.ре гистрацией блоком 7 из соответствующего узла 31 или 34 регистровой памяти совокупности тестовых наборов последнего цикла работы логического блока 2.

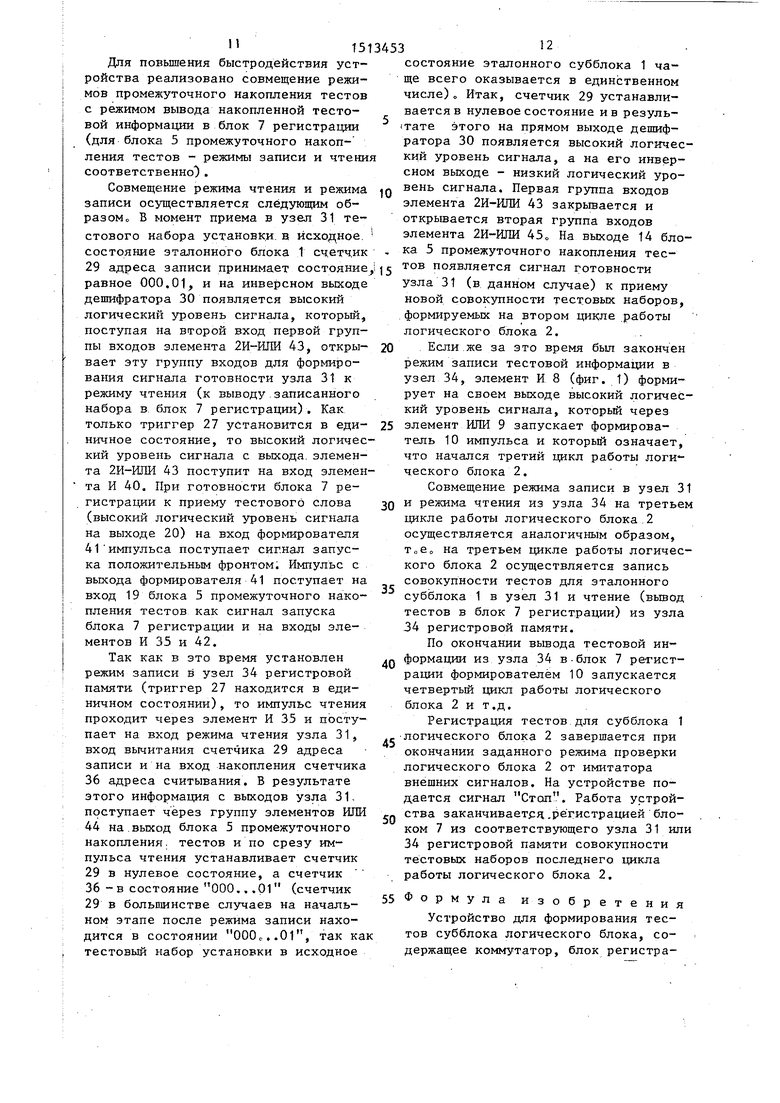

Формула изобретения

Устройство для формирования тестов субблока логического блока, содержащее коммутатор, блок регистра

131-5

ции, формирователь импульса, эталон- ный логический блок и элемент ИЛИ, причем выход элемента ИЛИ соединен с входом запуска формирователя им- . пульса, вход блокировки которого соединен с входом Стоп устройства, отличающееся тем, что, с целью формирования тестовой информации для субблока логического блока с собственной синхронизацией, в него введены таймер, блок промежуточного накопления тестов и элемент И, причем выход элемента И соединен с первым входом элемента ИЛИ, второй вход которого соединен с входом Пуск устройства, выход формирователя импульса соединен с управляющим входом коммутатора, входом запуска таймера и входом синхронизации блока промежуточного накопления тестов, вход разрешения которого соединен с выходом признака конца регистрации блока регистрации, первый и второй выходы блока промежуточного накопления тестов соединены соответственно с первым входом элемента И и с входом синхронизации блока регистрации, груп а информационных входов которого соединена с группой выходов блока ромежуточного накопления тестов, ервая и вторая группы информационных входов которого соединены соответственно с выходами субблока этаонного логического блока, а.также с разрядными выходами таймера., выход переполнения которого соединен с вторым входом элемента И, входы эталонного логического блока соединены с выходами коммутатора,- выход которого соединен с управляющим входом таймера, синхровход коммутатора соединен с синхровходом устройства, причем блок промежуточного накопления тестов содержит два узла регистровой памяти, буферный регистр, схему поразрядного сравнения, генератор частоты опроса,три коммутатора, четыре счетчика, два дешифратора нуля, Триггер, четьфе элемента И, формирователь импульса, два элемента 2И-ИЖ и группу элементов ИЛИ, причем первая группа информационньгх вход ов блока промежуточного накопления тестов соединена с группой информационных входов буферного регистра, информационными входами первой группы входов схемы поразрядного сравнения и первыми группами информационных

А53 .14

входов первого и второго узлов регистровой памяти, вторая группа информационных входов блока промежуточного накопления тестов соединена с cooтвeтcтвyющи и вторыми группами информационных входов первого и второго узлов регистровой памяти, вход синхронизации блока промежуточного

Q накопления тестов соединен с счетным входом триггера, вход разрешения блока промежуточного накопления тестов соединен с первым входом первого элемента И, второй вход которого сое5 динен с выходом первого элемента 2И-ШШ, выход первого элемента И соединен с входом запуска формирователя импульсов, выход которого соединен с вторым выходом блока проме20 жуточного накопления тестов и первыми входами второго и третьего элементов И, прямой выход триггера соединен с первым управляющим входом первого, второго и третьего коммутаторов, с

5 вторым входом третьего элемента И и первыми входами первых групп входов первого и второго элементов 2И-ШШ, инверсный выход триггера соединен с вторыми управляющими входами первого,

д второго и третьего коммутаторов, вторым входом второго элемента И и первыми входами вторых групп входов первого и второго элементов 2И-ИЛИ, выходы буферного регистра соединены с информационными входами второй группы входов схемы поразрядного сравнения, выход Не равно которой соединен . с первым входом четвертого элемента И, выход генератора частоты опроса соединен с вторым входом четвертого элемента И, выход которого соединен с входом разрешения записи буферного регистра, информационным входом первого коммутатора, первый и второй выходы которого соединены соответственно с входом разрешения записи первого и второго узлов регистровой памяти и входами сумьшрования первого и второго счетчиков, выход второго элемента И соединен с соответствукяцими входами вычитания первого счетчика, входом суммирования третьего счетчика и входом разрешения считьшания первого узла регистровой памяти, выход третьего элемента И соединен с входом

вычитания второго счетчика, входом суммирования третьего счетчика, входом разрешения считывания второго узла регистровой памяти, разрядные

5

0

5

0

15

1513453

выходы первого счетчика адреса соединены с соответствуюп1ими информационными BxoAaNm первого дешифратора нуля и первой группой информационных входов второго коммутатора, вторая группа информационных входов которого соединена с разрядными выходами третьего счетчика, разрядные выходы второго счетчика соединены с соответствующими информационными входами второго дешифратора нуля и первой группой информационных входов третьего . коммутатора, вторая группа информационных входов которого соединена с разрядными выходами четвертого счетчика, инверсные выходы первого и второго дешифраторов нуля соединены соответственно с вторыми входами первой и второй групп входов первого элемента

16

2И-ИЛИ, прямой выход первого дешифратора нуля соединен с входом установки в О третьего счетчика и вторым входом второй группы входов второго элемента 2И-ИЛИ, прямой выход второго дешифратора нуля соединен с входом установки в О четвертого счетчика и с вторым входом первой группы вхо.. дов второго элемента 2И-ИЛИ, выходы первого и третьего коммутаторов соединены соответственно с адресными входами первого и второго узлов регистровой памяти, выходы которых соединены соответственно с первой и второй группами входов группы элементов ИЛИ, выходы которых являются выходами блока промежуточного накопления тестов, вькод второго элемента 2И-И1Н является вькодом бло.ка промежуточного накопления тестов.

5

0

f3

20Ф иг.

| Устройство для формирования тестов | 1974 |

|

SU477413A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования тестов субблока логического блока | 1983 |

|

SU1088000A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1987-04-08—Подача