РЬвестны устройства, цикловой синхронизации для систем передачи двоичной информации, содержащие блок поиска синхроимпульса на линии задержки, циклическом счетчике и логических схемах.

Предлагаемое устройство отличается от известных тем, что, с целью повышения помехоустойчивости устройства синхронизации, оно содержит блок повышения достоверности, первый вход которого подключен к выходу счетчика, второй вход которого подсоединен к выходу логических, схем, один из выходов связан с линией задержки.

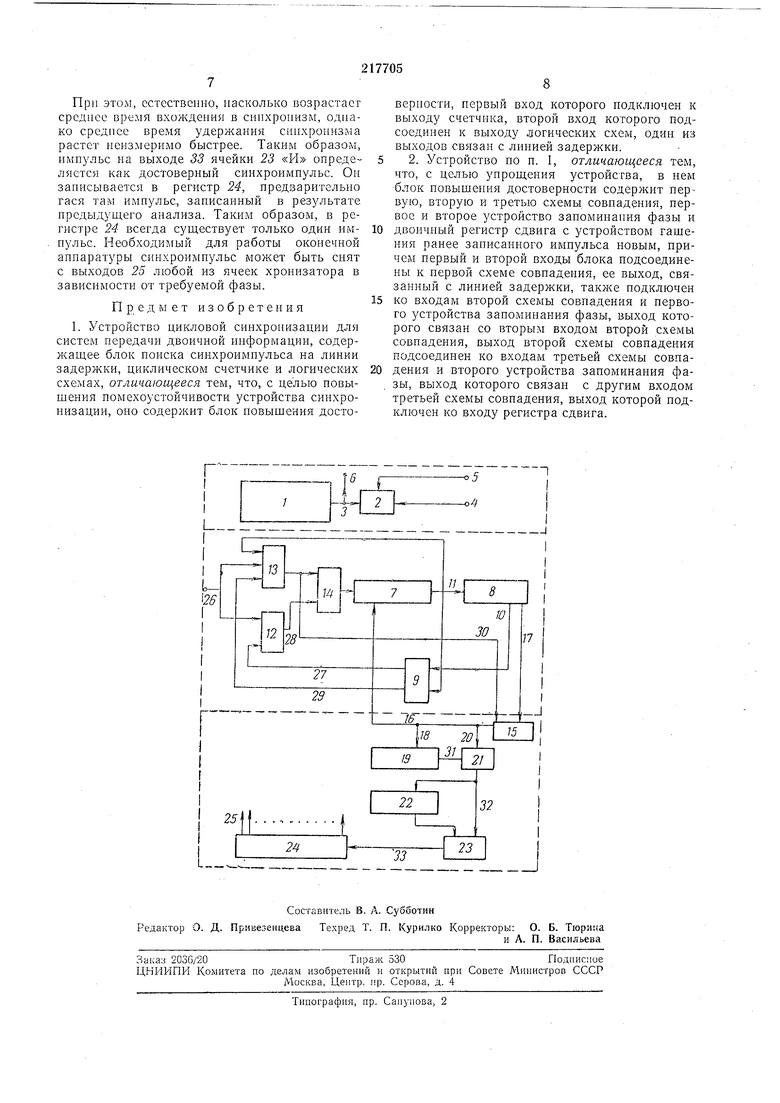

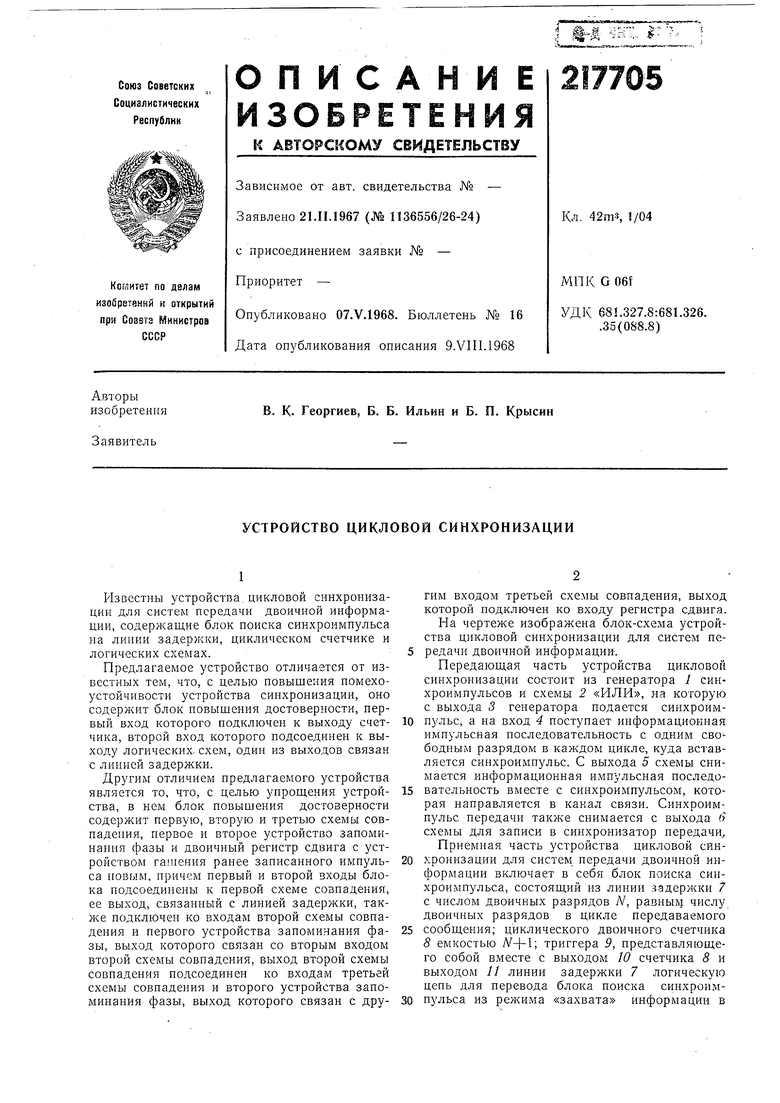

Другим отличием предлагаемого устройства является то, что, с целью упрощения устройства, в нем блок повышения достоверности содержит первую, вторую и третью схемы совпадения, первое и второе устройство запоминания фазы и двоичный регистр сдвига с устройством ганшяия ранее записанного импульса новым, причем первый и второй входы блока подсоединены к первой схеме совпадения, ее выход, связанный с линией задержки, также подключен ко входам второй схемы совпадения и первого устройства запоминания фазы, выход которого связан со вторым входом второй схемы совпадения, выход второй схемы совпадения подсоединен ко входам третьей схемы совпадения и второго устройства запоминания фазы, выход которого связан с другим входом третьей схемы совпадения, выход которой подключен ко входу регистра сдвига. На чертеже изображена блок-схема устройства цикловой синхронизации для систем передачи двоичной информации

Передающая часть устройства цикловой синхронизации состоит из генератора / синхроимпульсов и схемы 2 «ИЛИ, на которую с выхода 3 генератора подается синхроимпульс, а на вход 4 поступает информационная импульсная последовательность с одним свободным разрядом в каждом цикле, куда вставляется синхроимпульс. С выхода 5 схемы снимается информационная импульсная последовательность вместе с синхроимпульсом, которая направляется в канал связи. Синхроимпульс передачи также снимается с выхода 6 схемы для записи в синхронизатор передачи Приемная часть устройства цикловой синхронизации для систем передачи двоичной информации включает в себя блок поиска синхроимпульса, состоящий из линии задержки 7 с числом двоичных разрядов yV, равным числу двоичных разрядов в цикле передаваемого

сообщения; циклического двоичного счетчика 8 емкостью //+1; триггера Р, представляющего собой вместе с выходом 10 счетчика 8 и выходом 11 линии задержки 7 логическую цепь для перевода блока поиска синхроимрежим поиска синхроимпульса; ячейки 12 «И, через которую производится заполпение линии задержки 7 информациоппой последовательпостью (в режиме «захвата); ячейки 13 «И, предпазпаченной для операции поиска сипхроимпульса; разделительной ячейки 14 «ИЛИ. Блок повышения достоверности выделения синхроимпульса состоит из логической ячейки 15 «И, служащей для сравнения с сигналом в принимаемой последовательности фазы импульса, выделенного схемой и предполагаемого синхроимпульсом, с тремя выходами (выход 16 - для переключения всего устройства из режима поиска синхроимпульса в режим «захвата информации после выделения первого импульса выходом 17 счетчика 5; выход 18 - для записи выделенного синхроимпульса в устройство 19, запоминающее его фазу; выход 20, импульс которого в логической ячейке 21 «И сравнивается по фазе с импульсом, выделенным в результате предшествующего анализа); устройств памяти 19 и 22, запоминающих фазу выделенных импульсов, предполагаемых синхроимпульсами; ячеек 21 и 23 «И, соединенных последовательно и сравнивающих фазы импульсов, записапных в устройствах 19 и 22, с фазой вновь выделенного импульса, синхронизатора, выполненного в виде двоичного регистра 24 сдвига с числом разрядов Л и устройством гашения ранее записанного синхроимпульса вновь выделенным, который переписывается в регистр и с выходов 25 может быть снят с любой необходимой для работы оконечного устройства фазой.

Задачей приемной части устройства цикловой синхронизации является выделение синхроимпульса из цифровой последовательности, поступающей па его вход.

Метод выделения синхроимпульса в данном устройстве синхронизации основан на выявлении корреляционных связей последовательно в каждом разряде различных циклов. Иными словами, вероятность появления импульса в любом разряде цикла отлична от единицы, кроме разряда, па котором выставляется синхроимпульс. Очевидно, что путем многократного логического умножения символов одного и того же разряда носледовательно nocTyjiaющих из канала связи циклов, можно добиться того, что в конце концов «единица останется только в одном разряде. Эта «единица будет соответствовать позиции синхроимпульса, поскольку при отсутствии помех в канале связи последний всегда находится на одном и том лее разряде ряда последовательных циклов и потоке двоичной информации. Рассмотрим работу схемы. При включении передающей части устройства генератор 1 синхроимпульсов вырабатывает импульсы, следующие с частотой повторения циклов. С выхода 3 генератора синхроимпульсы поступают на схему 2 «ИЛИ. На другой вход 4 схемы 2 «ИЛИ подается информационная двоичная последовательность со свободным разрядом, в который вставляется синхроимнульс. С выхода 5 схемы 2 информация, разбитая па циклы синхроимпульсом, поступает в канал связи. С выхода 6 генератора / синхроимпульсы поступают иа 5 передающее устройство для его фазирования. Принцип работы приемной части устройства цикловой синхронизации рассматривается ниже.

Предполагается, что в работе приемпого и 10 передающего устройств рассматриваемой системы цикловой синхронизации одним из известных снособов достигнута синхронизация по тактам. Положим в начале, что схема включена, но на ее вход 26 информация не посту15 пает. Благодаря этому линия задержки 7 очищается от «единиц. Пиклический счетчик 8, имеющий емкость A+l, считает «нули. По скольку с выхода 11 линии задержки на вход счетчика 8 поступает пенрерывная последова0 тельность «нулей, то он насчитывает (/V-J-1) «нуль и возвращается в исходное состояние. Таким образом, па выходах 10 и 18 счетчика 8 с частотой возникают импульсы (здесь f - тактовая частота). Импульс с вы5 хода 10 счетчика 8 устапавливают триггер 9 так, что его выход 27 подготавливает ячейку 12 «И к работе.

Поскольку на вход 26 схемы информация не поступает, то с выхода 28 ячейки 12 «И 0 па схему 14 «ИЛИ подаются одни «нули.

Противоположный (нулевой) выход 29 триггера 9 подап ia вход ячейки 13 «И, благодаря этому ячейка 13 «И закрыта.

На выходе ячейки 15 «И импульсы не по5 являются, так как она открывается только по одному входу 17. Такое состояние схемы будем считать исходным.

Пусть теперь на вход 26 схемы поступает импульсная последовательность. Эта последо0 вательность разбита на циклы синхроимпульсом. Заметим, что в исходном состоянии ячейка 12 «И подготовлена по входу 27 триггером 9. Импульсы поступают из канала связи на вход 26 схемы и подаются к ячейкам 12 и 5 13 «И. Так как ячейка 13 «И закрыта с выхода 29 триггера 9, то импульсы проходят через ячейку 12 «И, ячейку 14 «ИЛИ и заполняют линию 7 задержки, имеющую емкость Л . Линия 7 задержки выполнена в виде сдвигаю0 щего регистра. Импульсная последовательность, заполняя линию задержки, продвигается по ней от начала к концу. При появлении импульса на выходе 11 линии 7 задержки триггер 9 переводится в противоположное сос5 тояние. При этом триггер 9 открывает по одному входу ячейку 13 «И, подготавливая ее к работе, и закрывает ячейку 12 «И.

В этот момент линия задержки 7 заполнена информацией, равной но объему одному циклу. Теперь схема приступает.к многократному логическому умножению, о котором упоминается выше. ветствующих позиции иослсдующего осуществляет ячейка 13 «И, исиользуя в качестве сомножителей информацию, храиящуюся в линии задержки 7 и поступающую на вход 26 из канала связи. Таким образом, в линии задержки после логического умножения символов, находящихся в ней в предыдущем цикле, на символы последовательиости, пост шающей в последующий цикл из канала связи, остается все меньще и меньще «единиц. Эта операция повторяется до тех нор, пока в линии задержки останется единственная «единица. В процессе логического умножения имнульсы с выхода // лимии задержки воздействуют на циклический двоичный счетчик 5. Каждым приходящим импульсом с выхода У/ счетчик возвращается в исходное состояние. Емкость счетчика yV-|-l. Пока в линии задержки содержится больше одной «едииицы, счетчик не может насчитать //-нулей, и сигнал на его выходе 18 отсутствует. Когда в линии задержки останется только одна «единица, на выходе 17 счетчика 8 ноявляется импульс, который поступает на вход ячейки 15 «И. На второй вход ячейки 15 «И подается канальный импульс с ячейки 13 «И. В случае их совпадения на выходе ячейки 15 «И появляется импульс, который с извеетной достоверностью можно ечитать синхроимпульсом. Очевидно, что при отсутствии помех в канале связи систему синхронизации можно было бы считать законченной циклическим счетчиком 8, и импульс на его выходе 17 с достоверностью, равной единице, можно было бы полагать синхроимпульеом. Задача достоверного выделения синхроимпульса существенно усложняется из-за наличия помех в канале связи. В этом случае на выходе 17 цикличеекого счетчика 8 могут появляться импульсы, не совпадающие по фазе с переданным синхроимнульсом. В дальнейшем будем их называть синхроимпульсами. При возрастании ошибок в канале вероятность ложного синхроимпульса увеличивается, что нрнводит к сокращению времени удержания синхронизма fy, являющегося одним из основных параметров любой системы синхронизации. С целью предотвращения этого устройство силхронизации дополняется блоком повыщения достоверности выделения синхроимпульса. Работа ее сводится к следующему. Импульс с выхода 18 ячейки 15 «И, который предположительио считается синхроим пульсом, записывается в запоминающее его фазу устройство 19, выполненное в виде рекур рентной линии задержки с числом состояний N, и остается там до нрихода следующего им нульса с ячейки 15 «И. Одновременно нм пульс с выхода 16 ячейчи 15 «И подается на линию задержки 7 и гасит единственную «единицу, находящуюся в ней. ителыю, благо;|.аря тому, что находящаяся в инии 7 задержки единица погашена, цикличекий счетчик 8 насчитывает «нулей, и а его выходе 10 появляется импульс, который еребрасывает триггер 9. В результате ячейка 3 «И закрывается, а ячейка 12 «И подгоавливается к работе. Линия 7 задержки заолняется новой порцией информации, нровигающейся от ее начала к концу. Ячейка 12 И открыта до тех пор, пока па выходе 11 ипии задержки не ноявитея импульс, перераеывающий триггер 9. Триггер 9 открывает чейку 13 «И и закрывает ячейку 12 «И. хема переходит в режим иоиска синхрон.мнульса, т. е. нрнступает к поразрядному логическому умножению, как было описаио выше. Когда в линии задержки 7 останется одна «единица, на выходе /7 счетчика 6 появляется импульс. Если в этот же момент на входе 30 ячейки 15 «И также возникает имнульс, то с ее выхода импульс поступит н на вход ячейки 21 «И. Этот же импульс гасит «единицу в линии 7 задержки и перезаписывается в запоминающее устройство 19, до этого сфазированное синхроимпульсом, выделенным в результате предыдущего аналнза. Имнульс с выхода 31 запоминающего устройства 19 подастся на вход ячейки 21 «PI. Если он совпал с импульсом па входе 20, то ячейка 21 «И генерирует импульс, который записывается в запоминающее устройство 22, аналогичное с устройством J9. Запись импульса в запоминающее устройство 22 произойдет в результате выделения подряд двух нмпульеов с одипаковой фазой. Иными словами, ячейка 21 «И генерирует импульс лишь в случае, когда на выходе ячейки 15 «И выделяется имнульс два раза подряд с одинаковой фазой. Значит, для установления ошибочной синхронизацнн еобходимо двукратное (и подряд) выделение ложных синхроимнульсов, обязательно соответствующих одному н тому же разряду цикла. По аналогии ячейка 23 «И генерирует импульс только в том случае, когда с выхода 17 счетчика 8 три раза подряд выделится имнульс, соответствующий одному и тому же разряду в цикле. Такие узлы, т. е. запоминающее устройство 19 с ячейкой 21 «И и запоминающее устройство 22 с ячейкой 23 «И, резко увелнчивают отношение Рд1Рл где Рд н Яд - соответственно вероятности достоверного н ложного выделения еинхроимнульсов. Это соотношение на выходе 32 схемы имеет норядок (Рд1Ру, а на выходе 16 - порядок (Р /Р лЫ-2, где рд и Р - соответственно вероятности достоверного н ложного выделения синхроимпульса схемой ноиска (на выходе /7 счетчика 8). Наращивая количество устройств, заномннающих фазу, и ячеек «И можно нолучить любое заданное соотношенне Рд/Рл и, как результат, любое требуемое зиачение среднего

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1971 |

|

SU321809A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Устройство для цикловой синхронизации | 1979 |

|

SU866772A1 |

| Цифровая линия задержки | 1987 |

|

SU1499451A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОКОВ ИНФОРМАЦИИ | 2003 |

|

RU2249920C2 |

| Устройство цикловой синхронизации | 1974 |

|

SU542991A2 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ УСТРОЙСТВ | 1970 |

|

SU267188A1 |

Даты

1968-01-01—Публикация