Известны устройства для .построения цифровых вычислительных устройств, содержащие регистр, счетчик и логические элементы.

Предлагаемый вычислительный элемент для построения цифровых вычислительных устройств отличается от известных тем, что в нем входы схемы совпадения подключены к выходам регистра и счетчика, выполненных на магнитострикционных линиях задержки, к выходу триггера, вход которого подключен к выходу сумматора. Это позволяет сократить количество оборудования.

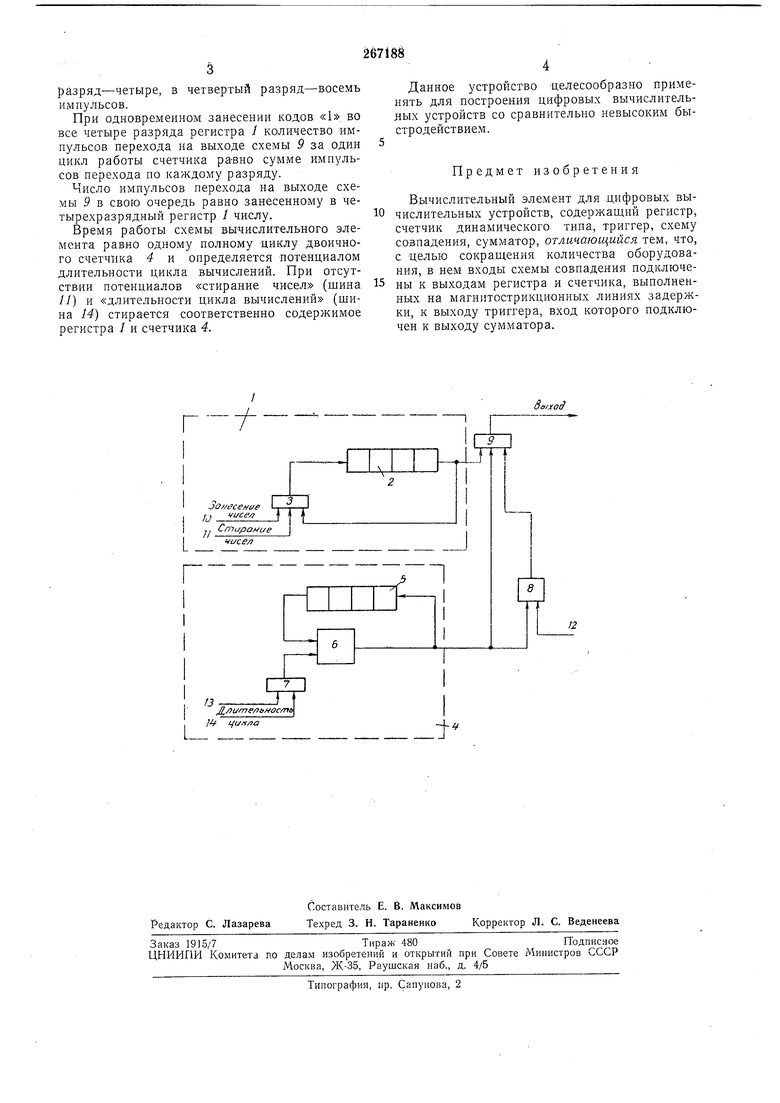

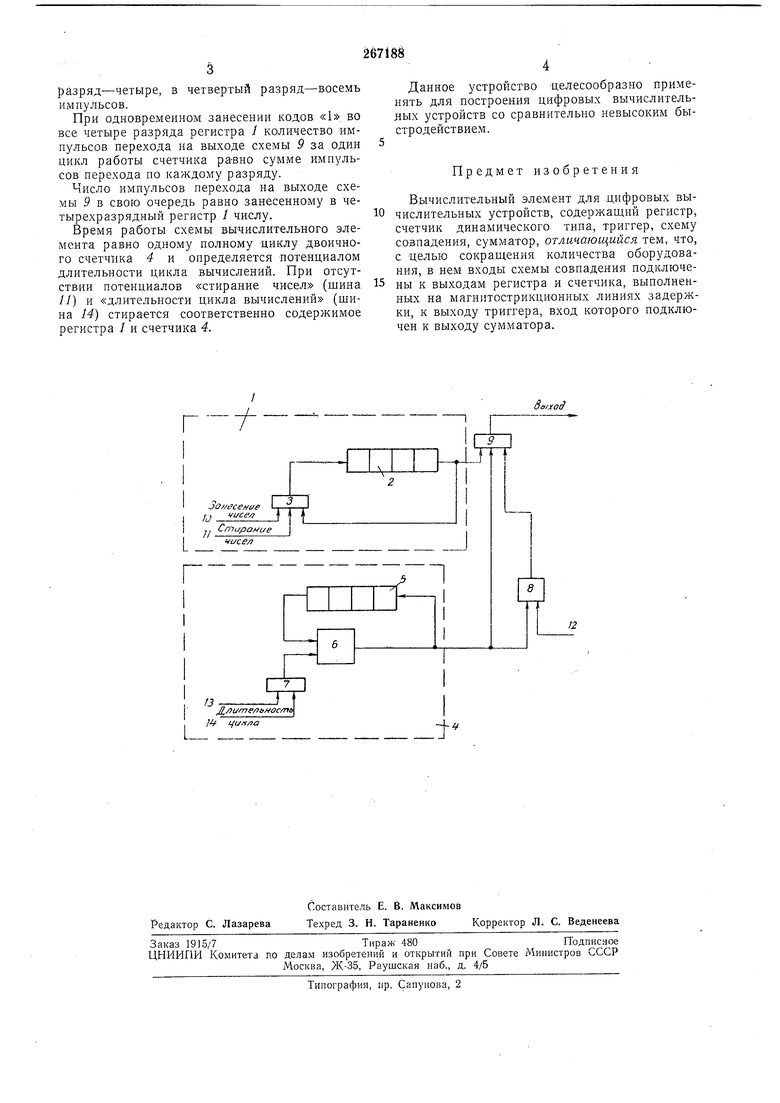

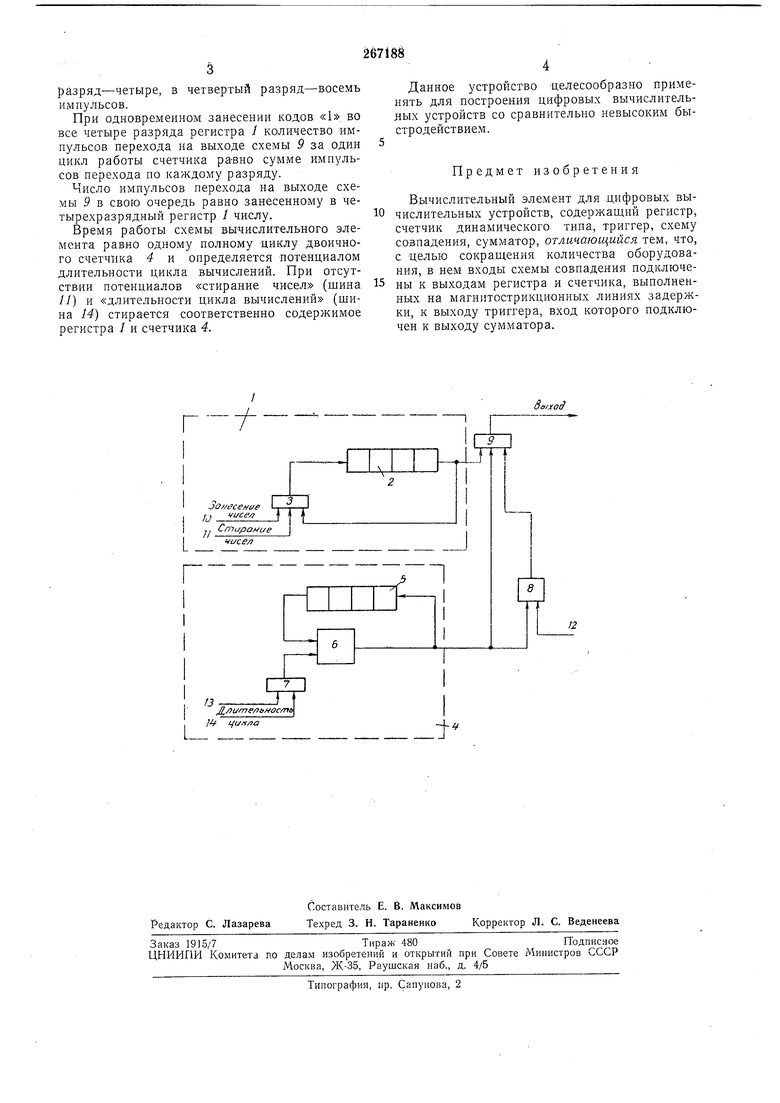

На чертеже представлена функциональная схема вычислительного элемента на динамических линиях задержки для построения цифровых вычислительных устройств.

Вычислительный элемент содержит регистр / на магнитострикционной линии 2 задержки и схеме 3 совпадения, счетчик 4 на магнитострикдионной линии 5 задержки, сумматоре 6 и схеме 7 совпадения, триггер 8 и схему 9 совпадения, шины W-14 входных сигналов. Для наглядности магнигострикционные линии задержки 2 и 5 условно разделены на несколько разрядов. Устройство работает следующим образом.

ские операции. При ручном вводе данных вместо потенциалов регистра / могут быть использованы потенциалы кодов числа, набираемого непосредственно на клавищах. После этого потенциалом длительности цикла вычислений по щине 13 разрещается счет импульсов, поступающих в счетчик 4 через схему 7 совпадения. Потенциалы регистра 1, счетчика 4 и триггера 8 подаются на вход схемы 9. При совпадении низких уровней (кодов единиц) этих сигналов на выходе схемы поЯвляется сигнал. Количество импульсов на выходе схемы 9 равно числу, занесенному в регистр 1. Потенциалы разрядов- регистра /,

содержащих код «О, запрещают образование сигналов на выходе схемы 9. Схема 9 пропускает только первый значащий разряд содержимого счетчика 4, так как этим же сигналом триггер 8 переводится в единичное состояние,

и его потенциал запрещает образование сигналов на выходе схемы 9 до установки триггера 8 по шине 12 «О очередным сигналом, поступающим после каждого сигнала щины 13. Па входе схемы 9 младшие разряды счетчика 4 клапанируются старшими разрядами регистра 1. В результате при занесении в первый разряд регистра кода «1 на выходе схемы 9 появляется один импульс перехода за полный цикл работы счетчика 4, при занесеразряд-четыре, в четвертый разряд-восемь импульсов.

При одновременном занесении кодов «1 во все четыре разряда регистра 1 количество имнульсов перехода на выходе схемы 9 за один цикл работы счетчика равно сумме импульсов перехода по каждому разряду.

Число импульсов перехода на выходе схемы 9 в свою очередь равно занесенному в четырехразрядный регистр 1 числу.

Время работы схемы вычислительного элемента равно одному полному циклу двоичного счетчика 4 и определяется потенциалом длительности цикла вычислений. При отсутствии потенциалов «стирание чисел (шина 11} и «длительности цикла вычислений (шина 14) стирается соответственно содержимое регистра / и счетчика 4.

Данное устройство целесообразно применять для построения цифровых вычислительлых устройств со сравнительно невысоким быстродействием.

Предмет изобретения

Вычислительный элемент для цифровых вычислительных устройств, содержащий регистр, счетчик динамического типа, триггер, схему совпадения, сумматор, отличающийся тем, что, с целью сокращения количества оборудования, в нем входы схемы совпадения подключены к выходам регистра и счетчика, выполненных на магнитострикционных линиях задержки, к выходу триггера, вход которого подключен к выходу сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПЕЦИАЛИЗИРОВАННОЕ ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU408304A1 |

| УСТРОЙСТВО для ВЫЧИТАНИЯ ДВУХ чист | 1970 |

|

SU278221A1 |

| ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1961 |

|

SU135700A1 |

| ВЫЧИСЛИТЕЛЬНАЯ МАШИНА ДЛЯ РАСКРОЯ МАТЕРИАЛА | 1970 |

|

SU287807A1 |

| УСТРОЙСТВО для ПОСТРОЕНИЯ КОРНЕВЫХ ГОДОГРАФОВ СИСТЕМ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 1973 |

|

SU397914A1 |

| УСТРОЙСТВО ДЛЯ ВРЕМЕННОГО СЖАТИЯ ВХОДНОГО СИГНАЛА | 1971 |

|

SU428544A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННОГО ИНТЕРВАЛА | 1991 |

|

RU2040854C1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

1

Авторы

Даты

1970-01-01—Публикация