Известные устройства для обнаружения ошибок в избыточных кодах основаны на выявлении ошибочных комбинаций.

Предлагаемое устройство предназначено для обнаружения ошибок в двоично-десятичном коде с избытком три в машине последовательного действия и отличается от известных тем, что оно выполнено на пяти ферротранзисторных ячейках, четыре из которых образуют попарным объединением устройства совпадения, а пятая обмотка используется как элемент памяти; входы старших разрядов соединены с обмотками записи первой схемы совпадения; вход первого разряда соединен с обмоткой записи пятой ячейки, а вход второго разряда - с обмоткой считывания пятой ячейки; причем обмотка опроса размещена на всех ячейках, кроме первой, а выходные обмотки устройств совпадения объединены.

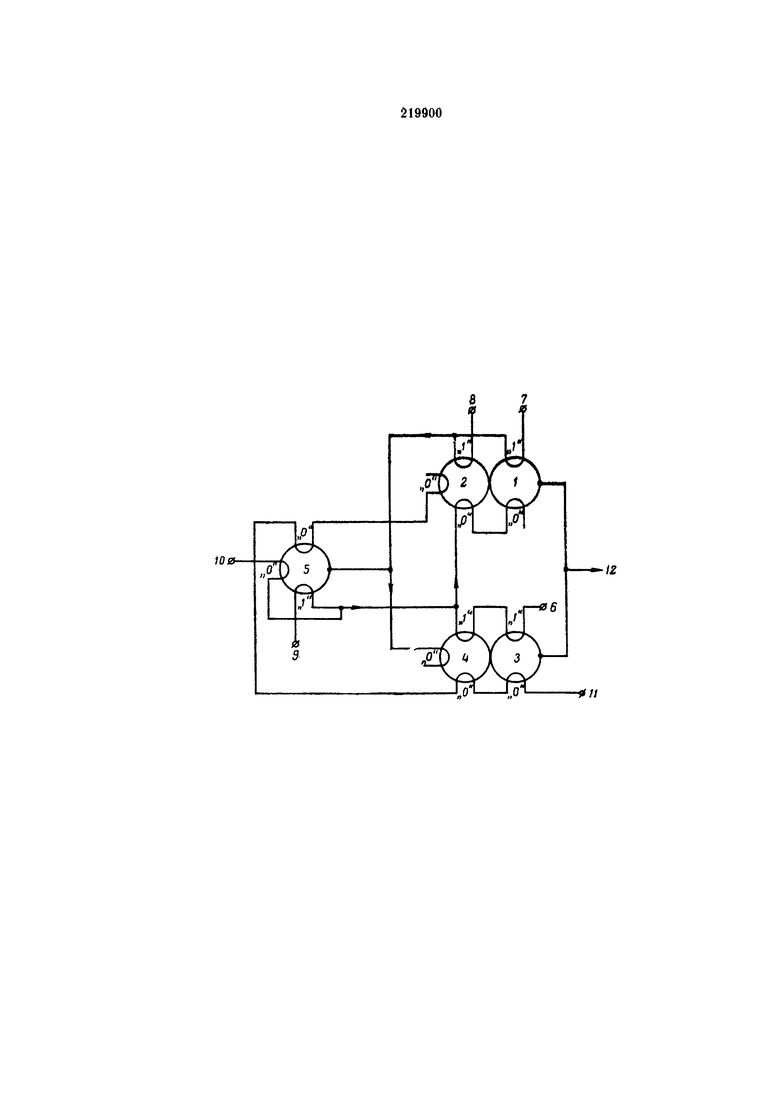

На чертеже дана принципиальная схема устройства.

Устройство контроля выполнено на пяти ферротранзисторных ячейках 1-5. Для обнаружения запрещенных комбинаций одного разряда они объединены в логическое устройство, состоящее из двух схем совпадения. Схемы совпадения образованы соответственно ячейками 1, 2 и 3, 4 и элементом памяти на ячейке 5.

Известно, что числа в коде с избытком 3 кодируются следующим образом: 0-0011, 1-0100, 2-0101, 3-0110, 4-0111, 5-1000, 6-1001, 7-1010, 8-1011 и 9-1100. Предлагаемое устройство обнаруживает все 6 неправильных кодовых комбинаций 0000, 0001, 0010, 1101, 1110, и 1111.

Устройство работает следующим образом.

По первому такту на вход 6 подается тактовый импульс, устанавливающий ячейки 1 и 2 в «0», а остальные ячейки - в «1». Во втором такте на входы 7 и 8 поступают импульсы третьего и четвертого разрядов соответственно (действие этих и других управляющих импульсов показано на чертеже символами «0» и «1»). В третьем такте на вход 9 приходит импульс первого (младшего) разряда, который записывает «1» на ячейке 5 и считывает информацию с первой схемы совпадения. По четвертому такту на вход 10 поступают импульсы второго разряда и считывают информацию с ячейки 5. При этом выходной импульс с ячейки 5 поступает на вторую схему совпадения как импульс запрета. По пятому такту считывается информация с ячеек 2, 3, 4 и 5 импульсом, поступающим на вход 11. Возникающие при этом сигналы схем совпадения поступают на выход 12 и сигнализируют об ошибочной комбинации.

Вторая схема совпадения обнаруживает первые три из описанных выше ошибочных комбинаций, а первая - остальные три комбинации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обнаружения ошибок | 1964 |

|

SU475624A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ И ОБНАРУЖЕНИЯ МНОГОКРАТНЫХ ОШИБОК | 1967 |

|

SU206169A1 |

| Двоично-десятичный счетчик | 1977 |

|

SU702530A1 |

| Дешифратор | 1974 |

|

SU572922A1 |

| БИБЛИОУТ'КД . ^ | 1973 |

|

SU362302A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙКОМБИНАЦИИ | 1971 |

|

SU293243A1 |

| СИНХРОНИЗАТОР ДЛЯ МНОГОТАКТНЫХ ФЕРРОТРАНЗИСТОРНЫХ СИСТЕЛ1 С РАЗНОВРЕМЕННЫЛ1ЗАПРЕТОМ | 1970 |

|

SU273517A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОДИНОЧНЫХ и ОБНАРУЖЕНИЯ МЯОЮКРАТНЫХ ОШИБОК | 1967 |

|

SU196441A1 |

| УСТРОЙСТВО для ЭКСПЕРИМЕНТАЛЬНОГО ИССЛЕДОВАНИЯ | 1971 |

|

SU297963A1 |

Устройство для обнаружения ошибок в разряде с избыточным кодированием, выполненное по способу выявления ошибочных комбинаций, отличающееся тем, что, с целью обнаружения ошибочных комбинаций двоично-десятичного кода с избытком трех оно выполнено на пяти ферротранзисторных ячейках, четыре из которых образуют попарным объединением два устройства совпадения, пятая используется как элемент памяти, входы обоих старших разрядов соединены с обмотками записи первой схемы совпадения и обмоткой запрета второй схемы совпадения, вход одного из младших разрядов соединен с обмоткой записи пятой ячейки, а вход другого - с обмоткой считывания, причем оба входа соединены с обмотками считывания первой схемы совпадения, выход пятой ячейки соединен с обмоткой запрета второй схемы совпадения, обмотки стирания пятой ячейки и второй схемы совпадения соединены с обмоткой запрета первой схемы совпадения, а выходы обеих схем совпадения объединены.

Авторы

Даты

1968-09-06—Публикация

1964-02-26—Подача