Известны устройства для получения импульсов, сдвинутых во времени на две третьих их длительности, содержащие триггеры импульсно-потенциальные схемы совпадения и усилители.

Предложенное устройство отличается от известных тем, что выход каждого триггера через импульсно-потенциальную схему совпадения и усилители соединен с управляющими входами последующего триггера.

Это позволяет упростить предлагаемое устройство и повысить его быстродействие.

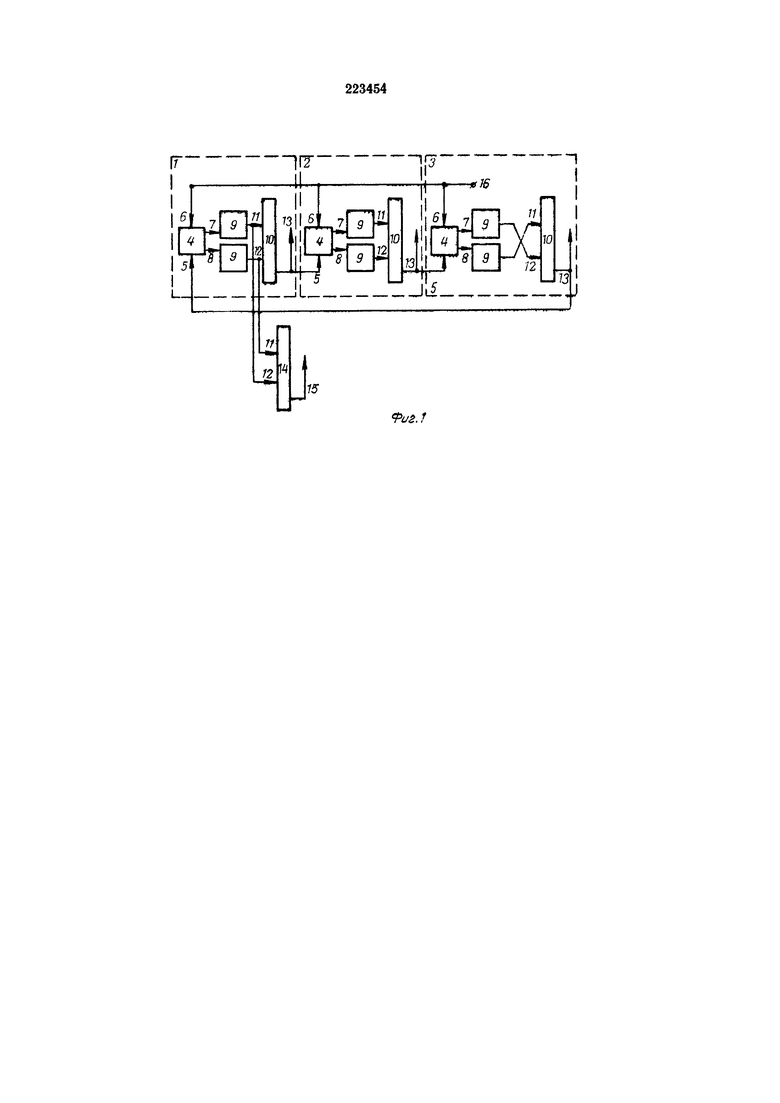

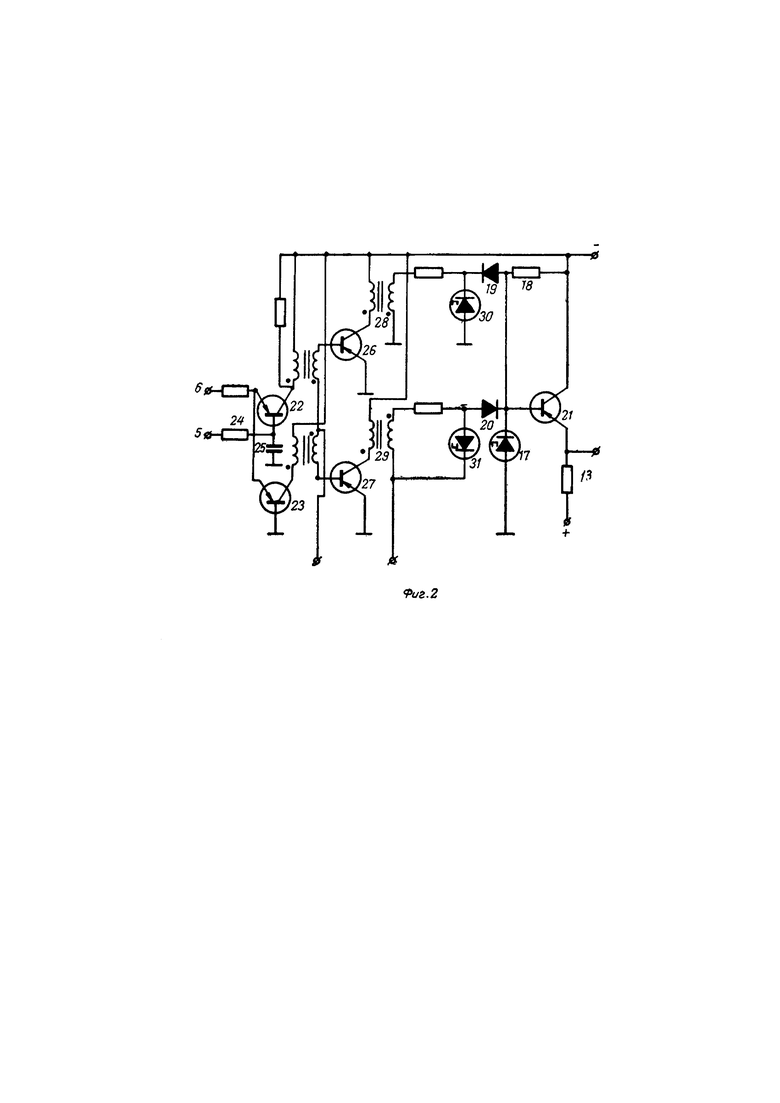

На фиг. 1 изображено предлагаемое устройство; на фиг. 2 - то же, электрическая схема.

Устройство состоит из ячеек 1-3. Каждая ячейка состоит из парафазного вентиля 4, имеющего управляющий вход 5, импульсный вход 6, единичный выход 7 и нулевой выход 8. На единичном выходе 7 вентиля появляется импульс при наличии импульса на входе 6 и разрешающего (I) потенциала на входе 5; на нулевом выходе 8 вентиля импульс появляется при наличии импульсов на входе 6 и запрещающего (0) потенциала на входе 5. Ячейка имеет также два усилителя 9, усиливающие выходные импульсы парафазного вентиля и вносящие дополнительную необходимую задержку импульсов, триггер 10, включающий в себя кодовый вход установки 11, кодовый вход установки 12 и единичный потенциальный выход 13.

Первая ячейка 1 имеет также дополнительный триггер 14 для получения инверсного потенциального выхода 15.

Ячейки 1-3 включены в кольцо так, что выход 13 каждой предыдущей ячейки управляет входом 5 каждой последующей ячейки. В ячейках 1 и 2 единичный выход 7 парафазного вентиля связан со входом установки (I) триггера 10, а нулевой выход 8 - со входом установки (0) этого триггера.

В ячейке 3 осуществлена перекрестная связь; выход 7 связан со входом 12, а выход 8 - со входом 11.

Входы 11, 12 инвертирующего триггера 14 ячейки 1 также связаны перекрестной связью с выходами вентиля 4 ячейки 1. На шину 16 подаются тактовые импульсы.

В качестве триггеров 10 в устройстве применяются триггеры на туннельных диодах (ТД). Триггер построен на ТД 17, сопротивлении 18, развязывающих диодах кодовых входов 19 и 20; триггер имеет эмиттерный повторитель выходного уровня, построенный на основе транзистора 21. Более отрицательный уровень на выходе 13 триггера соответствует (I), менее отрицательный - (0).

К парафазному вентилю относятся транзисторы 22, 23. Выход транзистора 22 является единичным выходом парафазного вентиля, а выход 23 - нулевым выходом.

Если на управляющий вход 5 подан единичный уровень и ко входу 6 подключается зафиксированный на общую шину импульсный источник напряжения, транзистор 22 открыт.

Транзистор 23 при этом заперт.При поступлении положительного импульса на вход 6 появляется импульс на единичном выходе парафазного вентиля.

Если на управляющем входе 5 (0), транзистор 22 заперт положительным смещением базы относительно эмиттера, а транзистор 23 заперт потому, что потенциал его базы равен потенциалу эмиттера, В результате при поступлении положительного импульса на вход 6 транзистор 23 отпирается и появляется импульс на инверсном выходе вентиля.

Интегрирующая цепь 24, 25 введена в схему вентиля, чтобы не допустить появления помехи на единичном выходе при включении разрешающего уровня на входе 5. Усилители 9 ячеек построены на основе транзистров 26 и 27. К усилителям относятся также трансформаторы 28, 29 и формирующие туннельные диоды 30 и 31. Усилители 9, кроме усиления выходных импульсов, вносят дополнительную необходимую при работе схемы задержку.

Связи между выходами вентиля и кодовыми входами основного триггера, изображенные на фиг. 2, соответствуют осуществляемым в ячейках 1 и 2 неперекрестным связям.

В ячейке 3 для осуществления перекрестной связи трансформатор 28 подключен к коллектору транзистора 27, а трансформатор 29 - к коллектору транзистора 26.

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик случайных двоичных сигналов | 1974 |

|

SU526871A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ M-ФАЗНЫМ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2027294C1 |

| Логическая схема "или-и-не" | 1974 |

|

SU510784A1 |

| ОДНОТАКТИЫЙ РЕГИСТР СДВИГА | 1971 |

|

SU291246A1 |

| Быстродействующий логический элемент или-и-не | 1973 |

|

SU478441A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВУХПОЛЯРНЫХ СИГНАЛОВ В ПОТЕНЦИАЛЬНЫЕ | 1969 |

|

SU247349A1 |

| Устройство задержки сигналов | 1983 |

|

SU1091306A2 |

| РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1972 |

|

SU354586A1 |

| Стабилизированный транзисторный конвертор | 1977 |

|

SU736289A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

Устройство для получения импульсов, сдвинутых во времени на две третьих их длительности, содержащее триггеры, импульсно-потенциальные схемы совпадения и усилители, отличающееся тем, что, с целью упрощения и повышения быстродействия, выход каждого триггера через импульсно-потенциальную схему совпадения и усилители соединен с управляющими входами последующего триггера.

Авторы

Даты

1968-11-13—Публикация

1967-05-10—Подача