В большинстве случаев оптимальная обработка сигналов представляет собой обработку согласованными фильтрами (СФ). Трудности, связанные с использованием линий задержки в аналоговых СФ, привели к созданию цифровых СФ. Функция, в конечном счете аналогичные функциям линий задержки аналоговых и цифровых СФ, выполняются регистрами сдвига. Замена линий задержки регистрами сдвига открыла большие возможности в построении оптимальных (или близких к оптимальным) фильтров. Но и при реализации цифровых СФ возникает необходимость преобразования сигнала в код, выполняемого довольно сложными устройствами. Кроме того, возникает погрешность, связанная с ограниченностью числа уровней квантования. Уменьшение шумов квантования достигается лишь путем увеличения числа уровней квантования, что существенно усложняет преобразователь аналог - код и снижает его быстродействие.

В предлагаемом устройстве, производящем оптимальную аналоговую обработку выборочных значений сигнала (т.е. значений сигнала в равноотстоящие моменты времени), функции линий задержки аналоговых СФ (или регистров сдвига цифровых) выполняет цепочка стробируемых интеграторов. В таком фильтре нет необходимости использовать линии задержки и преобразователи аналог - код. Кроме того, в нем принципиально отсутствуют шумы квантования, а погрешности представления входного процесса связаны лишь с дискретизацией сигнала по времени. В этом смысле описываемый фильтр занимает промежуточное положение между аналоговым и цифровым.

Фильтр отличается от известных тем, что в нем вход первого из интеграторов через ключ подключен ко входу устройства, а вход каждого последующего через ключ соединен с выходом предыдущего, причем выходы нечетных интеграторов подключены ко входу сумматора.

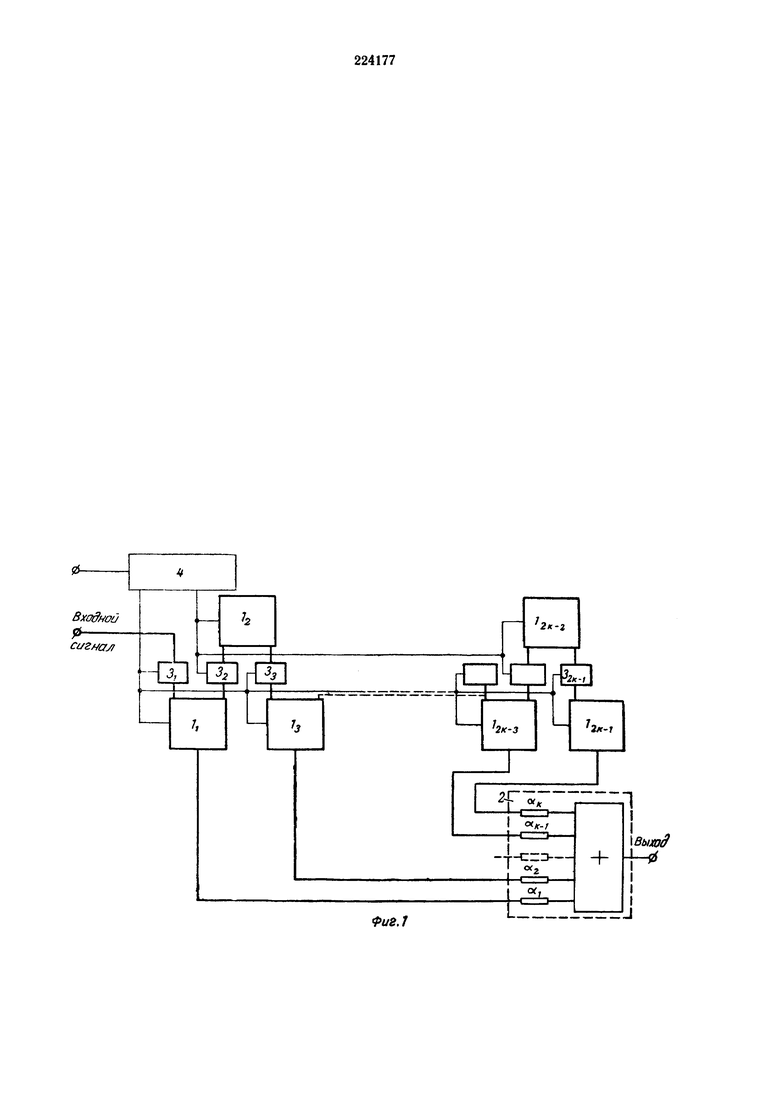

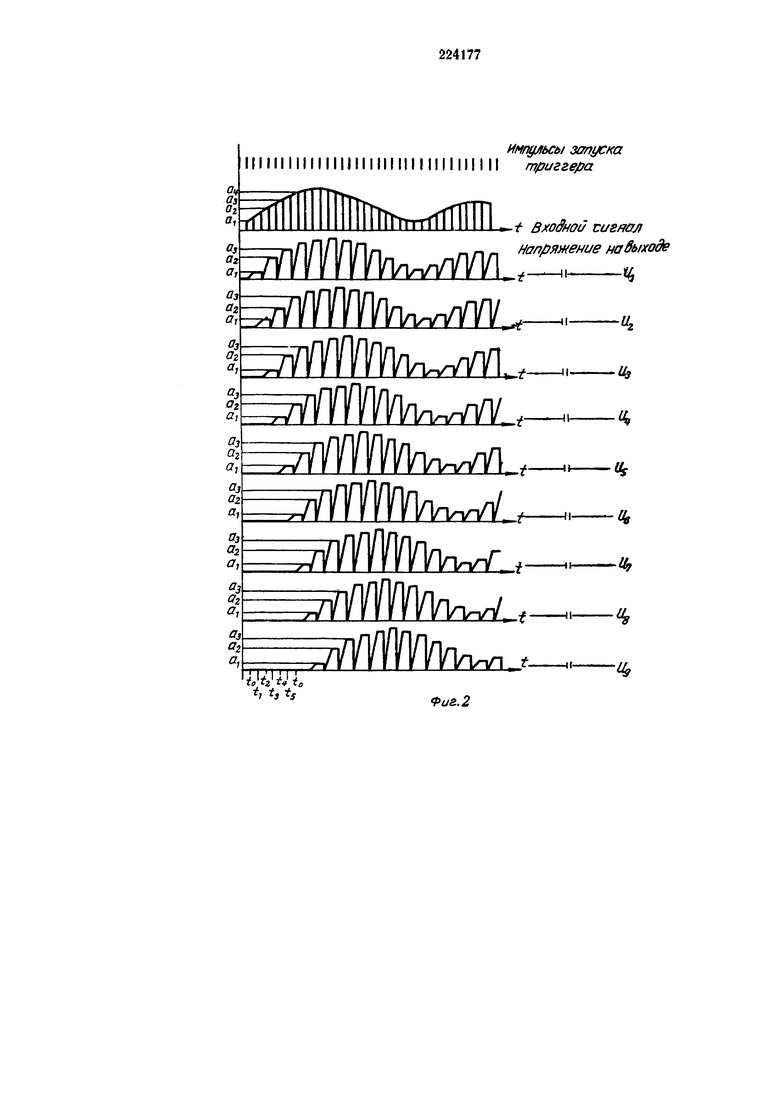

На фиг. 1 приведена блок-схема фильтра; на фиг. 2 - временные диаграммы.

Основным звеном фильтра является цепочка стробируемых интеграторов 11-12K-1 (K - число анализируемых выборок), с которых снимаются и подаются с соответствующими весами на сумматор 2 напряжения, пропорциональные по величине выборочным значениям входной реализации. Процесс прохождения выборок по цепочке интеграторов (см. фиг. 2) осуществляется путем соответствующей коммутации интеграторов при помощи ключей - 31, 32, 33 управляемых импульсами блока 4 управления.

В исходном состоянии в момент времени t0 напряжения на всех интеграторах равны нулю. Ключ 31 открывается импульсом блока 4, На интервале t0, t1 происходит интегрирование входного процесса интегратором 11. Ключ 32 разомкнут, и напряжение на интеграторе 12 продолжает оставаться нулевым. К концу интервала t0, t1 напряжение на интеграторе 11 достигает величины, пропорциональной среднему значению а1 входного процесса на интервале t0, t1. В момент t1 ключ 31 размыкается, и в течение интервала t1, t2 напряжение на выходе интегратора 11 остается постоянным (пропорциональным а1). Ключ 32 на интервале t1, t2 замкнут, и на интеграторе 12 производится интегрирование процесса, протекающего «а выходе интегратора 11. В момент t2 напряжение на интеграторе 12 достигает величины, пропорциональной а1, ключ 32 размыкается, спадом импульса блока 4 сбрасывается напряжение на интеграторе 11, открываются ключи 31 и 33. На интервале t2, t3 напряжение на выходе интегратора 12 остается постоянным, пропорциональным а1, интеграторы 11 и 13 производят соответственно интегрирование входного процесса и процесса на выходе интегратора 12. К концу интервала t2, t3 напряжения на выходах интеграторов 11 и 13 достигают соответственно величин а2 и а1. В момент t3 сбрасывается напряжение на интеграторе 11, чем интегратор 12 подготавливается для записи выборки а2.

В результате этого процесса в течение интервала (t2i+1 t2i+2) на интеграторах 12j-1 поддерживаются соответственно напряжения, пропорциональные значениям выборок ai-j. Эти напряжения с соответствующими коэффициентами αj, определяющими импульсную реакцию фильтра, поступают на сумматор 2.

С выхода сумматора снимаются импульсы, амплитуды которых пропорциональны значениям функции взаимной корреляции входного процесса и ожидаемого сигнала.

Устройство для оптимальной обработки сигналов, содержащее интеграторы, ключи, сумматор и блок управления, отличающееся тем, что, с целью повышения точности и упрощения устройства, в нем вход первого из интеграторов через ключ подключен ко входу устройства, а вход каждого последующего через ключ соединен с выходом предыдущего, причем выходы нечетных интеграторов подключены ко входу сумматора.

Авторы

Даты

1968-11-20—Публикация

1967-06-07—Подача