Изобретение относится IK област)1 преобразования .и кодирования информадии.

Известны устройства для формирования управляющих сигналов аналого-цифрового преобразователя лоразрядното кодирования, содержащие триггеры регистра, «единичные выходы которых, за исключением выхода триггера старщего разряда, соединены со входами одноименных схем совпадения, и -схемы задержки.

Предложенное устройство отличается тем, что ,в «ем «нулевые выходы триггеров регистра, за исключением выхода триггера старшего разряда, соединены со входами им предществующих -схем совпадения, причем выход схемы совладения старщего разряда через схему зад-ержки соединен со (входами схем совладения iB -целях установки «единицы триггеров старшего и следующего за ним разрядов, а .выходы остальных схем совпадения через схемы задержки соединены со входом схемы совпадения в цепи установки «нуля триггера своего разряда, а также со входом схемы совладения в щели установки «единицы триггера -следующего разряда. Это позволяет снизить требования к управляющим импульсам и улростить устройство.

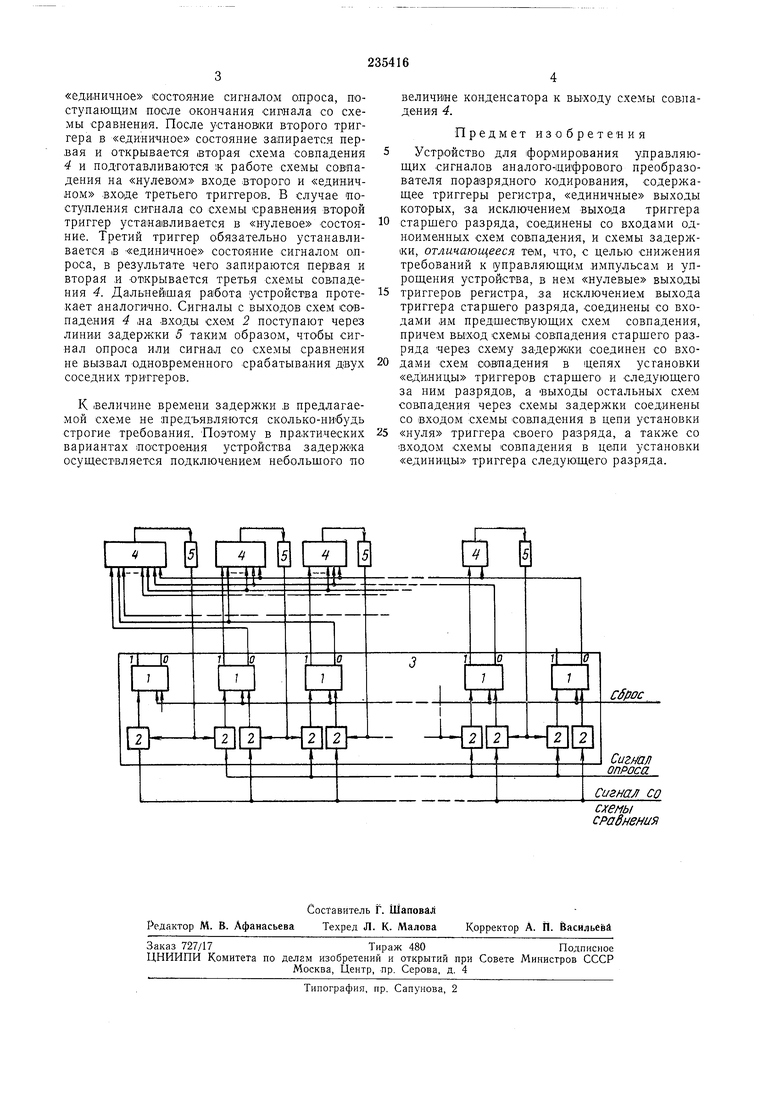

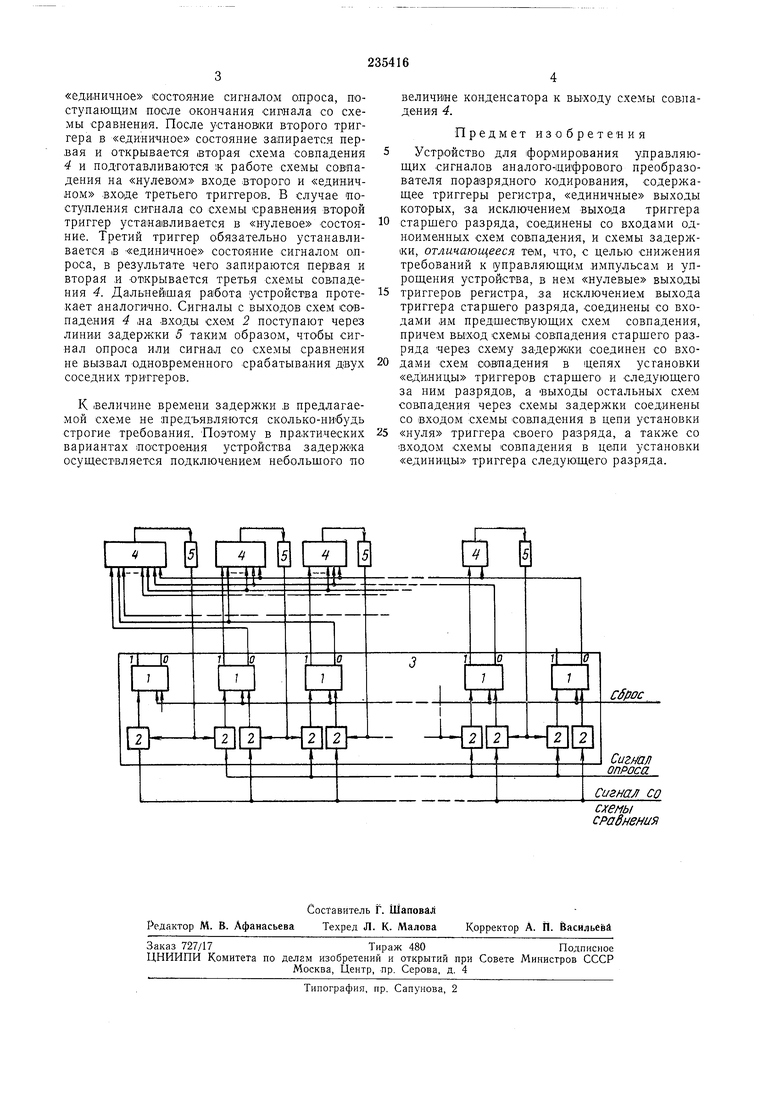

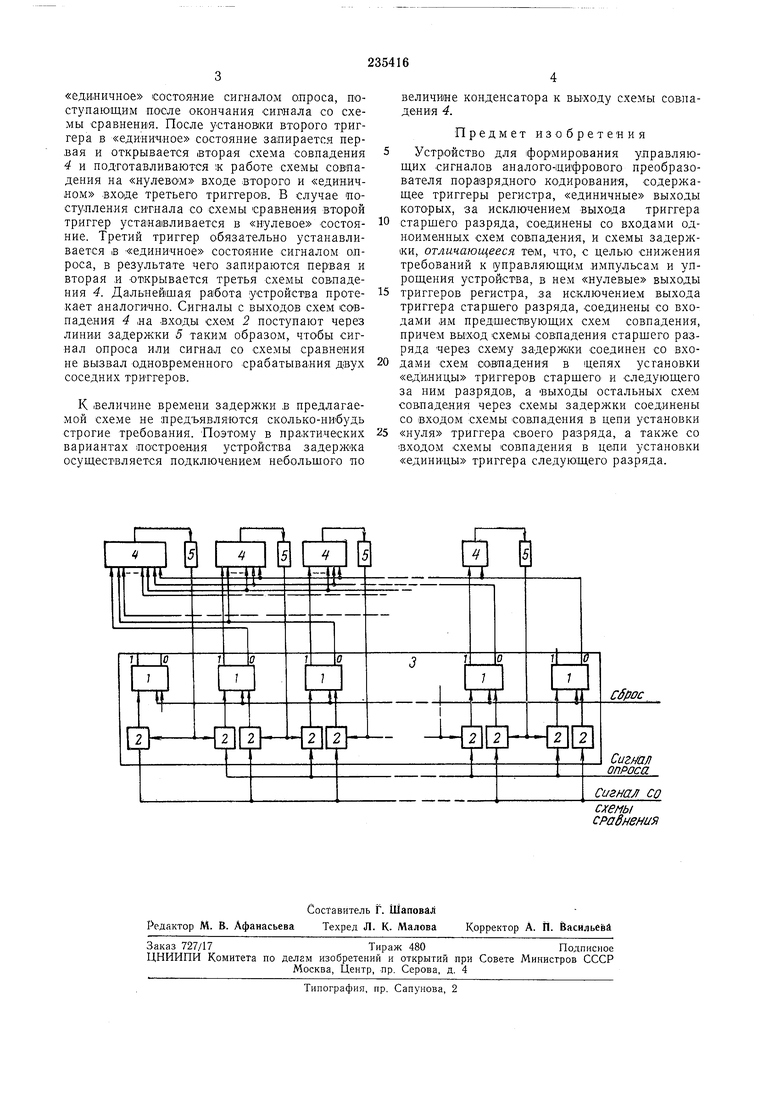

Устройство состоит из регистра на триггерах / со входными схемами совладения 2, которые образуют схему 3 запоминания результата в обычном лреобразователе с лоразрядным Кодированием. Единичные выходы всех триггеров /, кроме лер.вого, соединены со входами только одноименных схем совпадения 4, а «нулевые выходы всех триггеров 1, кроме лервого, соединены со входа-ми всех предществующих схем совпадения 4. Выход схемы совпадения 4 старшего разряда через схему задержки 5 соединен со входами схем совпадения 2 в цепях установки «единицы триггеррвстаршего и следующего за ни.м разрядов,

а выходы остальных схем совладения 4 через схему задержки 5 соединены со входом схемы совпадения 2 в депи установки «нуля триггера одноименного разряда, а также со входом схемы совладения в цепи установки «единицы

триггера следующего разряда.

В исходном состоянии, когда определяется знак входной величины, открыта лишь одна первая схема совладения 4, на входы которой поступают сигналы только с нулевых выходов триггеров. Выходной сигнал этой схемы открывает две схемы совладения 2, -в результате чего первый триггер (знаковый) может быть установлен, если это требуется, в «единичное состояние сигналом с выхода схемы

«единичное состойнне сигналом опроса, постунающим после окончания сигнала со схемы сравнения. После установки второго триггера в «единичное состояние запирается первая и открывается вторая схема совпадения 4 и подготавливаются к работе схемы совпадения на «нулевом входе второго и «единичном .входе третьего триггеров. В случае постулления сигнала со схемы сравнения второй триггер устанавливается в «нулевое состояние. Третий триггер обязательно устанавливается iB «единичное состояние сигналом опроса, в результате чего запираются первая и вторая п открывается третья схемы совпадения 4. Дальнейшая работа устройства протекает аналогично. Сигналы с выходов схем совпадения 4 на входы схем 2 поступают через линии задержки 5 таким образом, чтобы сигнал опроса или сигнал со схемы сравнения не вызвал одновременного срабатывания двух соседних триггеров.

К величине времени задержки в предлагаемой схеме не предъявляются сколько-нибудь строгие требования. Поэтому в пра.ктических вариантах построения устройства задерлжа осуществляется подключением небольшого по

величине конденсатора к вьгаоду схемы совпадения 4.

Предмет изобретения

Устройство для формирования управляющих сигналов аналого-цифрового преобразователя поразрядного кодирования, содержащее триггеры регистра, «единичные выходы которых, за исключением выхода триггера старшего разряда, соединены со входами одноименных схем совпадения, и схемы задержки, отличающееся тем, что, с целью снижения требований к управляющим импульсам и упрощения устройства, в нем «нулевые выходы

5 триггеров регистра, за исключением выхода триггера старшего разряда, соединены со входами им предшествующих схем совпадения, причем выход схемы совпадения старшего разряда через схему задерж1ки соединен со входами схем совпадения в цепях установки «единицы триггеров старшего и С чедующего за ним разрядов, а выходы остальных схем совпадения через схемы задержки соединены со входом схемы совпадения в цепи установки «нуля триггера своего разряда, а также со входом схемы совпадения в цепи установки «единицы триггера следующего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИОРИТЕТНОЕ УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1970 |

|

SU281901A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО | 1971 |

|

SU293297A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU317082A1 |

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Устройство для выделения информации из записи на носителе при магнитографической дефектоскопии сварных швов | 1972 |

|

SU476495A1 |

| Устройство для управления замещением информации | 1975 |

|

SU651413A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ НАНРЯЖЕНИЕ — КОД | 1967 |

|

SU193154A1 |

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1982 |

|

SU1112301A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU429423A1 |

| Устройство для вычисления функций упорядоченного выбора | 1972 |

|

SU444190A1 |

Даты

1969-01-01—Публикация