Изобретение Относится к области электроизмерительной и вычислительной техники и может быть использовано для преобразования непрерывных сигналов в цифровой код. Известны аналого-цифровые преобразователи, в которых повышение точности и быстродействия достигается путем использования комбинации методов преобразования. Недостатком таких преобразователей является то, что они содержат большое количество дополнительных элементов и сложные функциональные связи между ними.

Цель изобретения - унрощение схемы и увеличение быстродействия при сохранении точности и надежности преобразователя.

В предлагаемом аналого-цифровом преобразователе эта цель достигается путем иодключения входа запуска первого триггера в регистре младших разрядов к цепи установки преобразователя в начальное состояние и введения между регистрами триггеров старших и младших разрядов дополнительного триггера, выход которого соединен со входом цепи управления включением источника смещения компенсирующего напряжения и со входами схем совпадений переноса единицы в регистре старших разрядов, а вход сброса дополнительного триггера подключен через элемент задержки времени к шине распределителя, следующей за шинами старших разрядов. При

этом сигналом с этой шины при совпадении с инвертированным сигналом сравнивающего устройства происходит перенос единицы в регистре триггеров старших разрядов и увеличекие компенсирующего напрялсения.

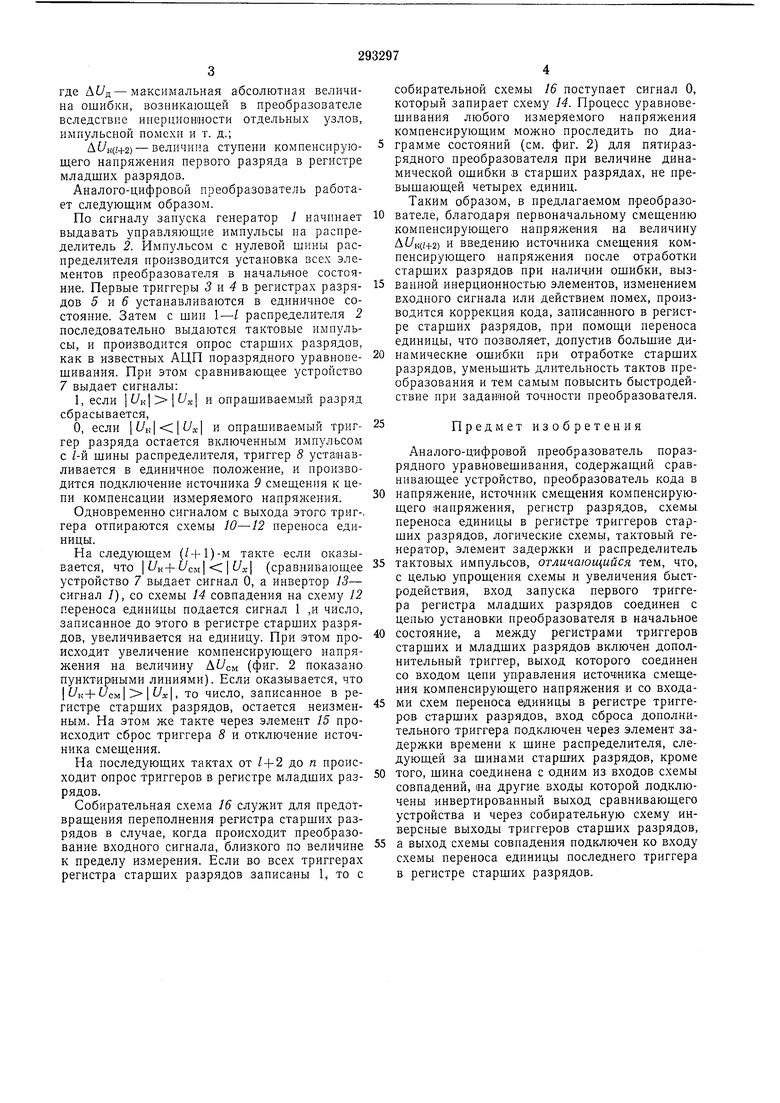

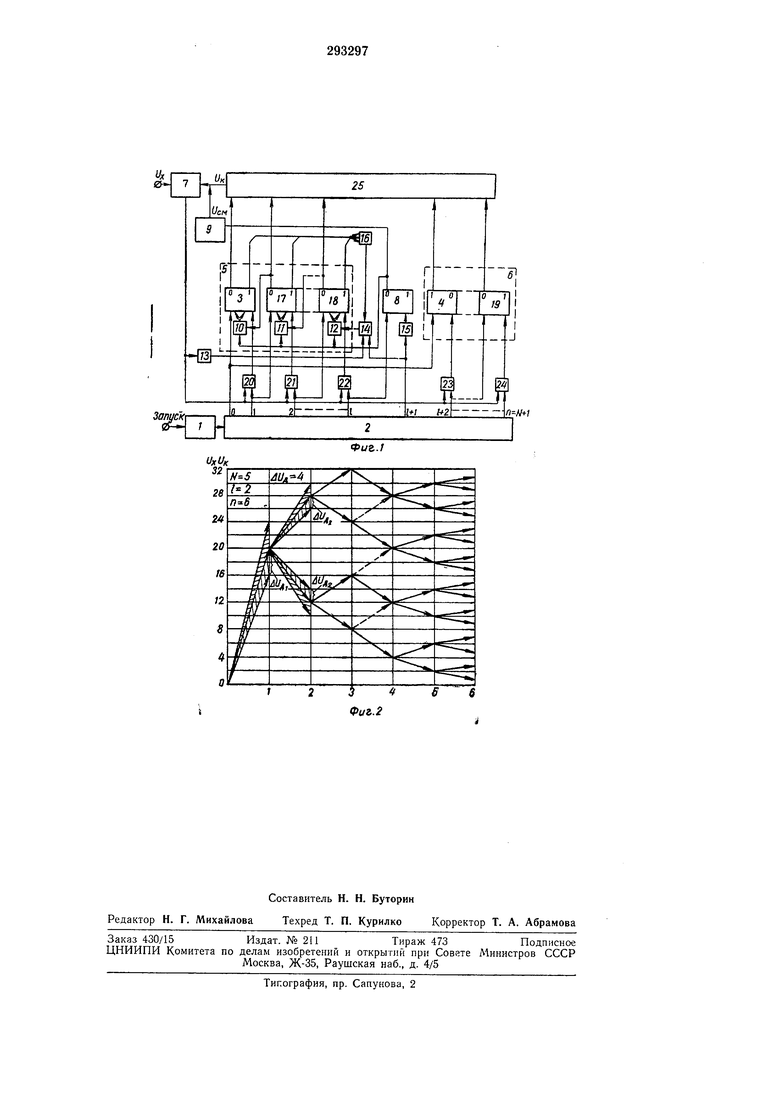

На фиг. 1 представлена схема аналого-цифрового преобразователя (АЦП) поразрядного уравновешивания, осуществляющего преобразование входного сигнала в N-разрядный двоичный код; «а фиг. 2 - диаграмма состояний компенсирующего напряжения при уравновешивании измеряемого напряжения для пятиразрядного преобразователя.

Преобразователь содержпт генератор / тактовых импульсов, распределитель 2 тактовых импульсов, первые триггеры , и 4 в регистрах старших 5 и младших 6 разрядов, сравнивающее устройство 7, дополнительный триггер 5, источник 9 смещения компенсирующего напряжения с ключом, схемы W-12 переноса единнцы, инвертор 13, схему 14 совпадения, элемент 15 задержки времени, собирательную схему 16, триггеры 17 и 18 регистра старших разрядов, триггер 19 регистра разрядов, схемы 20-24

совпадения и преобразователь 25 кода в напряжение.

Величина напряжения источника 9 выбирается таким образом, чтобы

где Af/H - максимальная абсолютная величина ошибки, возникающей в преобразователе вследствие инерционности отдельных узлов, импульсной помехи и т. д.;

(z+2) - величина ступени компенсирующего напрял ения первого разряда в регистре младщих разрядов.

Аналого-цифровой преобразователь работает следующим образом.

По сигналу запуска генератор / начинает выдавать управляющие импульсы па распределитель 2. Импульсом с нулевой шины распределителя производится установка всех элементов преобразователя в начальное состояние. Первые триггеры 3 и 4 ъ регистрах разрядов 5 и 6 устанавливаются в единичное состояние. Затем с шин 1-1 распределителя 2 последовательно выдаются тактовые импульсы, и производится опрос старших разрядов, как в известных АЦП поразрядного уравновешивания. При этом сравнивающее устройство 7 выдает сигналы:

1, если и опрашиваемый разряд сбрасывается,

О, если и опрашиваемый триггер разряда остается включенным импульсом с /-Й шины распределителя, триггер 8 устанавливается в единичное положение, и производится подключение источника 9 смещения к цепи компенсации измеряемого напрялсения.

Одновременно сигналом с выхода этого триг-, гера отпираются схемы 10--12 переноса единицы.

На следующем (/+1)-м такте если оказывается, что UK+UCM UX (сравнивающее устройство 7 выдает сигнал О, а инвертор 13- сигнал /), со схемы 14 совпадения на схему 12 переноса единицы подается сигнал 1 ,и число, записанное до этого в регистре старщих разрядов, увеличивается на единицу. При этом происходит увеличение компенсирующего напряжения на величину (фиг. 2 показано пунктирными линиями). Если оказывается, что I УСМ| I ж|, то число, записанное в регистре старших разрядов, остается неизменным. На этом же такте через элемент 15 происходит сброс триггера 8 и отключение источника смещения.

На последующих тактах от /+2 до п происходит опрос триггеров в регистре младщих разрядов.

Собирательная схема 16 служит для предотвращения переполнения регистра старших разрядов в случае, когда происходит преобразование входного сигнала, близкого по величине к пределу измерения. Если во всех триггерах регистра старших разрядов записаны 1, то с

собирательной схемы 16 поступает сигнал О, который запирает схему 14. Процесс уравновешивания любого измеряемого напряжения компенсирующим можно проследить по диаграмме состояний (см. фиг. 2) для пятиразрядного преобразователя при величине динамической ошибки в старших разрядах, не превышающей четырех единиц. Таким образом, в предлагаемом преобразователе, благодаря первоначальному смешению компенсирующего напряжения на величину At/K(;+2) и введению источника смещения компенсирующего напряжения после отработки старших разрядов при наличии ошибки, вызванной инерционностью элементов, изменением входного сигнала или действием помех, производится коррекция кода, записаеного в регистре старших разрядов, при помощи переноса единицы, что позволяет, допустив большие динамические ошибки при отработке старших разрядов, уменьшить длительность тактов преобразования и тем самым повысить быстродействие при заданной точности преобразователя.

Предмет изобретения

Аналого-цифровой преобразователь поразрядного уравновешивания, содержащий сравнивающее устройство, преобразователь кода в

напряжение, источник смещения компенсирующего напряжения, регистр разрядов, схемы переноса единицы в регистре триггеров старщих разрядов, логические схемы, тактовый генератор, элемент задержки и распределитель

тактовых импульсов, отличающийся тем, что, с целью упрощения схемы и увеличения быстродействия, вход запуска первого триггера регистра младших разрядов соединен с цепью установки преобразователя в начальное

состояние, а между регистрами триггеров старших и младших разрядов включен дополнительный триггер, выход которого соединен со входом цепи управления источника смещения компенсирующего напряжения и со входами схем переноса единицы в регистре триггеров старших разрядов, вход сброса дополнительного триггера подключен через элемент задержки времени к шине распределителя, следующей за шинами старших разрядов, кроме

того, шина соединена с одним из входов схемы совпадений, на другие входы которой подключены инвертированный выход сравнивающего устройства и через собирательную схему инверсные выходы триггеров старших разрядов,

а выход схемы совпадения подключен ко входу схемы переноса единицы последнего триггера в регистре старших разрядов.

Фиъ.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Г. Г. ЖИВИЛОБ; ::-.:;B::^ji03MAfl'1!^'а:гни кя,;^^'^?-кАЯ'Ч.'г. | 1972 |

|

SU324705A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU330538A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1018227A1 |

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1972 |

|

SU439913A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СО СТАТИСТИЧЕСКОЙ ОБРАБОТКОЙ РЕЗУЛЬТАТОВ | 1973 |

|

SU389623A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU748863A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU744968A1 |

| Преобразователь напряжения в код | 1980 |

|

SU884126A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

Даты

1971-01-01—Публикация