Изобретение относится к адфровой измерительной технике и может быть использовано при проектировании аналого-цифровых преобразователей с двоично-десятичным кодированием двухполярных -входных сигналов.

(В известных схемах двухполярных анологоцифровых преобразователей результат преобразования входных сигналов снимается либо в прямом, либо в обратном коде в зависимости от полярности входного сигнала, и для этого применяется двоичный или самодополняющийся двоично-десятичный код.

При работе аналого-цифрового преобразователя в комплексе с электронной вычислительной машиной наиболее удобным .является кодирование непрерывного си-гнала в двоичном или двои1чно-десятичном коде с весами 8-4-2- 1. Последний является несамодополняющимся кодом, поэтому применение его в двухполярных аналого-цифровых преобразователях поразрядного уравновешивания значительно усложняет схему преобразователя.

Цель изобретения - построение двухполярного аналого-цифрового преобразователя с кодированием выходных сигналов в коде с весами 8-4-2-1 без использования сложных схем перевода кода.

коде с весами 8 4-2-1 при использовании сетки с весами 2-4-2 -1, а для преобразования измеряемого напряжения другой полярности (положительной), отрабатываемого в коде с весами 2-4-2-1, обеспечивается перевод кода с весами 2-4--2-1 в код с весами 8-4-2-1 с небольшим количеством элементов.

Для этого в каждой декаде один выход

0 триггера старшего разряда декады соединен со входом схемы совпадения, другой вход которой подключен к триггеру полярности; выход схемы совпадения соединен со входами собирательных схем, через вторые входы кото5рых выходы триггеров разрядов, следующих за старшим, кроме младшего, соединены со входами цепей управления соответствующих ключей в дискретном делителе; кроме того, выходы этих триггеров разрядов соединены с блоком считывания через схемы совпадения, другие входы которых подключены ко второму выходу триггера старшего разряда декады; второй выход триггера полярности соединен со схемой совпадения, другой вход которой

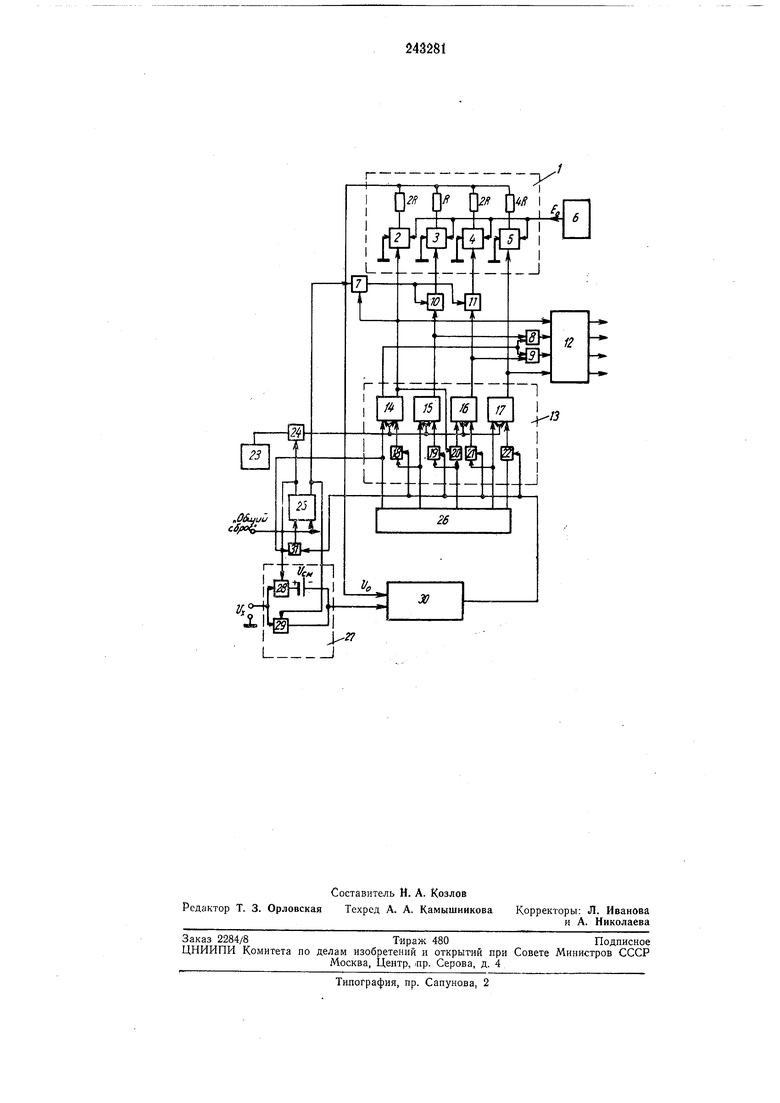

5 подключен к блоку управления, а выход соединен со счетным входом триггеров разрядов всех декад. ля У с измерительными ключами 2-5, источника образцового нанряжения 6, схем совпадения 7, 8, 9, собирательных схем 10, 11, блока считывания 12, цифрового ре.гистра /- с разрядными триггерами 14-17 и схемами совпадения 18-22, блока управления 23, схемы совпадения 24, три1ггера полярности 25, распределителя 26, блока управления полярностью 27 с ключами 28, 29; сравнивающего устройства 30, схемы совпадения 31. Рассмотрим работу одной старшей декады преобразователя, так Как остальные декады работают аналогично. Преобразователь поразрядного уравновешивания работает по принципу сравнения изме- 15 ряемого напряжения U . с образцовым напряжением t/o, которые подают на вход сравниваюшего устройства 30. Отработка образдового дискретного напряжения и о ti получение на выходе преобразо- 20 вател-я преобразуемого напряжения в коде с весами 8-4-2-1 принципиально различны для положительной и отрицательной полярностей преобразуемого напряжения (. Рассмотрим преобразование напряжения Uх для обеих полярностей раздельно. Образцовое напряжение U при отрицательной полярности иX отра-батывается в коде с весами 8-4-2-1 при использовании сегки сопротивлений с весами 2-4-2-1 для че- 30 го в управляющие цепи измерительных ключей 3 к 4 вводятся собирательные схемы 10 и 11 и схемы совпадения 7. Ввод этих схем позволяет при отрицательной полярности преобразуемого напряжения U открывать ключи 3 35 и 4 не только от срабатывания триггеров 15 и /(, но 1И от (срабатывания три1ггера/4. При срабатывании триггера 14 образцовое напряжение Ug на выходе дискретного делителя 1 получается равным 0,8 Яо- Если 40 0, то последующее подключение разрядных триггеров 15-17 не изменит величины образцового напряжения t/o на выходе дискретного, делителя 1. Если ,8Eo, то очередным импульсом 45 распределителя 26 триггер 14 сбросится в положение «О, и последующее подключение триггеров 15 и 16 будет менять Ug в соответствии с весами второго и третьего разрядов. По окончании отработки образцового напря- 50 жения и о по всем разрядам декады преобразуемое напряжение отрицательной полярности о-казывается записанным на разрядные триггеры 14-17. Полученный код отличается от требуемого кода с весами- 8-4-2-1 тем, что 55 при Ux 8 или 9 во втором и третьем разрядах декады записана «1 вместо «О. Для получения требуемого кода с весами 8-4-2-1- вводятся схемы совпадения 8, 9. В результате отработки Uo 8 или (/о 9 бо триггер 14 перебрасывается в положение «1, что соответствует «1 в первом разряде декады в коде с весами 8-4-2-1. При этом схемы совпадения 8, 9 закрываются, и на выходе 5 10 второго и третьего разрядов декады получается «О. Образцовое напряжение Ug при положительной полярности измеряемого напрял ення Uj. отрабатывается в коде свесами 2-4-2-1. Схема совпадения 7 закрыта для положительной полярности и X, У( сигнал с триггера 14 на измерительные ключи 3 HI 4 не проходит. Для устранения неоднозначности получаеМО-го кода (при t/. 6 или L 7) вводится схема совпадения 20. При этом исключается возможность появления «1 на выходе третьего разряда декады при отсутствии «1 на выходе первого разряда декады. По окончании отработки образцового напряжения Uo по всем разрядам декады преобразуемое напряжение Uj оказывается записанным на триггеры 14-17. Сигнал «прямой код, .поступаюший перед сигналом «считывания из блока управлени-я 23, проходит через схему совпадения 24, открытую при положительной полярности, на счетные входы триггеров 14-17 и изменяет состояние последних. Получающийся на триггерах 14-17 код переводят в код с весами 8-4-2-1, для чего применяются те же схемы совпадения 5, 9, что и при преобразовании напряжения отрицательной полярности. В конце преобразования положительных или отрицательных напряжеиий импульс «считывания поступает в блок ний импульс «считывания поступает в бл считывания 12, который выдает преобразосчитывания 12, который выдает преобра; ванный сигнал на выход преобразователя. Предмет изобретения Аналого-цифровой преобразователь поразрядного уравновешивания с двоично-десятичным кодированием двухполярных входных сигналов, содержащий распределитель, цифровой регистр, дискретный делитель с сеткой резисторов с «весами 2-4-2-1 в- каждой декаде, источник опорного напряжения, сравнивающее устройство, блок управлени1Я полярностью, триггер полярности, блок считывания. отличающийся тем, что, с целью упрощения устройства, в нем в каждой декаде один выход триггера старшего разряда декады соединен со входом схемы совпадения, другой вход которой подключен к триггеру полярности; выход схемы совпадения соединен со входами собирательных схем, через вторые входы которых выходы триггеров разрядов, следующих за старшим, кроме младшего, соединены со входами цепей управления соответствующих ключей в дискретном делителе; кроме того, выходы этих триггеров разрядов соединены с блоком считывания через схемы совпадения. другие входы которых подключены ко второму выходу триггера старшего разряда декады; второй выход триггера полярности соединен со схемой совпаденИЯ, другой вход которой подключен iK блоку управления, а выход соединен со счетным входом триггеров разрядов всех декад.

V,

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1970 |

|

SU588627A1 |

| БИБЛИОТЕЬСА | 1971 |

|

SU289794A1 |

| Аналого-цифровой преобразователь считывания | 1977 |

|

SU677097A1 |

| Преобразователь напряжения в код | 1977 |

|

SU728222A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ И РЕГИСТРАЦИИ НАПРЯЖЕНИЯ АККУМУЛЯТОРНОЙ БАТАРЕИ• j'"^ ^ ^ ;' <- kii :.ЧР^!!1-Ли>&^а-4 | 1973 |

|

SU405147A1 |

| Устройство для определения динамическихХАРАКТЕРиСТиК пРЕОбРАзОВАТЕлЕй | 1979 |

|

SU838612A1 |

| Устройство для измерения динамическихХАРАКТЕРиСТиК АНАлОгО-цифРОВыХ пРЕОбРАзО-ВАТЕлЕй | 1979 |

|

SU815897A1 |

| Преобразователь частоты в код | 1977 |

|

SU746922A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1979 |

|

SU964981A1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

Авторы

Даты

1969-01-01—Публикация