Изобретение относится к вычислительной технике.

Известны дешифраторы-формирователи, содержащие ключи, формирователи импульсов, дешифраторы. В этих дешифраторах на одну возбуждаемую цепь приходится большое количество оборудования.

Предлагаемый дешифратор отличается тем, что в нем выходы первого дешифратора через первую группу ключей, а выходы второго дешифратора через формирователи импульсов подключены к соответствуюш:им входам диодно-трансформаторных вентилей второго блока, третий дешифратор через вторую группу ключей подключен к первым входам диоднотрансформаторных вентилей первого блока, вторые входы которых подключены к выходам второго блока диодно-трансформаторных вен1илей.

Это позволяет сократить количество оборудования.

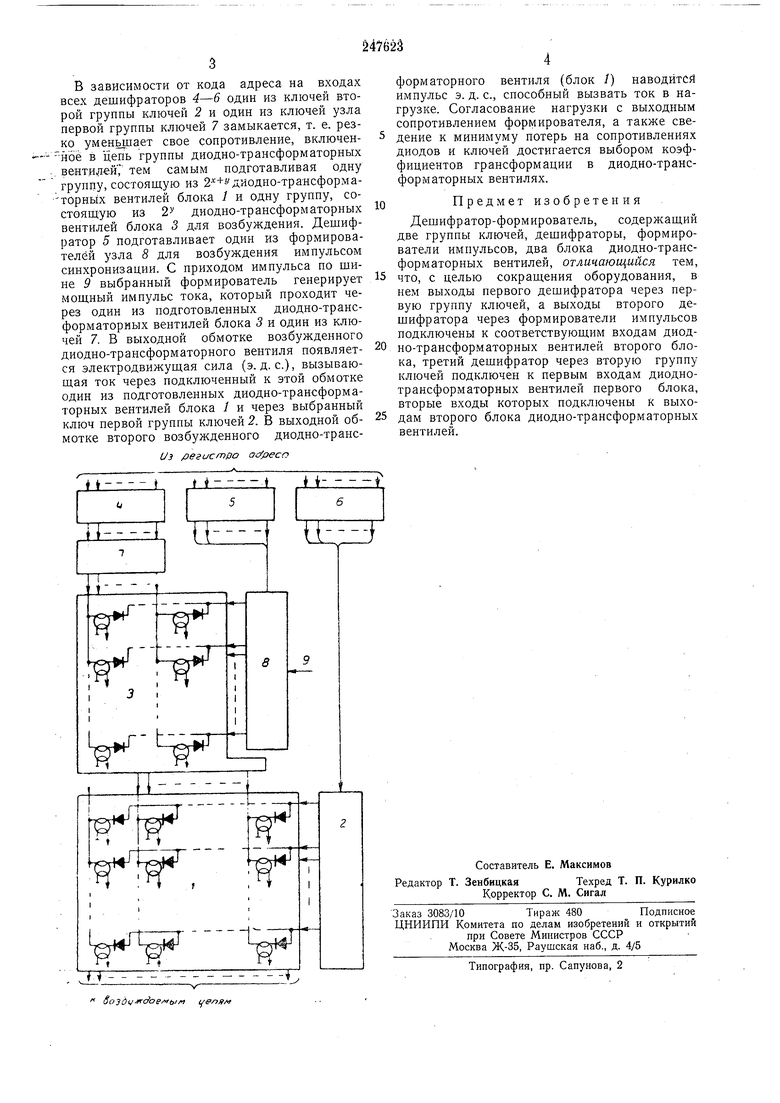

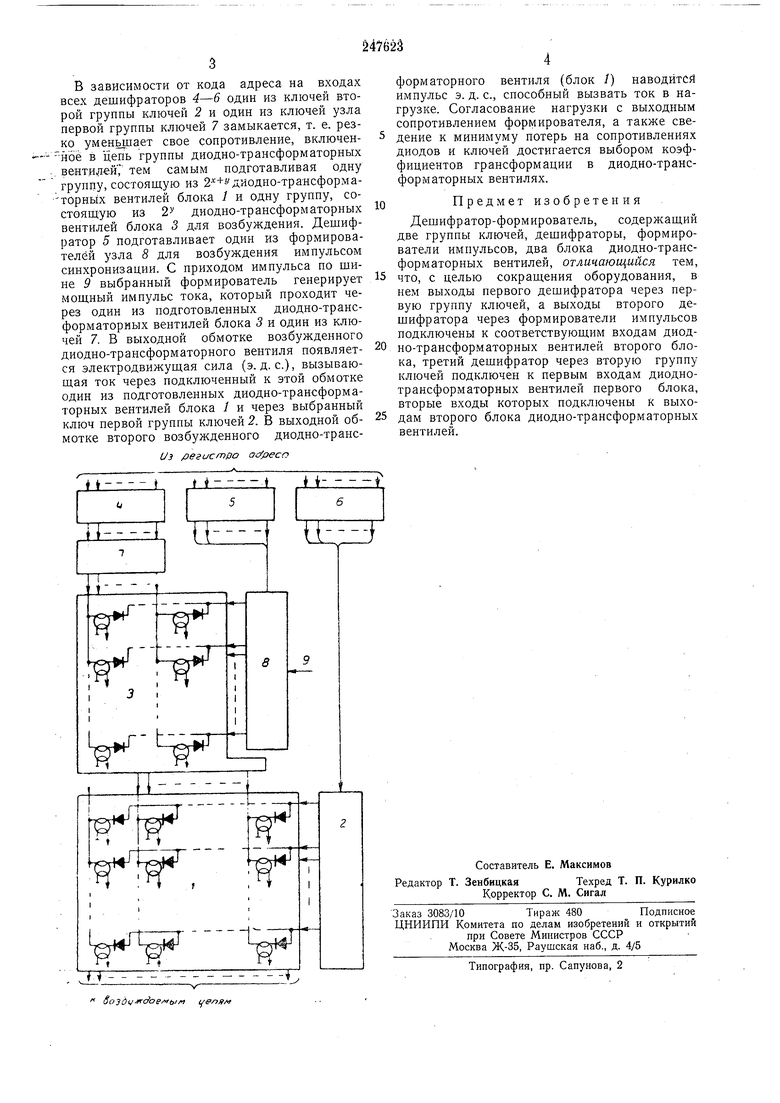

Схема устройства нредставлена на чертеже.

Устройство содержит первый блок диоднотрансформаторных вентилей 1, вторую группу -ключей 2, второй блок диодно-трансформаторных вентилей 3, первый 4, второй 5, третий 6 дешифраторы импульсов, первую группу ключей 7, формирователи импульсов 8, шину импульсов синхронизации Р.

даемых цепей (где п - количество разрядов в регистре адреса), подключенных к такому же количеству диодно-трансформаторных вентилей /, первичные обмотки которых подключены к 2 ключам 2 с одной стороны и через диоды - к выходным обмоткам 2 диоднотрансформаторных вентилей 5 (где х, у, s - количество разрядов регистра адреса, не показанного на чертеже), подключенных к дешифраторам 4-6 соответственно таким образом, что каждый ключ соединен с каждым диодно-трансформаторным вентилем блока через один и только один диодно-трансформаторный вентиль блока 1. В свою очередь,

диодно-трансформаторные вентили блока 3 одними концами подключены к ключам 7, а другими - к формирователям 8 таким образом, что каждый ключ соединен с каждым формирователем через один и только один

диодно-трансформаторный вентиль блока 3. Ключи 2 управляются маломощным потенциальным дешифратором 6, связанным с «s разрядами регистра адреса, ключи 7 - маломоШНым потенциальным дешифратором 4,

связанным с к разрядами регистра адреса, а формирователи 5 - по шине 9 импульсов синхронизации и маломощным потенциальным дешифратором 5, связанным с у разрядами регистра адреса.

В зависимости от кода адреса на входах всех дешифраторов 4-6 один из ключей второй группы ключей 2 и один из ключей узла первой группы ключей 7 замыкается, т. е. резко уменьшает свое сопротивление, включенноё в цепь группы диодно-трансформаторных

вентидей, тем самым подготавливая одну

группу, состоящую из 2 + диодно-траясформаторных вентилей блока / и одну группу, состоящую из 2У диодно-трансформаторных вентилей блока 3 для возбуждения. Дещифратор 5 подготавливает одии из формирователей узла 8 для возбуждения импульсом синхронизации. С приходом импульса по щине 9 выбранный формирователь генерирует мощный импульс тока, который проходит через один из подготовленных диодно-трансформаторных вентилей блока 3 и один из ключей 7. В выходной обмотке возбужденного диодно-трансформаторного вентиля появляется электродвижущая сила (э. д, с.), вызывающая ток через подключенный к этой обмотке одии из подготовленных диодно-трансформаторных вентилей блока 1 и через выбранный ключ первой группы ключей 2. В выходной обмотке второго возбужденного диодно-трансi/s регистра

форматорного вентиля (блок 1) наводитсй импульс э. д. с., способный вызвать ток в нагрузке. Согласование нагрузки с выходным сопротивлением формирователя, а также сведение к минимуму потерь на сопротивлениях диодов и ключей достигается выбором коэффициентов грансформации в диодно-трансформаторных вентилях.

Предмет изобретения

Дещифратор-формирователь, содержащий две группы ключей, дещифраторы, формирователи импульсов, два блока диодно-трансформаторных вентилей, отличающийся тем,

что, с целью сокращения оборудования, в нем выходы первого дешифратора через первую группу ключей, а выходы второго дешифратора через формирователи импульсов подключены к соответствующим входам диодно-трансформаторных вентилей второго блока, третий дешифратор через вторую группу ключей подключен к первым входам диоднотрансформаторных вентилей первого блока, вторые входы которых подключены к выходам второго блока диодно-трансформаторных вентилей.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ из постоянного ТРАНСФОРМАТОРНОГО ЗАПОМИНАЮЩЕГО | 1973 |

|

SU377868A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ С ОДНОВРЕМЕННЫМ ПЕРЕНОСОМ | 1961 |

|

SU147366A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛИЗАТОР | 1970 |

|

SU275531A1 |

| Формирователь адресных токов | 1979 |

|

SU924752A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ ИЗ ОСТАТОЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В ПОЛИАДИЧЕСКУЮ | 1973 |

|

SU407301A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Многоканальный преобразователь код-угол | 1975 |

|

SU526935A1 |

| УСТРОЙСТВО для ВВОДА и ОТОБРАЖЕНИЯ ГЕОМЕТРИЧЕСКИХ ИЗОБРАЖЕНИЙ | 1973 |

|

SU367438A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

Даты

1969-01-01—Публикация