Изобретение относится к области цифровой вычислительной техники, в частности к устройствам для исследования и анализа спектров ядерных излучений.

Известны многоканальные анализаторы импульсов с носледовательным обращением к разрядам числа, содержащие регистр разряда, регистр адреса, блок памяти на ферритах, блок формирования программных импульсов, блок коммутации, дешифратор разрядного регистра и переключатель разрядов.

Однако известные устройства недостаточно быстродейственны вследствие того, что цепь формирования программных импульсов остается постоянной во всех зажимах, и имеют малую скорость опроса каналов при выводе информации на осциллографическую трубку.

Предлагаемое устройство отличается от известных тем, что оно содержит дополнительные вентили и коммутатор кода, причем импульсные входы первого и второго вентилей объединены и нодсоединены к выходу считывания «1 блока памяти, потенциальный вход первого вентиля соединен с выходом блока коммутации для включения режима измерения, а его выход связан со входом задания начала цикла блока формирования программных импульсов и счетным входом разрядного регистра, потенциальный вход второго вентиля соединен с выходом блока коммутации заДания релхима наблюдения, а его выход связан со входом разрешения записи блока формирования программных импульсов; импульсные входы третьего и четвертого вентилей объединены и подключены к выходу считывания «О блока памяти, потенциальный вход третьего вентиля подсоединен к потенциальному входу первого вентиля, а его выход- к выходу второго вентиля, потенциальный вход четвертого вентиля соединен с потенциальным входом второго вентиля, а выход-с выходом первого вентиля, первый потенциальный вход пятого вентиля связан с переключателем разрядов, а второй - с потенциальным входом второго вентиля, импульсный вход соединен с выходом команды «сброс блока коммутации, а его выход связан со входом коммутатора кода разрядного регнстра, выходы которого подключены к установочным входам триггеров разрядного регистра.

Это позволяет улучшить технические и эксплуатационные параметры.

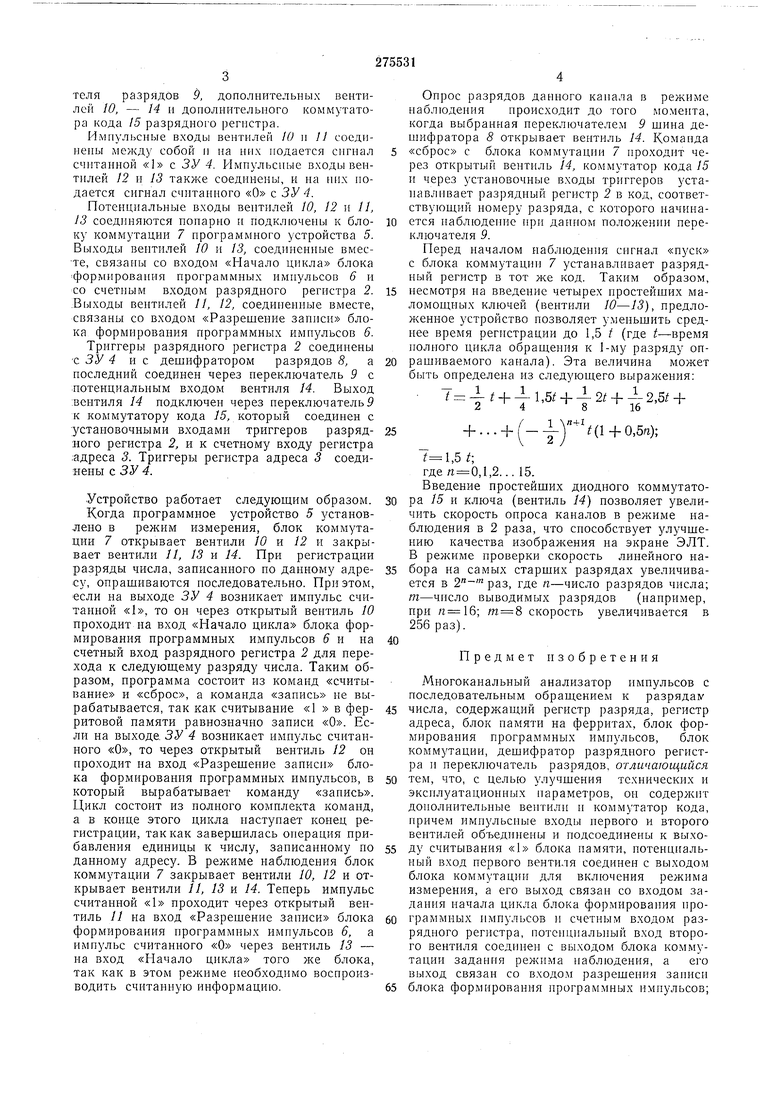

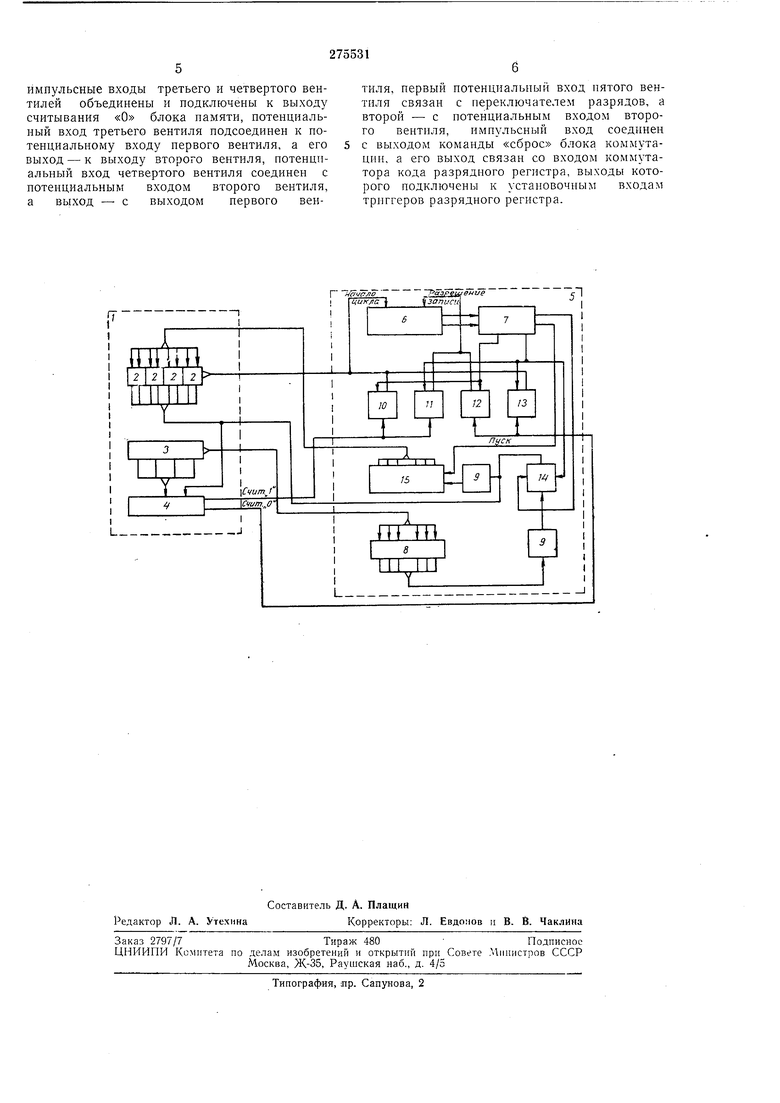

На чертеже приведена структурная схема многоканального анализатора. Он содержит регистрирующее устройство 1, включающее разрядный регистр 2, регистр адреса 3, запоминающее устройство (ЗУ) 4 и программное устройство 5, состоящее пз блока формирования пpoгpaм п ыx импульсов 6, блока коммутации 7, дещифратора разрядов 8, переключателя разрядов 9, дополнительных вентилей 10, - 14 и донолнительиого коммутатора кода 15 разрядного регистра.

Импульсные входы вентилей 10 и 11 соединены между собой и на них подается снгиал считанной «1 с ЗУ 4. Имиульсные входы веитнлей 12 и 13 также соединены, и на 1И1х иодается сигнал считанного «О с ЗУ 4.

Потенциальные входы вентилей 10, 12 и 11, 13 соединяются ионарио и иодключеиы к блоку коммутации 7 ирограммного устройства 5. Выходы вентилей 10 н 13, соединенные вместе, связаны со входом «Начало цикла блока сформирования программных импульсов 6 и со счетным входом разрядного регистра 2. .Выходы вентилей 11, 12, соединенные вместе, связаны со входом «Разрешение заннси блока формирования программных импульсов 6.

Триггеры разрядного регистра 2 соединены -с ЗУ 4 и с дешифратором разрядов 8, а последний соединен через переключатель 9 с потенциальным входом вентиля 14. Выход вентиля 14 подключен через нереключательР к коммутатору кода 15, который соединен с установочными входами триггеров разрядного регистра 2, и к счетному входу регистра .адреса 3. Триггеры регистра адреса 3 соединены с ЗУ 4.

Устройство работает следующим образом.

Когда программное устройство 5 установлено в режим измерения, блок коммутации 7 открывает вентили 10 и 12 и закрывает вентили //, 13 и 14. При регистрации разряды числа, записанного но данному адресу, опрашиваются последовательио. При этом, если на выходе ЗУ 4 возникает имиульс считанной «1, то он через открытый вентиль 10 цроходит на вход «Начало цикла блока формирования программных импульсов 6 и на счетный вход разрядного регистра 2 для нерехода к следующему разряду числа. Таким образом, программа состоит из команд «считывание и «сброс, а комаида «запись не вырабатывается, так как считывание «1 в ферритовой памяти равнозначно записи «О. Если на выходе ЗУ 4 возникает импульс считанного «О, то через открытый вентиль 12 он проходит на вход «Разрешение заниси блока формирования нрограммных импульсов, в который вырабатывает команду «запись. Цикл состоит из полиого комплекта команд, а в копце этого цикла наступает конец регистрации, так как завершилась оиерация прибавления единицы к числу, записанному по данному адресу. В режиме наблюдения блок коммутации 7 закрывает вентили 10, 12 и открывает вентили 11, 13 и 14. Теперь импульс считанной «1 проходит через открытый вентиль У/ на вход «Разрешение заниси блока формирования нрограммных импульсов 6, а импульс считаииого «О через вентиль 13 - иа вход «Начало цикла того же блока, так как в этом необходимо воспроизводить считанную информацию.

Опрос разрядов данного канала в режиме наблюдеиия происходит до того момента, когда выбранная переключателем 9 шииа дешифратора 8 открывает вентиль 14. Команда «сброс с блока коммутации 7 проходит через открытый вентиль 14, коммутатор кода 15 и через установочные входЕз триггеров устанавливает разрядный регистр 2 в код, соответствующий иомеру разряда, с которого начинается паблюденне при данном положенни переключателя 9.

Перед началом наблюдения сигнал «пуск с блока коммутации 7 устаиавливает разрядный регистр в тот же код. Таким образом,

несмотря иа введеиие четырех иростейших маломощных ключей (веитили 10-13), предложенное устройство позволяет уменьшить средиее время регистрации до 1,5 / (где i-время полного цикла обращения к 1-му разряду опрашиваемого канала). Эта величииа может быть определеиа из следующего выражения:

+... + ((1+0,5а);

/

,

где/г 0,1,2... 15.

Введение простейших диодного коммутатора 15 и ключа (вентиль 14) позволяет увеличить скорость оироса каналов в режиме наблюдеиия в 2 раза, что снособствует улучщению качества изобра кения иа экране ЭЛТ. В режиме проверки скорость линейного набора на самых старщих разрядах увеличивается в раз, где п-число разрядов числа; т-число выводимых разрядов (иаиример, нри т 8 скорость увеличивается в 256 раз).

Предмет изобретения

Многоканальный анализатор импульсов с последовательным обращением к разряда1У

числа, содержащий регистр разряда, регистр адреса, блок памяти на феррнтах, блок формирования программных импульсов, блок коммутации, дещифратор разрядного регистра и переключатель разрядов, отличающийся

тем, что, с целью улучщения технических и экснлуатационных параметров, он содерл ит дополиительиые вентили и коммутатор кода, причем импульсиые входы первого и второго веитилей объединены и подсоединены к выхоДУ считывания «1 блока памяти, нотенциальиый вход первого вентиля соединен с выходом блока коммутации для включения режима измерения, а его выход связан со входом задания пачала цикла блока формироваиия ирограммиых импульсов и счетным входом разрядного регистра, потенциальный вход второго вентиля соединен с выходом блока коммутации задания режима наблюдения, а его выход связаи со входом разрешения заниси

импульсные входы третьего и четвертого вентилей объединены и нодключены к выходу считывания «О блока памяти, потенциальный вход третьего вентиля подсоединен к потенциальному входу нервого вентиля, а его выход - к выходу второго вентиля, потенциальный вход четвертого вентиля соединен с потенциальным входом второго вентиля, а выход - с выходом первого вентиля, первый потенциальный вход пятого вентиля связан с переключателем разрядов, а второй - с потенциальным входом второго вентиля, импульсный вход соединен с выходом команды «сброс блока коммутации, а его выход связан со входом коммутатора кода разрядного регистра, выходы которого подключены к установочным входам триггеров разрядного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный анализатор импульсов с последовательным обращением к разрядам числа | 1978 |

|

SU746547A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА ЦИЛИНДРИЧЕСКИХ МАГНИТНЫХ ПЛЕНКАХ | 1968 |

|

SU231224A1 |

| УСТРОЙСТВО для СЧИТЫВАНИЯ ОСЦИЛЛОГРАММ | 1968 |

|

SU218546A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1970 |

|

SU273281A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР С УСРЕДНЕНИЕМ | 1967 |

|

SU190097A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Цифровое устройство доплеровской фильтрации | 1990 |

|

SU1830496A1 |

| УСТРОЙСТВО для ВВОДА и ОТОБРАЖЕНИЯ ГЕОМЕТРИЧЕСКИХ ИЗОБРАЖЕНИЙ | 1973 |

|

SU367438A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЭТАЛОННОЙ КАРТЫ МЕСТНОСТИ ДЛЯ НАВИГАЦИОННЫХ СИСТЕМ | 1992 |

|

RU2022355C1 |

Даты

1970-01-01—Публикация