Предлагаемое изобретение относится к области вычислительной техники, а именно к цнфР.ОВЫМ управляющим устройствам, и может быть использовано организациями, занимающимися разработкой и внедрением цифровых систем управления иромышленными технологическими процессами.

Известны устройства для цифрового управления на потенциальных элементах, содержащие коммутатор, соедииенный с аналого-цифровым преобразователем и блоком управления, которые связаны .с арифметическим блоком, состоящим из регистра частичных сумм, сумматора, регистра множимого и множителя, связанных между собой илинамн иерениси, и цепи переноса сумматора, блок выходных преобразователей, подключенный к блоку управления и арифметическому блоку, и блок оперативной памяти.

Известные устройства содержат большое количество оборудования.

Предложенное устройство отличается от известных тем, что, с целью уменьшения количества оборудования, в ием выход регистра множителя арифметического блока подключен к шинам записи блока оперативной памяти, а вход регистра сумматора подключен к шинам считывания блока оперативной памяти.

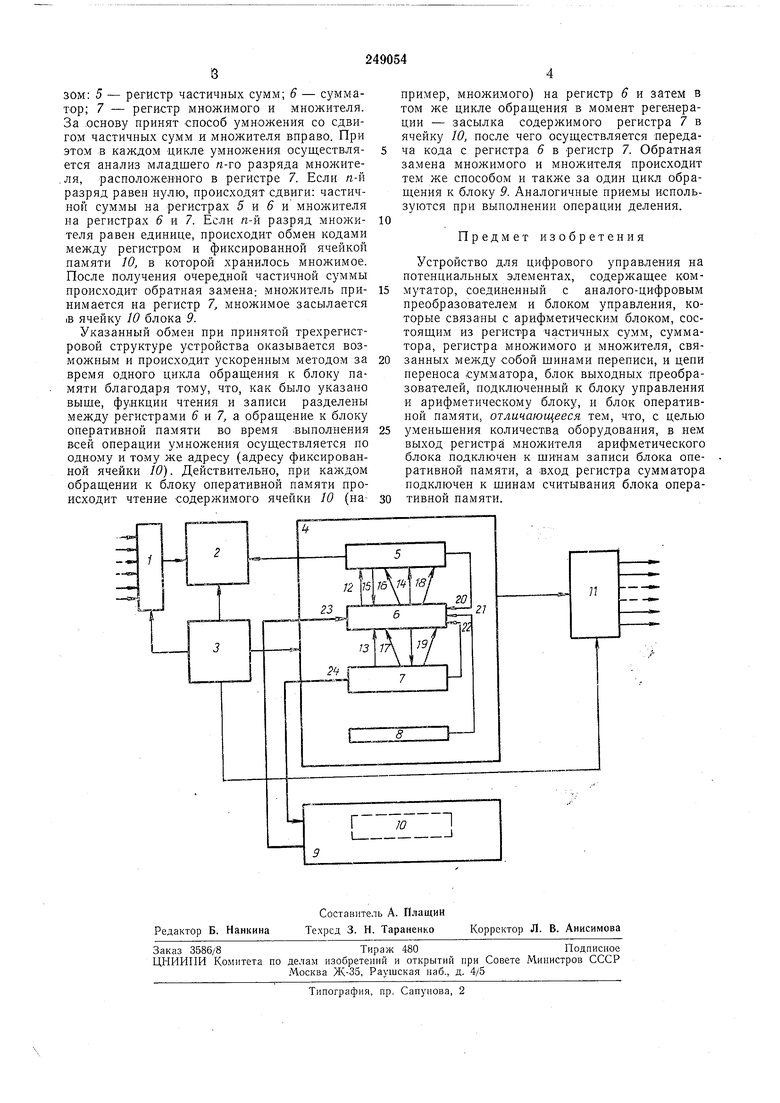

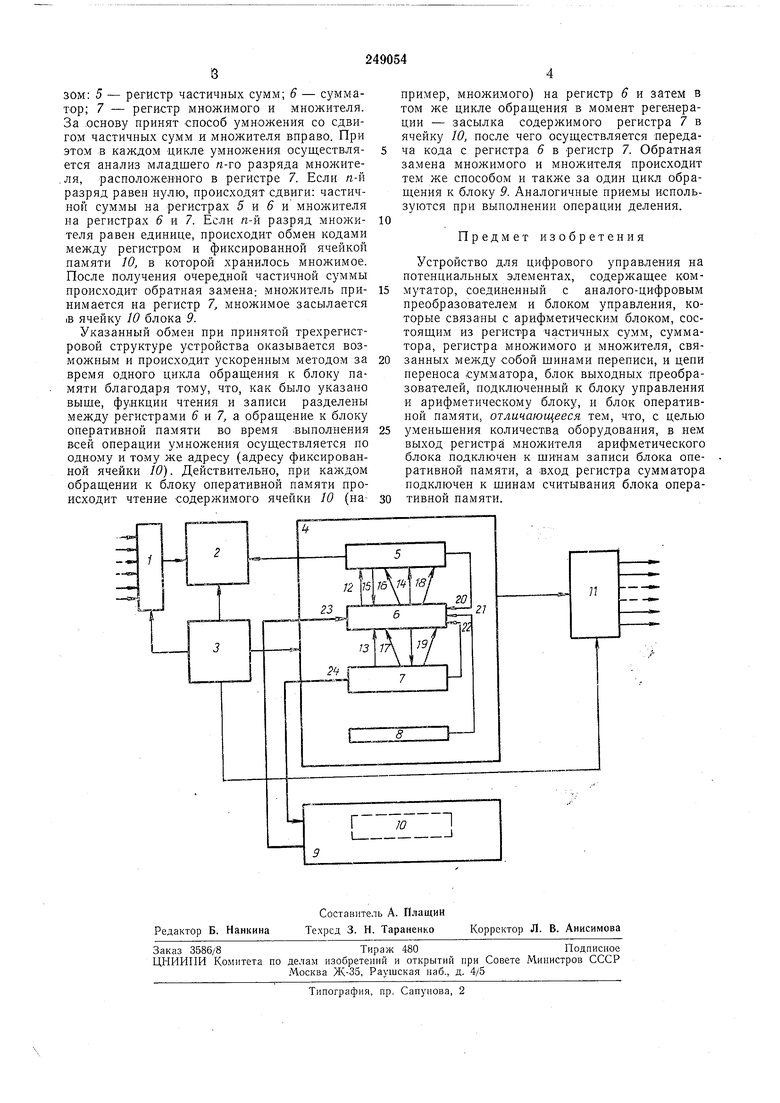

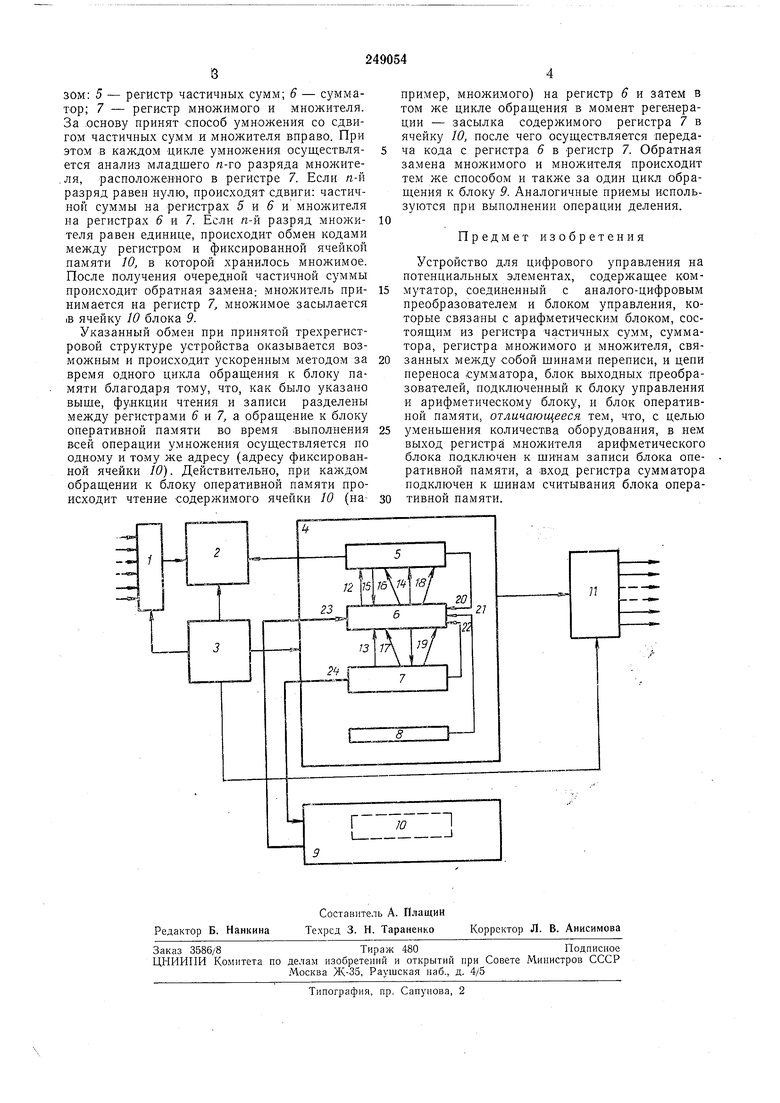

лого-цифровой преобразователь без суммирующего счетчика; 3 - блок уиравления; 4 - арифметический блок параллельного типа с входящими в него регистрами 5, 6, 7 и цепочкой переноса 8, построенными на элементах потенциального типа; 9 - блок оперативной памяти без регистра числа; 10 - ячейка блока оперативной памяти с фиксированным адресом; 11 - блок выходных преобразователей. lO Цифрами 12-24 обозначены связи между регистрами блока 4 и между другими блоками устройства, а именно; 12, 13, 14 - прямые передачи; 15 - инверсная передача; 16, 17-- передачи со сдвигом вправо; 18, 19 - передачи со сдвигом влево; 20-22 - связи, представляющие логику сумматора двумя регистрами 6 н 7; и соответственно: 23 - шина чтения из блока 9 в регистр 6; 24 - шина записи в блок 9 из регистра 7.

20 Устройство работает следующим образом. В процессе реализации заданного алгоритма управления арифметический блок выполняет арифметические операции сложения, вычитания, умножения и др.

25 При данной структуре арифметического блока отличной от обычной является лишь методика выполнения операций умножения и деления. Рассмотрим выполнение операции умножения. Функции регистров при выполнении

зом: 5 - регистр частичных сумм; 6 - сумматор; 7 - регистр множимого и множителя. За .основу принят способ умножения со сдвигом частичных сумм и множителя вправо. При этом в каждом цикле умножения осуществляется анализ младилего «-го разряда множите. ля, расположенного в регистре 7. Если я-й разряд равен нулю, происходят сдвиги: частичной суммы на регистрах 5 и 5 и множителя на регистрах б и 7. Если га-й разряд множителя равен единице, происходит обмен кодами между регистром и фиксированной ячейкой памяти 10, в которой хранилось множимое. После получения очередной частичной суммы происходит обратная замена; мнол итель принимается на регистр 7, множимое засылается (В ячейку W блока 9.

Указанный обмен при принятой трехрегистровой структуре устройства оказывается возможным и происходит ускоренным методом за время одного цикла обращения к блоку памяти благодаря тому, что, как было указано выще, функции чтения и записи разделены между регистрами 6 и 7, а обращение к блоку оперативной памяти во время выполнения всей операции умножения осуществляется но одному и тому же адресу (адресу фиксированной ячейки 10). Действительно, при каждом обращении к блоку оперативной памяти происходит чтение содержимого ячейки 10 (на

пример, множимого) на регистр 6 и затем в том же цикле обращения в момент регенерации - засылка содержимого регистра 7 в ячейку 10, после чего осуществляется передача кода с регистра 6 в регистр 7. Обратная замена множимого и множителя происходит тем же способом и также за один цикл обращения к блоку 9. Аналогичные приемы используются при выполнении операции деления.

Предмет изобретения

Устройство для цифрового управления на потенциальных элементах, содержащее коммутатор, соединенный с аналого-цифровым преобразователем и блоком управления, которые связаны с арифметическим блоком, состоящим из регистра частичных сумм, сумматора, регистра множимого и множителя, связанных между собой щинами переписи, и цепи переноса сумматора, блок выходных преобразователей, подключенный к блоку управления и арифметическому блоку, и блок оперативной памяти, отличающееся тем, что, с целью

уменьщения количества оборудования, в нем выход регистра м.ножителя арифметического блока подключен к шинам записи блока оперативной памяти, а вход регистра сумматора подключен к щинам считывания блока оперативной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Многоканальное устройство для измерения температуры | 1990 |

|

SU1791731A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Устройство для умножения с накоплением | 1988 |

|

SU1509876A1 |

| КОНВЕЙЕРНЫЙ АРИФМЕТИЧЕСКИЙ УМНОЖИТЕЛЬ | 2013 |

|

RU2546072C1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения с накоплением комплексных чисел | 1987 |

|

SU1478211A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОРКИ ИНФОРМАЦИИ | 1970 |

|

SU268753A1 |

| Устройство для умножения с накоплением комплексных чисел | 1988 |

|

SU1587230A1 |

Даты

1969-01-01—Публикация