i:

Изобретение относится к области устройств предварительной обработки информации, получаемой при регистрации различных процессов, и может быть применено нри проектировании устройств накопления и обработки информации.

Известны устройства обработки информации, содержащие запоминающий блок с регистром адреса, адресными ключами и элементами памяти, арифметический блок, включающий регистр числа со знаковым разрядом и сумматор с первым и вторым знаковыми разрядами, а также содержащее блок управления.

Предлагаемое устройство содерл ит импульсно-потенциальный ключ, один из потенциальных управляющих входов которого подсоединен к выходу второго знакового разряда сумматора, два других управляющих потенциальных входа через триггер, а управляющий импульсный вход непосредственно соединен с блоком управления, два импульсных выхода ключа соединены со счетными входами регистра числа и сумматора, командный выход .блока управления соединен с щиной выбора адреса нулевого канала и щиной отключення адресных ключей через триггер и ключ выбора адреса нулевого канала, при этом щины сброса в нуль регистра числа и знакового разряда этого регистра, а также щины сброса

в нуль сумматора с первым знаковым разрядом и второго знакового разряда сумматора раздельно подключены к командным выходам блока управления.

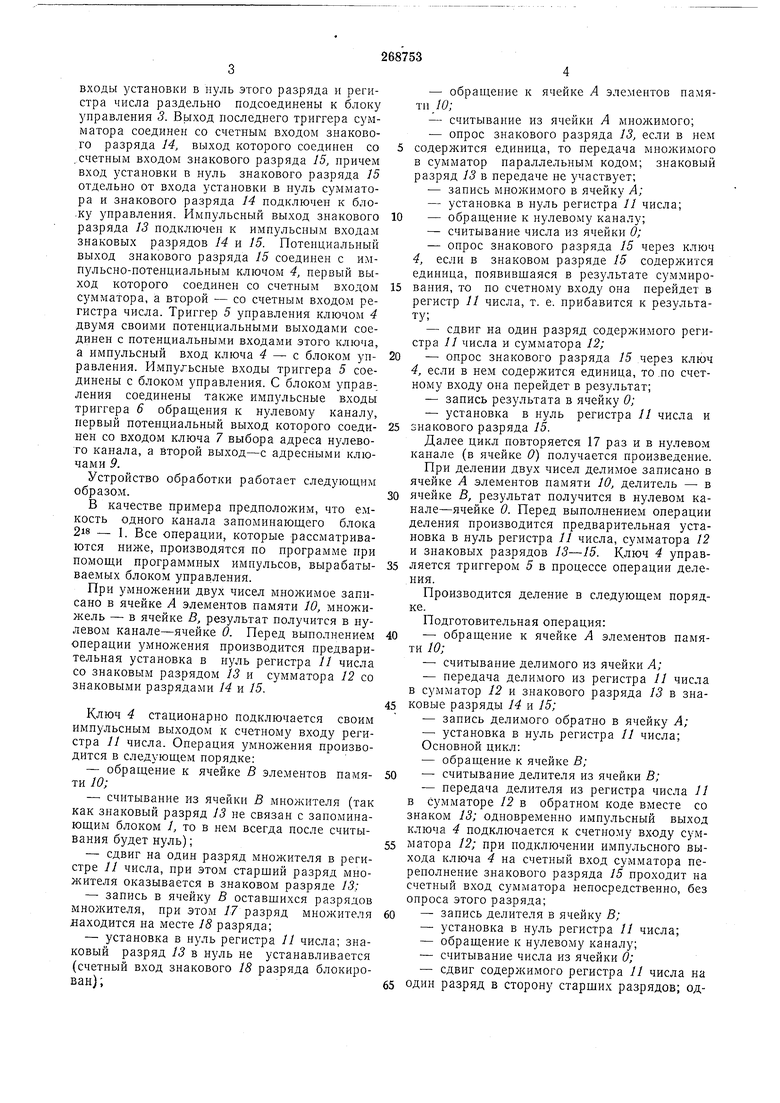

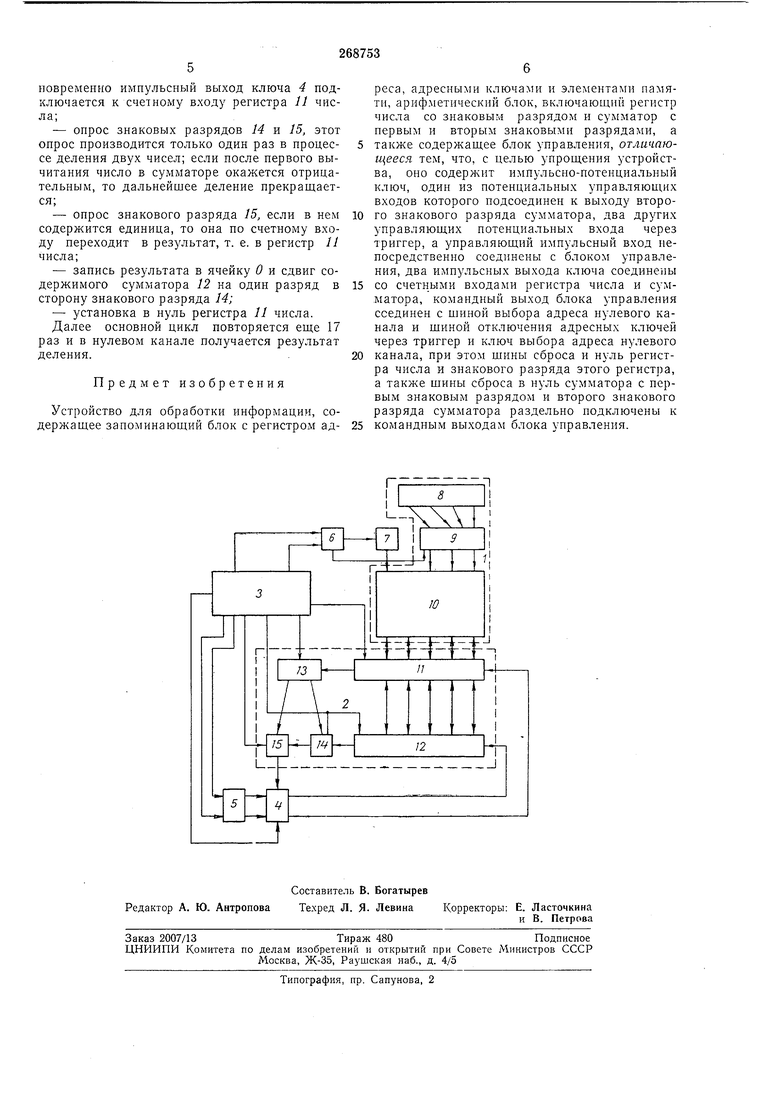

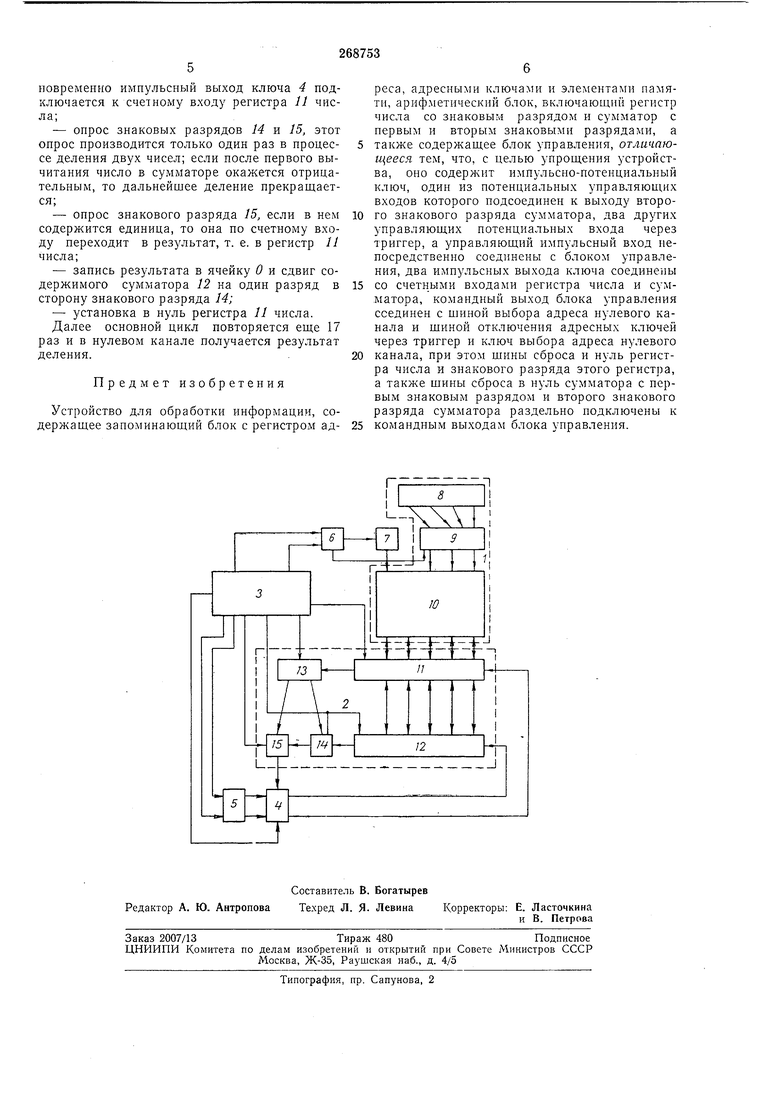

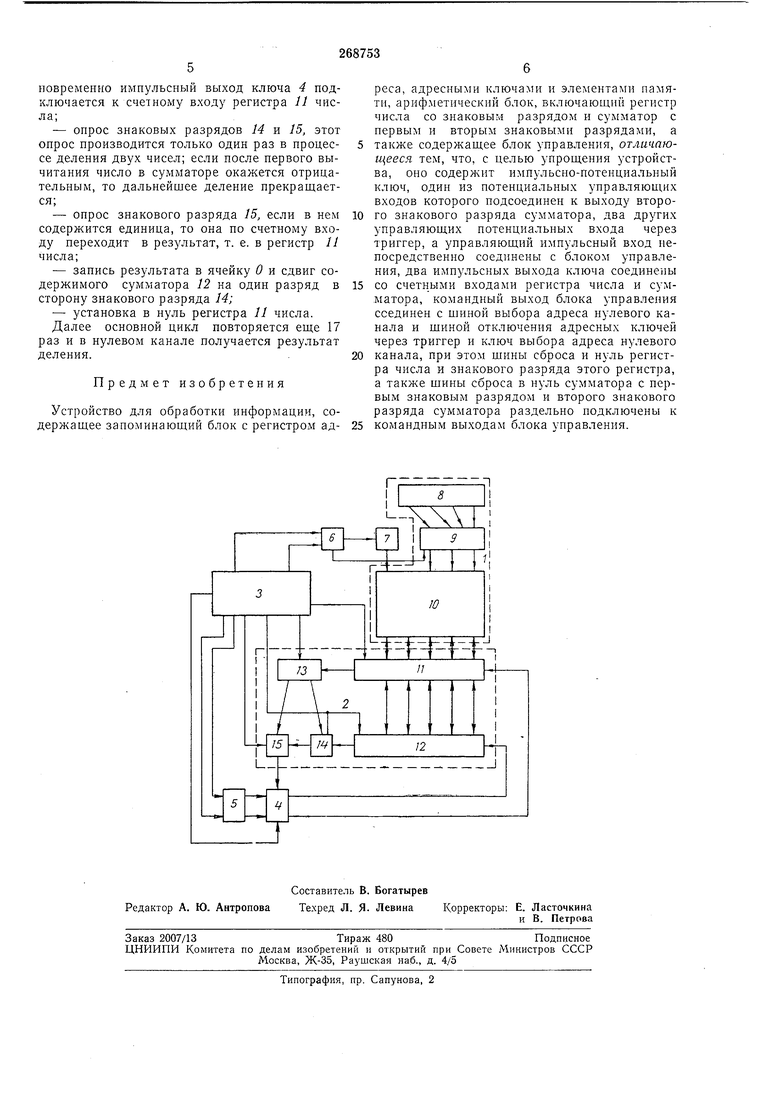

На чертеже показана блок-схема устройства обработки информации.

Устройство содержит запоминающий блок 1, арифметический блок 2, блок управления 3, импульсно-потенциальный ключ 4, триггер 5

управления импульсно-потенциальным ключом, триггер 6 управления ключом выбора адреса нулевого канала и ключ 7 выбора адреса нулевого канала.

Запоминающий блок 1 состоит из регистра

8 адреса, адресных ключей 9 и элементов памяти 10, а арифметический блок 2 - из регистра // числа, сумматора 12, знакового разряда 13 регистра числа и знаковых разрядов 14 и 15 сумматора.

Регистр 8 адреса потенциальными входами триггеров соединен со входами адресных ключей 9, выходы которых подсоединены к элементам памяти 10. Импульсные выходы запоминающего блока соединены с импульсными

входами триггеров регистра 11 числа, импульсные выходы и входы которого связаны с импульсными входами и выходами сумматора 12 соответственно. Выход последнего старщего триггера регистра числа соединен со счетвходы установки в нуль этого разряда и регистра числа раздельно подсоединены к блоку унравления 3. Выход последнего триггера сумматора соединен со счетным входом знакового разряда 14, выход которого соединен со .счетным входом знакового разряда 15, причем вход установки в нуль знакового разряда 15 отдельно от входа установки в нуль сумматора и знакового разряда 14 подключен к бло.ку управления. Импульсный выход знакового разряда 13 подключен к импульсным входам знаковых разрядов 14 и 15. Потенциальный выход знакового разряда 15 соединен с импульсно-потенциальным ключом 4, первый выход которого соединен со счетным входом сумматора, а второй - со счетным входом регистра числа. Триггер 5 управления ключом 4 двумя своими потенциальными выходами соединен с потенциальными входами этого ключа, а импульсный вход ключа 4 - с блоком управления. Импульсные входы триггера 5 соединены с блоком управления. С блоком унрав-. ления соединены также импульсные входы триггера 6 обращения к нулевому каналу, первый потенциальный выход которого соединен со входом ключа 7 выбора адреса нулевого канала, а второй выход-с адресными ключами 9.

Устройство обработки работает следующим образом.

В качестве примера нредположим, что емкость одного канала запоминающего блока 218 - I. Все операции, которые рассматриваются ниже, производятся по программе при помощи программных импульсов, вырабатываемых блоком управления.

При умножении двух чисел множимое записано в ячейке А элементов памяти 10, множижель - в ячейке В, результат получится в нулевом канале-ячейке 0. Перед выполнением операции умножения производится предварительная установка в нуль регистра )/ числа со знаковым разрядом 13 и сумматора 12 со знаковыми разрядами 14 и 15.

Ключ 4 стационарно подключается своим импульсным выходом к счетному входу регистра 11 числа. Операция умножения производится в следующем порядке:

-обращение к ячейке В элементов памяти 10;

-считывание из ячейки В множителя (так как знаковый разряд 13 не связан с запоминающим блоком /, то в нем всегда после считывания будет нуль);

-сдвиг на один разряд множителя в регистре 11 числа, при этом старший разряд множителя оказывается в знаковом разряде 13:

-запись в ячейку В оставщихся разрядов множителя, при этом 17 разряд множителя находится на месте 18 разряда;

-установка в нуль регистра 11 числа; знаковый разряд 13 в нуль не устанавливается (счетный вход знакового 18 разряда блокирован);

-обращение к ячейке А элементов памяти 10;

-считывание из ячейки А множимого;

-онрос знакового разряда 13, если в нем содержится единица, то передача множимого

в сумматор параллельным кодом; знаковый разряд 13 в передаче не участвует;

-запись множимого в ячейку А;

-установка в пуль регистра 11 числа; - обращение к нулевому каналу;

-считывание числа из ячейки 0;

-опрос знакового разряда 15 через ключ 4, если в знаковом разряде 15 содержится единица, ноявивщаяся в результате суммирования, то по счетному входу она нерейдет в регистр 11 числа, т. е. прибавится к результату;

-сдвиг на один разряд содерл :имого регистра // числа и сумматора 12;

- опрос знакового разряда 15 через ключ 4, если в нем содержится единица, то .по счетному входу она перейдет в результат;

-запись результата в ячейку 0;

-установка в нуль регистра 11 числа и знакового разряда 15.

Далее цикл новторяется 17 раз и в нулевом канале (в ячейке 0) получается произведение. При делении двух чисел делимое записано в ячейке А элементов памяти 10, делитель - в ячейке В, результат получится в нулевом канале-ячейке 0. Перед выполнением операции деления производится предварительная установка в нуль регистра 11 числа, сумматора 12 и знаковых разрядов 13-15. Ключ 4 управляется триггером 5 в процессе операции деления.

Производится деление в следующем порядке.

Подготовительная операция:

- обращение к ячейке А элементов памяти 10;

-считывание делимого из ячейки А;

-передача делимого из регистра // числа в сумматор 12 и знакового разряда 13 в знаковые разряды 14 и 15;

-запись делимого обратно в ячейку А;

-установка в нуль регистра // числа; Основной цикл:

-обращение к ячейке В;

- считывание делителя из ячейки В;

-передача делителя из регистра числа // в сумматоре 12 в обратном коде вместе со знаком 13; одновременно импульсный выход ключа 4 подключается к счетному входу сумматора 12; при подключении импульсного выхода ключа 4 на счетный вход сумматора переполнение знакового разряда 15 проходит на счетный вход сумматора непосредственно, без опроса этого разряда;

- запись делителя в ячейку В;

-установка в нуль регистра 11 числа;

-обращение к нулевому каналу;

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для умножения с накоплением | 1988 |

|

SU1509876A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| УСТРОЙСТВО ОБРАБОТКИ ИНФОРМАЦИИ ДЛЯ МНОГОКАНАЛЬНЫХ АНАЛИЗАТОРОВ | 1973 |

|

SU377792A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА С АВТОМАТИЧЕСКИМ ПРОГРАММИРОВАНИЕМ И МИКРОПРОГРАММНЫМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1964 |

|

SU224161A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

Даты

1970-01-01—Публикация