4s

Т 1Г. /ПГ т

Чг

ел

о ;о

00

sj

о

гт°

и Множимые Ннотиты «

SuKoiH резуль- ,тата

фие.1

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ..

Целью изобретения является повышение быстродействия при вычислении суммы парных произведений.

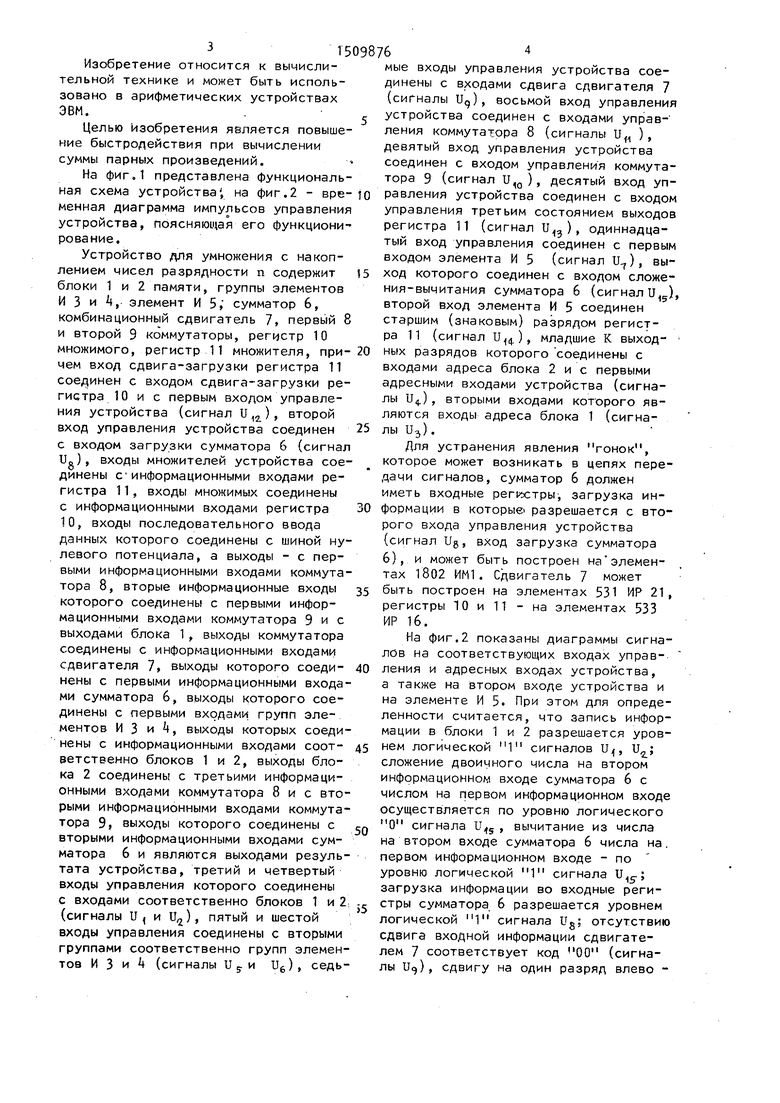

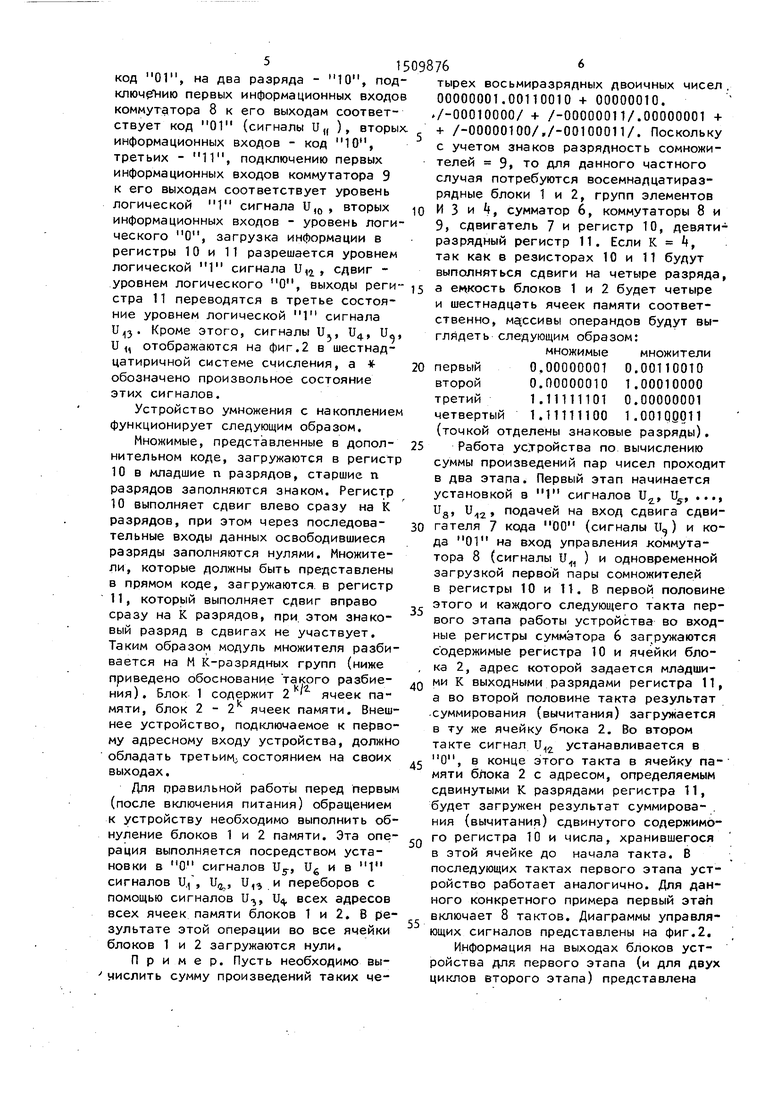

На фиг.1 представлена функциональная схема устройства , на фиг.2 - временная диаграмма импульсов управления устройства, поясняю1цая его функциони- рованне.

Устройство для умножения с накоплением чисел разрядности п содержит блоки 1 и 2 памяти, группы элементов И 3 и 4, элемент И 5, сумматор 6, комбинационный сдвигатель 7, первый 8 и второй 9 коммутаторы, регистр 10

множимого, регистр 11 множителя, при- чем вход сдвига-загрузки регистра 11 соединен с входом сдвига-загрузки регистра 10 и с первым входом управления устройства (сигнал U ,2.) второй вход управления устройства соединен с входом загрузки сумматора 6 (сигнал Uo), входы множителей устройства соединены С информационными входами регистра 11, входы множимых соединены с информационными входами регистра 10, входы последовательного ввода данных которого соединены с шиной нулевого потенциала, а выходы - с первыми информационными входами коммутатора 8, вторые информационные входы которого соединены с первыми информационными входами коммутатора 9 и с выходами блока 1, выходы коммутатора соединены с информационными входами сдвигателя 7, выходы которого соединены с первыми информационными входами сумматора 6, выходы которого соединены с первыми входами групп элементов И 3 и , выходы которых соединены с информационными входами соот- ветственно блоков 1 и 2, выходы блока 2 соединены с третьими информационными входами коммутатора Вис вторыми информационными входами коммутатора 9, выходы которого соединены с вторыми информационными входами сумматора 6 и являются выходами результата устройства, третий и четвертый входы управления которого соединены с входами соответственно блоков 1 и 2 (сигналы и, и и), пятый и шестой входы управления соединены с вторыми группами соответственно групп элементов И 3 и 4 (сигналы и 5-и U) , седь

мые входы управления устройства соединены с входами сдвига сдвигателя 7 (сигналы Uq), восьмой вход управления устройства соединен с входами управ- ления коммутатора 8 (сигналы U,;, ) , девятый вход управления устройства соединен с входом управления коммутатора 9 (сигнал U,g), десятый вход управления устройства соединен с входом управления третьим состоянием выходов регистра 11 (сигнал U), одиннадцатый вход управления соединен с первым входом элемента И 5 (сигнал U), выход которого соединен с входом сложения-вычитания сумматора 6 (сигнал U,), второй вход элемента И 5 соединен старшим (знаковым) разрядом регистра 11 (сигнал ), младшие К выход- ных разрядов которого соединены с входами адреса блока 2 и с первыми адресными входами устройства (сигналы U4.), вторыми входами которого являются входы адреса блока 1 (сигналы и).

Для устранения явления которое может возникать в дачи сигналов, сумматор 6 иметь входные , загрузка

формации в которые разрешается с рого входа управления устройства (сигнал Ug, вход загрузка сумматора 6), и может быть построен на элементах l802 ИМ1. Сдвигатель 7 может быть построен на элементах 531 ИР 21, регистры 10 и 11 - на элементах 533 ИР 16.

На фиг.2 показаны диаграммы сигналов на соответствующих входах управления и адресных входах устройства, а также на втором входе устройства и на элементе И 5 При этом для определенности считается, что запись информации в блоки 1 и 2 разрешается уровцепях передолжен

ин- в тонем логической 1 сигналов и, сложение двоичного числа на втором информационном входе сумматора 6 с числом на первом информационном входе осуществляется по уровню логического О сигнала , вычитание из числа на втором входе сумматора 6 числа на. первом информационном входе - по уровню логической 1 сигнала загрузка информации во входные регистры сумматора 6 разрешается уровнем логической 1 сигнала Ug; отсутствию сдвига входной информации сдвигате- лем 7 соответствует код 00 (сигналы и.), сдвигу на один разряд влево 51509876

разряда - 10, под- информационных входов его выходам соответ(сигналы U,, ), вторых ходов - код 10, подключению первых ходов коммутатора 9 ответствует уровень

ты 00 /+с те сл ря И 9, ра та вы 15 э и ст гл

логической 1 сигнала U, , вторых IQ информационных входов - уровень логического О, загрузка информации в регистры 10 и 11 разрешается уровнем логической 1 сигнала U,, , сдвиг - уровнем логического О, выходы регистра 11 переводятся в третье состоясигнала

ние уровнем логической 1 Кроме этого, сигналы U,, U

и

5 4

и.

отображаются на фиг.2 в шестнадцатиричной системе счисления, а обозначено произвольное состояние этих сигналов.

Устройство умножения с накоплением функционирует следующим образом.

Множимые, представленные в дополнительном коде, загружаются в регистр 10 в младшие п разрядов, старшие п разрядов заполняются знаком. Регистр 10 выполняет сдвиг влево сразу на К разрядов, при этом через последовательные входы данных освободившиеся разряды заполняются нулями. Множители, которые должны быть представлены в прямом коде, загружаются, в регистр 11, которь1й выполняет сдвиг вправо сразу на К разрядов, при. этом знаковый разряд в сдвигах не участвует. Таким образом модуль множителя разбивается на М К-разрядных групп (ниже приведено обоснование такого разбиения). Блок 1 содержит 2 ячеек памяти, блок 2-2 ячеек памяти. Внешнее устройство, подключаемое к первому адресному входу устройства, должно обладать третьим состоянием на своих выходах.

Для правильной работы перед первым (после включения питания) обращением к устройству необходимо выполнить обнуление блоков 1 и 2 памяти. Эта операция выполняется посредством уста15

20

35

40

25

30

45

50

новки в О сигналов U

5

Ug И В

Т

сигналов и,,, и, и,з и переборов с помощью сигналов U, , всех адресов всех ячеек памяти блоков 1 и 2. В результате этой операции во все ячейки блоков 1 и 2 загружаются нули.

Пример. Пусть необходимо вы- яислить сумму произведений таких че

IQ

тырех восьмиразрядных двоичных чисел , 00000001.00110010 + 00000010. /00010000/ + /-00000011/.00000001 + + /-00000100/,/-00100011/. Поскольку с учетом знаков разрядность сомножителей 9, то для данного частного случая потребуются восемнадцатиразрядные блоки 1 и 2, групп элементов И 3 и , сумматор 6, коммутаторы 8 и 9, сдвигатель 7 и регистр 10, девятиразрядный регистр 11. Если К , так как в резисторах 10 и 11 будут выполняться сдвиги на четыре разряда, 15 э емкость блоков 1 и 2 будет четыре и шестнадцать ячеек памяти соответственно, массивы операндов будут выглядеть следующим образом:

множимые множители 0,00000001 0.00110010 0.00000010 1.00010000 1.1П11101 0.00000001 1.11111100 1.001QQ011

20 первый второй третий четвертый

35

40

(точкой отделены знаковые разряды).

25 Работа устройства по вычислению суммы произведений пар чисел проходит в два этапа. Первый этап начинается

установкой в 1 сигналов V,

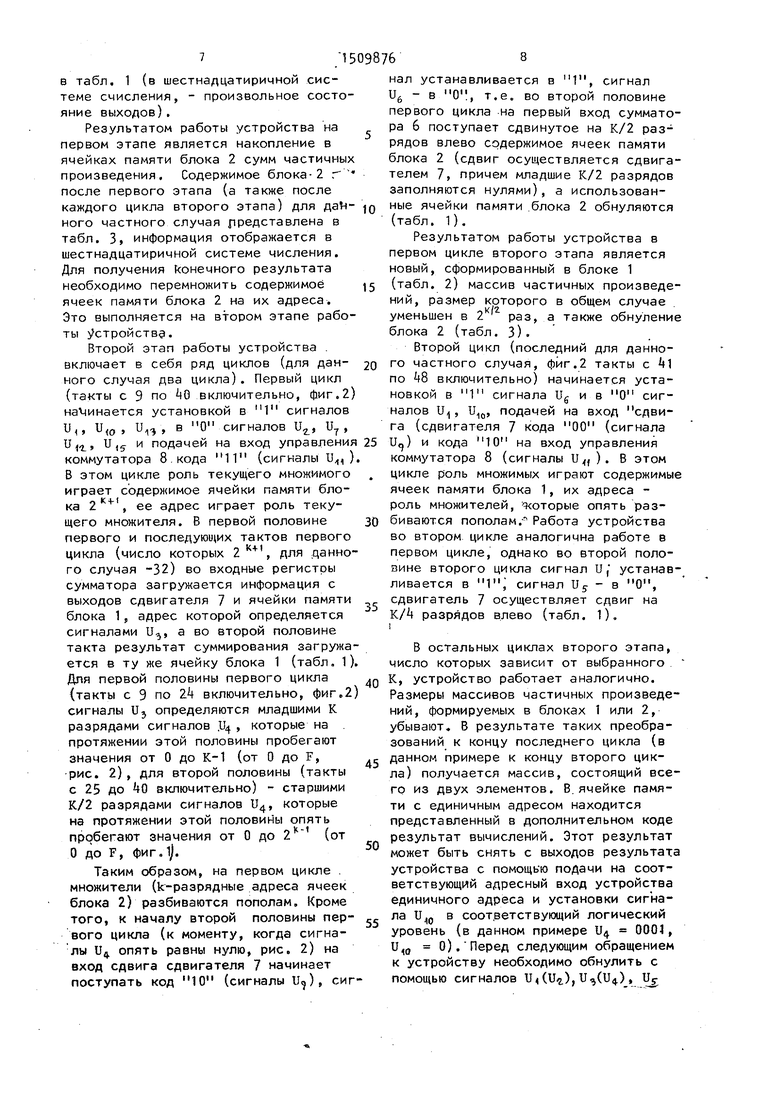

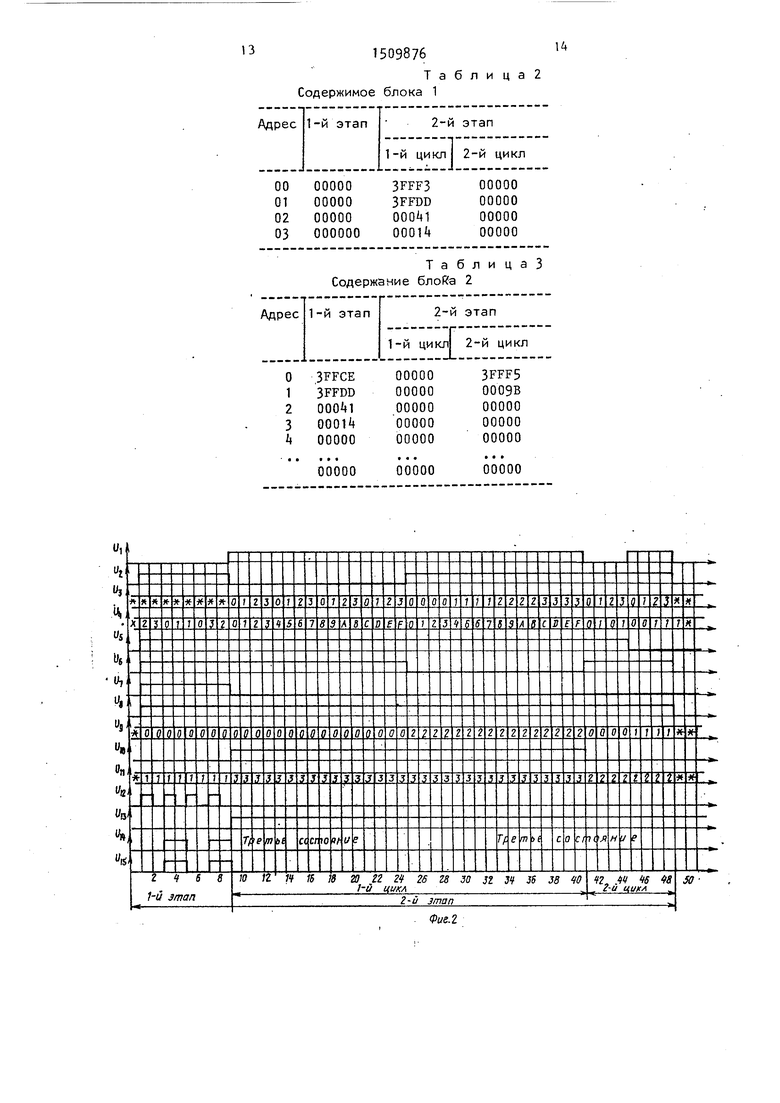

Ug, , подачей на вход сдвига сдви30 гателя 7 кода 00 (сигналы 1Ц ) и кода 01 на вход управления коммутатора 8 (сигналы и ) и одновременной загрузкой первой пары сомножителей в регистры 10 и 11. В первой половине этого и каждого следующего такта первого этапа работы устройства во входные регистры сумматора 6 заг.ружаются содержимые регистра 10 и ячейки блока 2, адрес которой задается младшими К выходными разрядами регистра П, а во второй половине такта результат суммирования (вычитания) загружается в ту же ячейку бпока 2. Во втором такте сигнал U устанавливается в О, в конце этого такта в ячейку памяти блока 2 с адресом, определяемым сдвинутыми к разрядами регистра 11, будет загружен результат суммирова- . ния (вычитания) сдвинутого содержимого регистра 10 и числа, хранившегося в этой ячейке до начала такта. В последующих тактах первого этапа устройство работает аналогично. Для данного конкретного примера первый этап включает 8 тактов. Диаграммы управляющих сигналов представлены на фиг.2. Информация на выходах блоков устройства для первого этапа (и для двух циклов второго этапа) представлена

45

50

55

в табл. 1 (в шестнадцатиричной системе счисления, - произвольное состояние выходов).

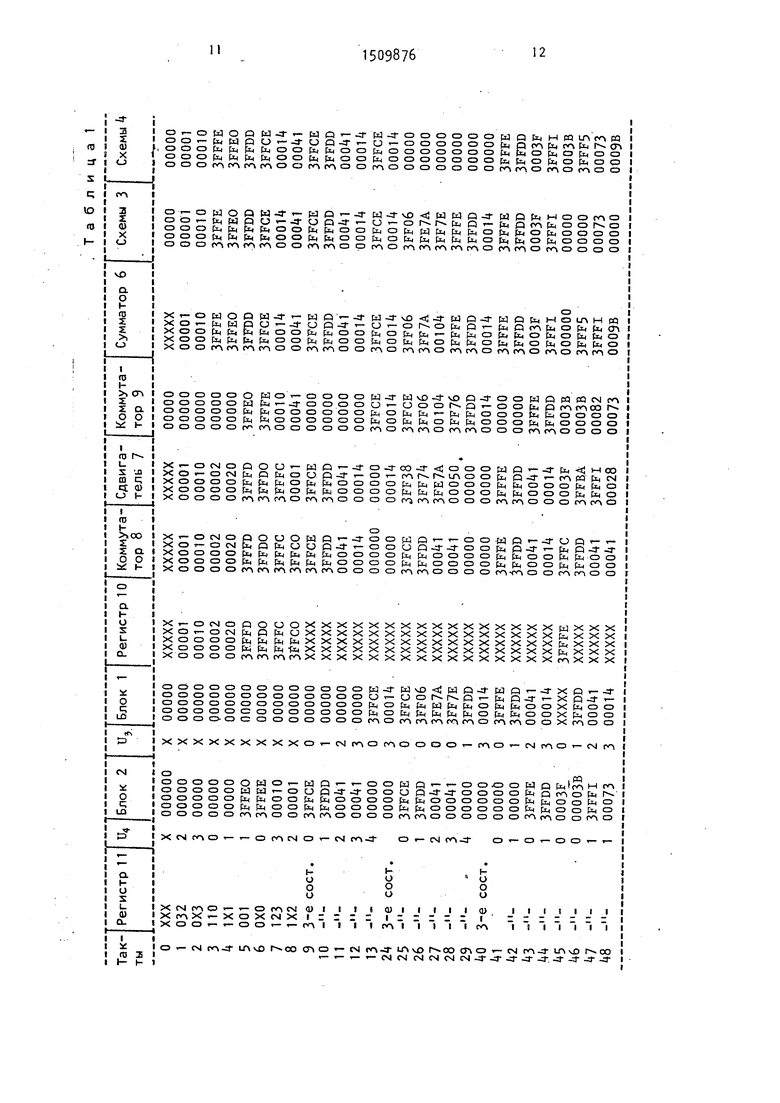

Результатом работы устройства на первом этапе является накопление в ячейках памяти блока 2 сумм частичных произведения. Содержимое блока-2 г после первого этапа (а также после каждого цикла второго этапа) для иого частного случая представлена в табл. 3 информация отображается в шестнадцатиричной системе числения. Для получения Конечного результата необходимо перемножить содержимое ячеек памяти блока 2 на их адреса. Это выполняется на втором этапе работы стройств.

Второй этап работы устройства . включает в себя ряд циклов (для данного случая два цикла). Первый цикл {такты с 9 по 0 включительно, фиг.2) на Минается установкой в 1 сигналов и,, , и , в О сигналов V, U , U,, и подачей на вход управления коммутатора 8.кода 11 (сигналы U, ) В этом цикле роль текущего множимого играет содержимое ячейки памяти блока , ее адрес играет роль текущего множителя. В первой половине первого и последующих тактов первого цикла (число которых , для данного случая -32) во входные регистры сумматора загружается информация с выходов сдвигателя 7 и ячейки памяти блока 1, адрес которой определяется сигналами , а во второй половине такта результат суммирования загружается в ту же ячейку блока 1 (табл. 1). Для первой половины первого цикла (такты с 9 по Z4 включительно, фиг.2) сигналы Uj определяются младшими К разрядами сигналов Щ , которые на . протяжении этой половины пробегают значения от О до К-1 (от О до F, рис. 2) , для второй половины (такты с 25 до kQ включительно) - старшими К/2 разрядами сигналов U, которые на протяжении этой половины опять пробегают значения от О до (от О до F, фиг.1).

Таким образом, на первом цикле . множители (k-разрядные адреса ячеек блока 2) разбиваются пополам. Кроме того, к началу второй половины первого цикла (к моменту, когда сигналы V опять равны нулю, рис. 2) на вход сдвига сдвигателя 7 начинает поступать код 10 (сигналы U), сиг

0

5

D

5

0

5

0

5

нал устанавливается в 1, сигнал Ug - в О, т.е. во второй половине первого цикла на первый вход сумматора 6 поступает сдвинутое на К/2 разрядов влево содержимое ячеек памяти блока 2 (сдвиг осуществляется сдвига- телем 7, причем младшие К/2 разрядов заполняются нулями), а использованные ячейки памяти блока 2 обнуляются (табл. 1).

Результатом работы устройства в первом цикле второго этапа является новый, сформированный в блоке 1 (табл. 2) массив частичных произведений, размер которого в общем случае уменьшен в раз, а также обнуление блока 2 (табл. 3).

Второй цикл (последний для данного частного случая, фиг.2 такты с 1 по 8 включительно) начинается установкой в 1 сигнала Ug и в О сигналов и, ,, подачей на вход сдвига (сдвигателя 7 кода 00 (сигнала U,j) и кода 10 на вход управления коммутатора 8 (сигналы U,). В этом цикле роль множимых играют содержимые ячеек памяти блока 1, их адреса - роль множителей, ч оторые опять разбиваются пополам.- Работа устройства во втором цикле аналогична работе в первом цикле, однако во второй половине второго цикла сигнал U, устанавливается в сигнал Uj - в О, сдвигатель 7 осуществляет сдвиг на

K/k разрядов влево (табл. 1).

1

В остальных циклах второго этапа, число которых зависит от выбранного К, устройство работает аналогично. Размеры массивов частичных произведений, формируемых в блоках 1 или 2, убывают. В результате таких преобразований к концу последнего цикла (в данном примере к концу второго цикла) получается массив, состоящий всего из двух элементов. В. ячейке памяти с единичным адресом находится представленный в дополнительном коде результат вычислений. Этот результат может быть снять с выходов результата устройства с помощь ю подачи на соответствующий адресный вход устройства единичного адреса и установки сигнала и,, в соот.ветствующий логический уровень (в данном примере U 0001, U,g 0). Перед следующим обращением к устройству необходимо обнулить с помощью сигналов U4(U), ) Ug:

1509876

(Ug) ячейку памяти с единичным адресом соответствующего блока (ячейку с нулевым адресом можно не обнулять, это не повлияет на дальнейшую работу устройства), после чего устройство готового к работе со следующим массивом операндов.

Разрядность блоков 1 и 2, групп

10

первого коммутатора соединены с ин- формационными входами сдвигателя, выходы которого соединены с первыми информационными входами сумматора, выходы которого соединены с первыми : входами первой и второй групп элементов И, выходы которых соединены с информационными входами соответственно

элементов 3 и , сумматора 6, сдвига- Q первого блока памяти и второго блока

теля 7 и KOMMytaTopoB 8 и 9 может быть больше 2п в зависимости от количества вводимых разрядов расширения.

Формула изобретения 5

памяти, выходы которого соединены с третьими информационными входами первого коммутатора и с вторыми информационными входами второго коммутатора, выходы которого соединены с вторыми информационными входами сумматора и являются выходами результата устройства, третий и четвертый входы управления которого соединены с входами записи соответственно первого и второго блоков памяти, пятый и шестой входы управления устройства соединен с вторыми входами соответственно первой и второй групп элементов И, седьмой вход управления устройства соединен с входом сдвига сдвигателя, восьмой вход управления устройства соединен с входом управления первого коммутатора, девятый вход управления устройства соединен с входом управления второго коммутатора, дес ятый вход управления устройства соединен с входом управления третьим состоянием выходов регистра множителя, одиннадцатый вход управления устройства соединен с первым входон элемента И, выход которого соединен с входом сложения вычитания сумматора, а второй вход соединен с выходом старшего знакового разряда регистра множителя, выходы младших К разрядов которого соединены с входами устройства, вторые адресные входы которого соединены с входами адреса первого блока памяти.

Устройство для умножения с накоплением, содержащее регистр множимого, сумматор, регистр множителя, вход сдвига-загруз ки которого соединен с входом сдвига-загрузки регистра множимого и с первым входом управления устройства, второй вход управления устройства соединен .с входом загрузки сумматора, информационные входы регистра множителя соединены с входами множителей устройства, информационные входы регистра множимого соединены с входами множимых устройства, входы последовательного ввода данных регистра множимого соединены с шиной нулевого потенциала устройства, отличающееся тем, чт о, с целью повышения быстродействия, в него введены первый и второй блоки памяти, первая и вторая группы элементов И первый и второй коммутаторы, сдвига- тель, элемент И, выходы регистра множимого соединены с первыми информационными входами первого коммутатора, вторые информационные входы которого соединены с первыми информационными входами второго коммутатора и с выходами первого блока памяти, а выходы

10

первого коммутатора соединены с ин- ч формационными входами сдвигателя, выходы которого соединены с первыми информационными входами сумматора, выходы которого соединены с первыми : входами первой и второй групп элементов И, выходы которых соединены с информационными входами соответственно

0

5

5

0.

5

D

памяти, выходы которого соединены с третьими информационными входами первого коммутатора и с вторыми информационными входами второго коммутатора, выходы которого соединены с вторыми информационными входами сумматора и являются выходами результата устройства, третий и четвертый входы управления которого соединены с входами записи соответственно первого и второго блоков памяти, пятый и шестой входы управления устройства соединен с вторыми входами соответственно первой и второй групп элементов И, седьмой вход управления устройства соединен с входом сдвига сдвигателя, восьмой вход управления устройства соединен с входом управления первого коммутатора, девятый вход управления устройства соединен с входом управления второго коммутатора, дес ятый вход управления устройства соединен с входом управления третьим состоянием выходов регистра множителя, одиннадцатый вход управления устройства соединен с первым входон элемента И, выход которого соединен с входом сложения вычитания сумматора, а второй вход соединен с выходом старшего знакового разряда регистра множителя, выходы младших К разрядов которого соединены с входами устройства, вторые адресные входы которого соединены с входами адреса первого блока памяти.

13

1509876

Таблица2 Содержимое блока 1

14

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения с накоплением комплексных чисел | 1988 |

|

SU1587230A1 |

| Устройство для умножения с накоплением | 1987 |

|

SU1451683A1 |

| Устройство для умножения с накоплением комплексных чисел | 1987 |

|

SU1478211A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1287156A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ. Цель изобретения - повышение быстродействия при вычислении сумм парных произведений. Устройство содержит регистр 10 множимого, сумматор 6, регистр 11 множителя, блоки 1 и 2 памяти, группы элементов И 3 и 4, элемент И 5, сдвигатель 7 и коммутаторы 8 и 9. Функционирование устройства включает два цикла: в течение первого цикла формируются и заносятся в блок два значения частичных произведений величин AI на к - разрядные группы чисел XI. При этом в ячейке с адресом BI формируется число S =Σ AJ I.2K, где J - номер числа X, в коде которого присутствует группа разрядов, образующих код I

к - вес этой группы. Во втором цикле производится суммирование частичных произведений. 2 ил., 3 табл.

ТаблицаЗ Содержание блоКа 2

| Устройство для вычисления сумм произведений | 1973 |

|

SU480077A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Карцев М.А | |||

| Арифметика цифровых машин.- М.: Наука, 19б9, с | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

Авторы

Даты

1989-09-23—Публикация

1988-01-26—Подача