Предложенное устройство относится к вычислительной технике и может быть использовано в управляющих цифровых вычислительных машинах и устройствах дискретной автоматики.

Известны устройства для определения приоритетности сигналов, содержащие тряггерные регистры, схемы совпадения и сборки.

Недостатком этих устройств является значительное увеличение количества оборудования с увеличением числа абонентов (разрядов).

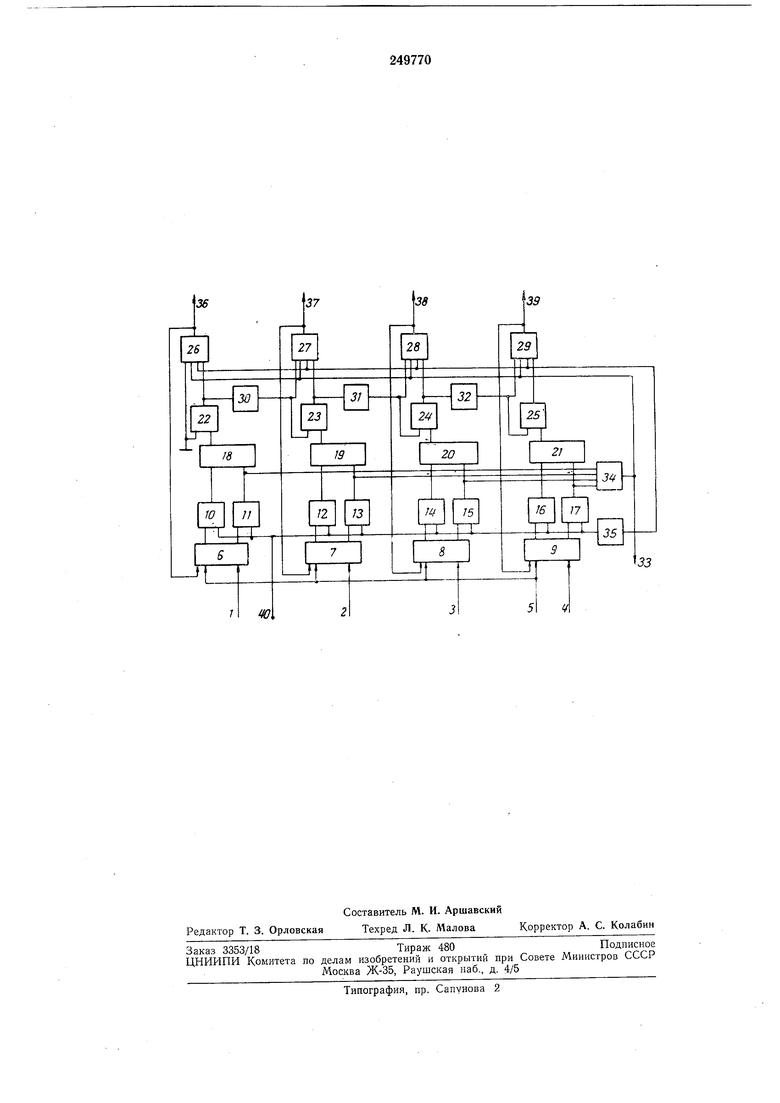

Предложенное устройство отличается тем, что выход каждого разряда промежуточного регистра соединен с .пер-вым входом сборки данного разряда, второй вход которой соединен с первым входом схемы совпадения данного разряда и с выходом (п-1)-го межразрядного инвертора. Выход сборки соединен со вторым входом схемы совпадения и с входом л-го межразрядного инвертора, третьи входы схем совпадения объединены и подключены к выходу сборки, входы которой соединены с выходами всех вентилей блокировки, входы вентилей блокировки соединены с единичными выходами триггеров входного регистра.

Предположим, что поступает четыре сигнала «Запрос по шинам 1-4. Общий сброс входного регистра производится но щине 5. Входной запоминающий регистр выполнен

на триггерах 6-9. Единичный и нулевой выходы триггеров 6-9 канодого разряда входного запоминающего регистра соединяются с единичным и нулевым входами триггеров промежуточного запоминающего регистра через

вентили блокировки 10-17. Нулевые выходы триггеров 18-21 промежуточного запоминающего регистра соединяются со вторыми входами сборок 22-25. Выход каждой сборки 22- 25 соединяется с четвертым входом схем совпадения 26-29 каждого разряда соответственно, а также через межразрядные инверторы 30-32 - с первым входом схем совпадения 27-29 и с первым входом сборок 23-25 последующего (менее приоритетного) разряда.

На первый вход сборки 22 и схемы совпадения 26 первого разряда (разряда наибольшей приоритетности) подается нулевой потенциал, lia вторые входы схем совпадения 25-29 подается управляющий сигнал по щине 33 со

сборки 54, который одновременно поступает в устройство управления. На сборку 34 поступают сигналы с выходов вентилей блокировки 11, 13, 15 VL 17, которые подключены к единичным входам триггеров /S-21 промежуточного

схем совпадения 26-29 подается управляющий сигнал из устройства управления через инвертор 35. На одной из шин 36-39 появится сигнал с выхода соответствующей схемы совпадения в том случае, если один из входных сигналов, поступающих по шинам /-4, окажется наиболее приоритетным в данный момент. Одновременно сигнал с шины 36-39 установит в «О триггер входного запоминающего регистра своего разряда.

Устройство работает следующим образом.

При включении питания все триггеры входного запоминающего регистра устанавливаются в исходное (нулевое) состояние сигналом по шине 5, в результате чего на выходе вентилей блокировки 10, 12, 14, 16 появляется положительный сигнал, который устанавливает триггеры 18-21 промежуточного запоминающего регистра в исходное состояние. После этого устройство готово к работе.

Допустим, что от двух абонентов одновременно поступили имлульсные сигналы по шинам положительной полярности / и 5. Эти сигналы установят в единичное состояние триггеры и S входного запоминающего регистра. Сигналы с единичных выходов этих триггеров через вентили блокировки 11 и 15 устанавливают в единичное состояние триггеры 18 и 20 промежуточного запоминающего регистра. Одновременно на выходе сборки 34 появляется положительный сигнал на шине 33, который подается в устройство управления, а также на вторые входы схем совпадения 26-29, блокируя тем самым возможность выдачи ложного сигнала приоритета с их выходов.

Получив сигнал с шины 33, устройство управления выдает в устройство для определения приоритетности по шине 40 потенциальный сигнал блокировки положительной полярности на время приема приор-итетного сигнала на исполнение. При поступлении из устройства управления сигнала по шине 40 вентили 10-17 закрываются. При этом блокируется передача информации с входного запоминающего регистра на промежуточный запоминающий релистр для предупреждения появления ложных сигналов во время приема приоритетного сигнала на исполнение.

Одновременно сигнал, поступивший по шине 40, через инвертор 35 подается на схемы совпадения 26-29. На выходе схемы совпадения 26 появляется сигнал положительной полярности, который является наиболее приоритетным из пришедших. На выходе схемы совпадения 28 появляется сигнал положительной полярности, поступивший с выхода сборки 22 через межразрядный инвертор 30, сборку 23 и межразрядный инвертор 31. Одновременно сигнал с выхода схемы совпадения 26 по шине 36 подается на нулевой вход .триггера в

данного разряда входного запоминающего регистра, что свидетельствует о приеме приоритетного сигнала на исполнение. После этого устройство управления снимает положительный сигнал по шине 40, и триггер 18 промежуточного запоминающего регистра устанавливается в нулевое состояние сигналом с выхода вентиля блокировки 10. Одновременно положительный сигнал с выхода вентиля блокировки 15 через сборку 34 поступает в устройство управления и на вторые входы схем совпадения 26-29. При этом цикл работы устройства для определения приоритетности совместно с устройством управления аналогичен предшествующему за исключением того, что теперь

на исполнение выдается с устройства менее приоритетный сигнал по шине 38.

Работа устройства для определения приорнтетностй сигналов и его взаимодействие с устройством управления при приходе других сигналов аналогична описанной.

Предмет изобретения

Устройство для определения приоритетности управляющих сигналов, выполненное на потенциальных элементах, содержащее два триггерных регистра, схемы совпадения и сборки, отличающееся тем, что, с целью уменьшения количества оборудования, выход каждого разряда промежуточного регистра соединен с первым входом сборки данного разряда, второй вход которой соединен с первым входом схемы совпадения данного разряда и с выходом (п-1)-го мелсразрядного инвертора, а выход сборки соединен со вторым входом схемы совпадения и с входом п-го мел разрядного инвертора, третьи входы схем совпадения объединены и подключены к выходу сборки, входы которой соединены с выходами всех вентилей блокировки, входы вентилей блокировки соединены с единичными выходами триггеров входного регистра.

Даты

1969-01-01—Публикация