Изобретение относится к области вычислительной техники.

Известны устройства для генерации кода с постоянным числом р единиц, содержащие регистры и логические схемы.5

Недостатком известных устройств являегся их сложность и вследствие этого низкая надежность.

Предложенное устройство отличается от известных тем, что в нем входы блока управле- ю ния сдвигом соединены с выходами соответствующих ячеек от (fe + 1)-й до я-й регистра сдвига, выход блока управления сдвигом соединен с первым входом вентиля, второй вход вентиля соединен с выходом линии задержки, 15 выход вентиля через схему «ИЛИ соединен с тактовыми входами ячеек от первой до ft-й регистра сдвига, выход fe-й ячейки регистра сдвига соединен с первым входом вентиля входного блока, второй вход вентиля входно- 20 го блока соединен с выходом линии задержки, тчход вентиля входного блока через схему «ИЛИ входного блока соединен с входом регистра сдвига, входы схемы «ИЛИ блока упавления сдвигом соединены с выходами со- 25 тветствующих ячеек от (fe+ 1)-й до t-ii реистра сдвига и выходами дещифратора, вхоы дешифратора соединены с выходами ячеек от (t + 1)-й до я-й регистра сдвига и тем, что, целью расщирения функциональных воз- 30

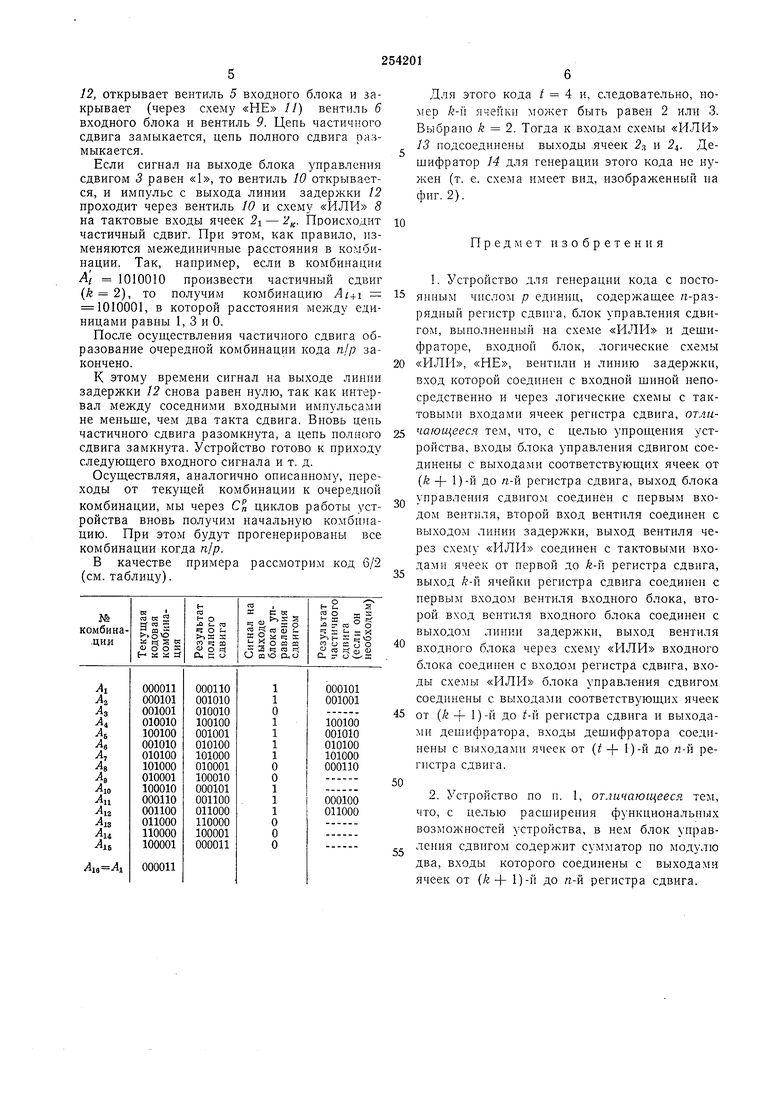

можностей устройства, в нем блок управления сдвигом содержит сумматор по модулю два, входы которого соединены с выходами ячеек от (k + 1)-й до п-н регистра сдвига.

Это позволяет упростить устройство и расщирить его фуикциональные возможности.

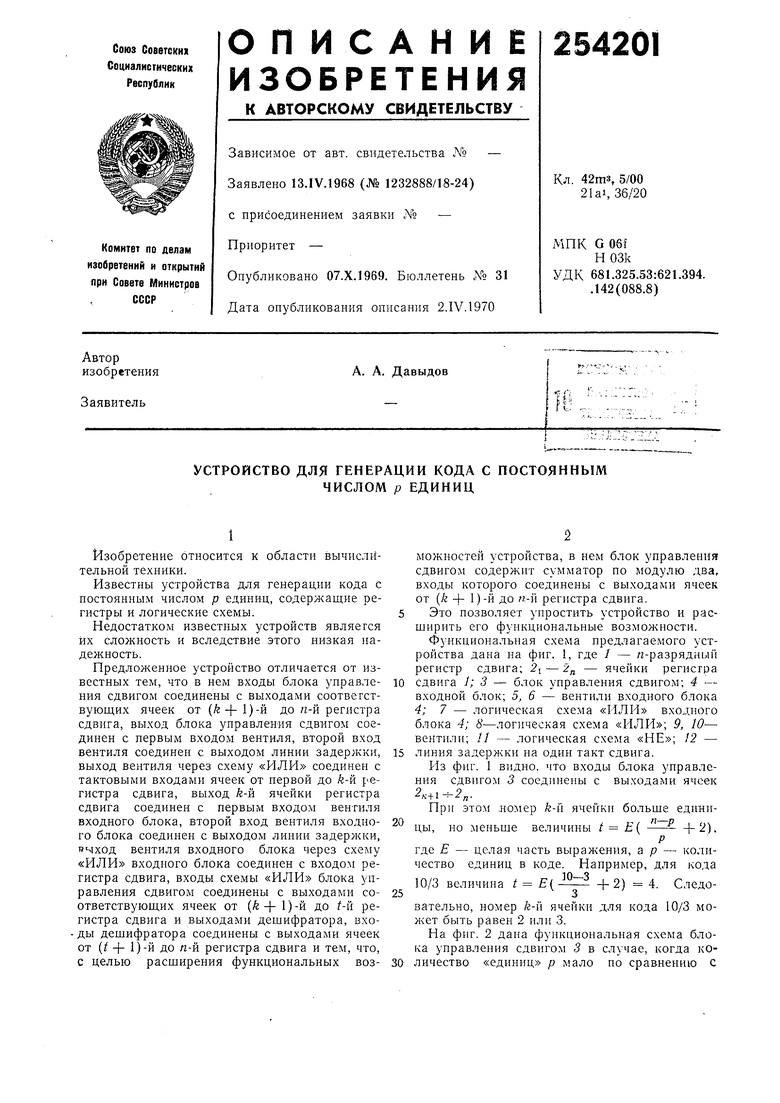

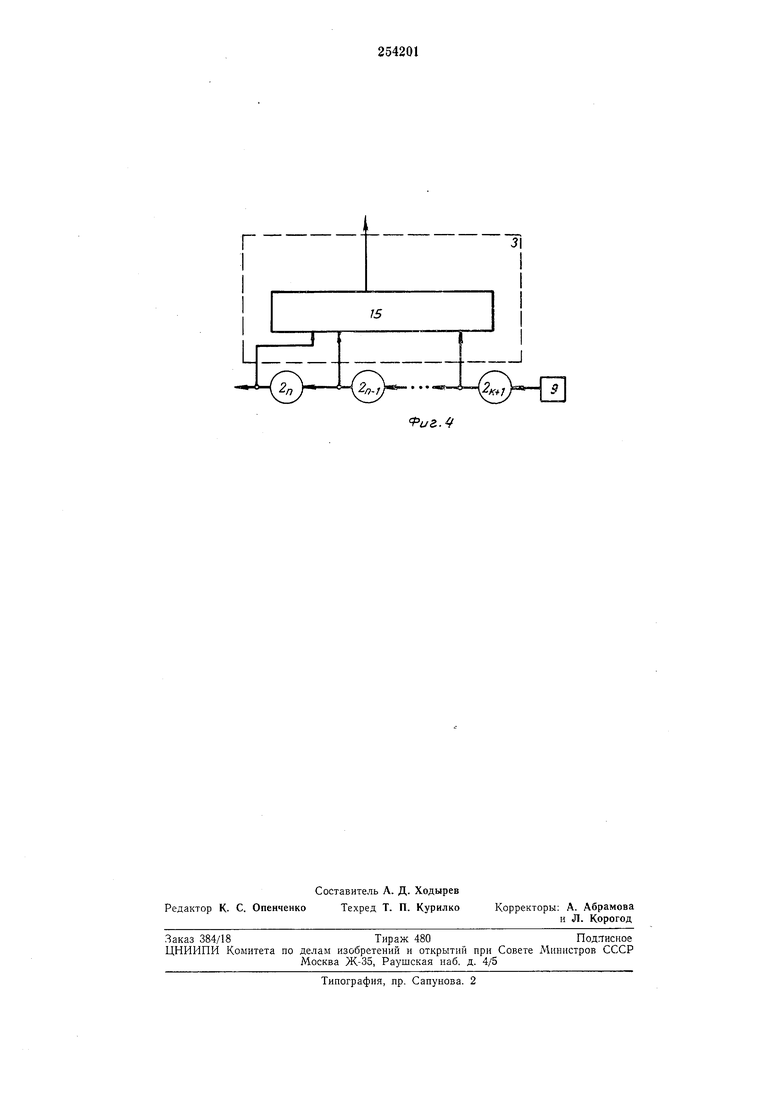

Функциональная схема предлагаемого устройства дана на фиг. 1, где / - я-разрядный регистр сдвига; 2i-2 - ячейки регистра сдвига 1; 3 - блок управления сдвигом; 4 - входной блок; 5,6 - вентили входного блока 4; 7 - логическая схема «1-1ЛИ входного блока 4; 8-логическая схема 9, 10- вентили; // - логическая схема 12 - линия задержки на один такт сдвига.

Из фиг. 1 видно, что входы блока управления сдвигом 3 соединены с выходами ячеек

.

При этом ломер /г-й ячейки больше единия-р

цы, но меньше величины t Е(

2).

где Е - целая часть выралуения, ар - количество единиц в коде. Например, для кода

10-3

10/3 величина t Е( +2) 4. Следовательно, номер /г-й ячейки для кода 10/3 может быть равен 2 или 3.

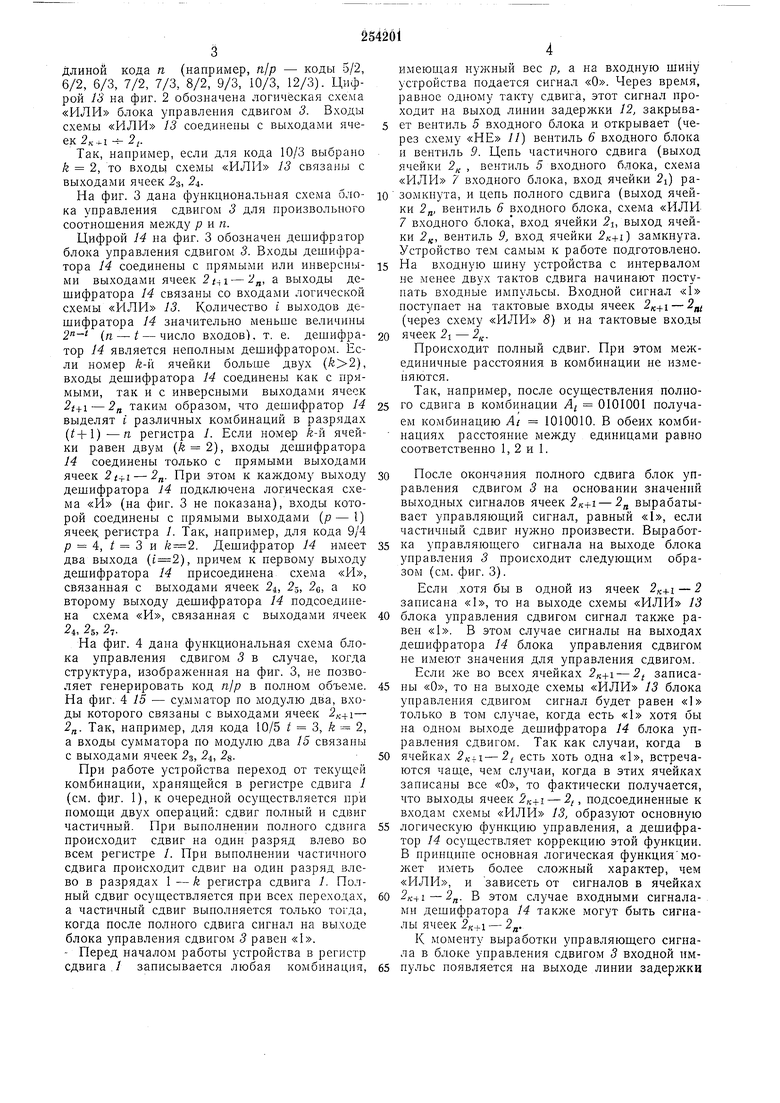

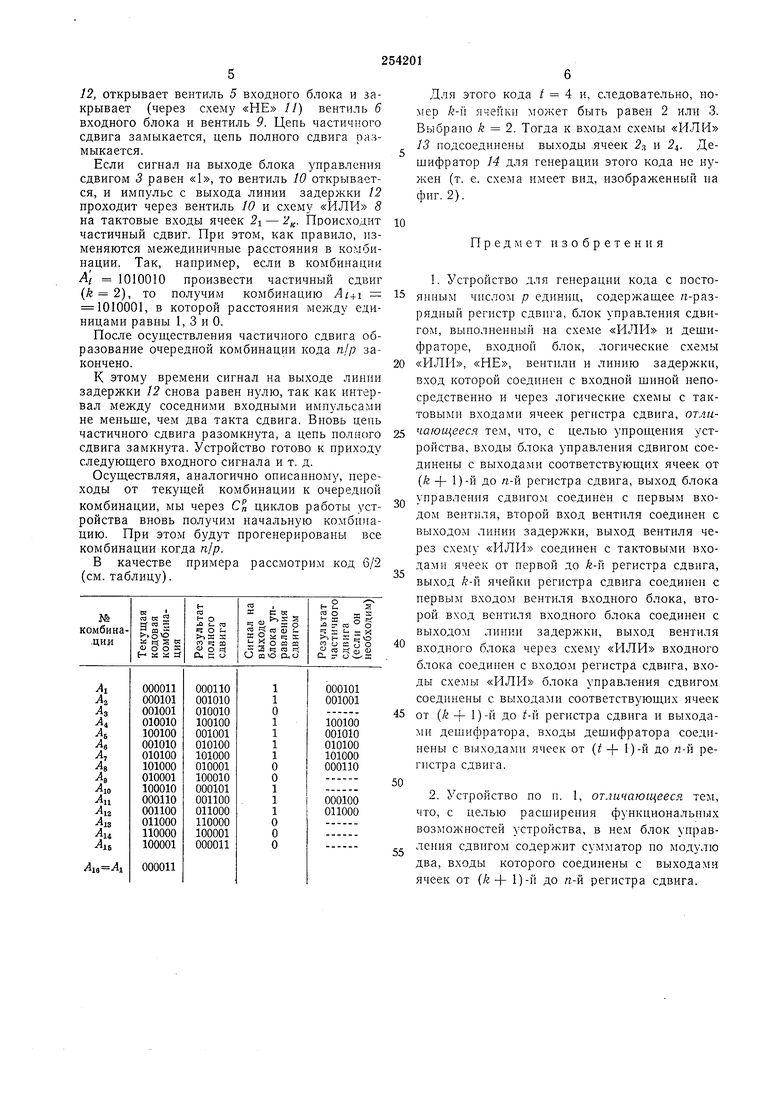

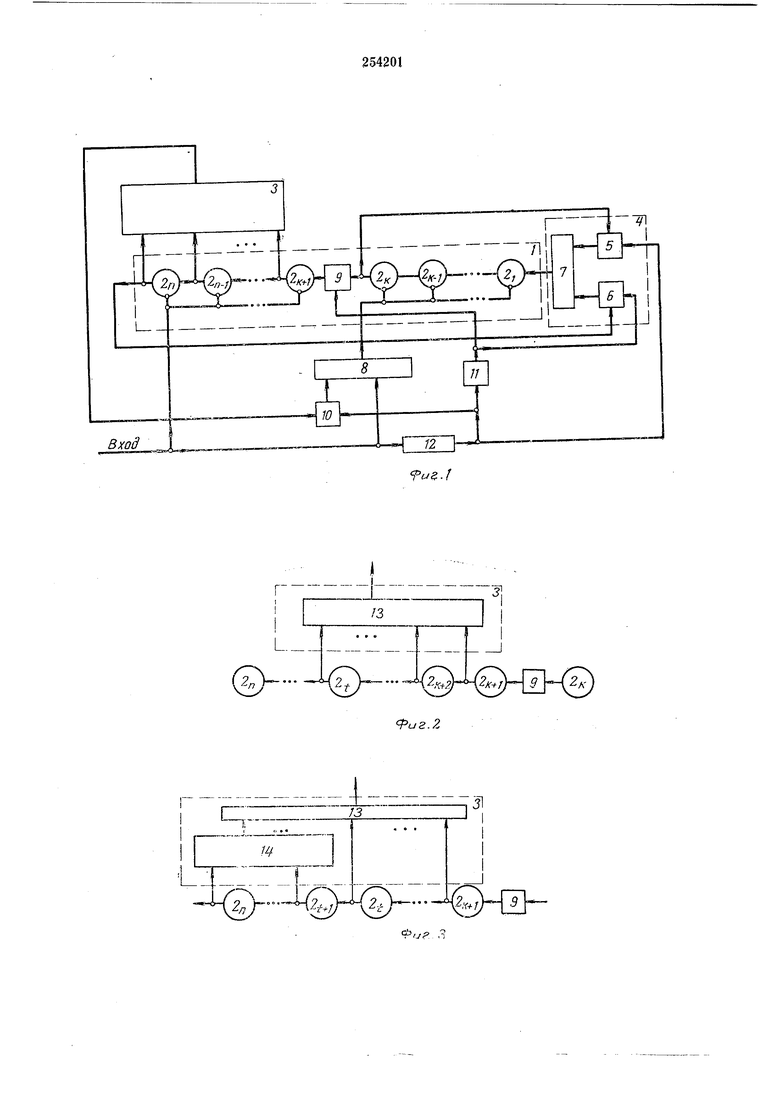

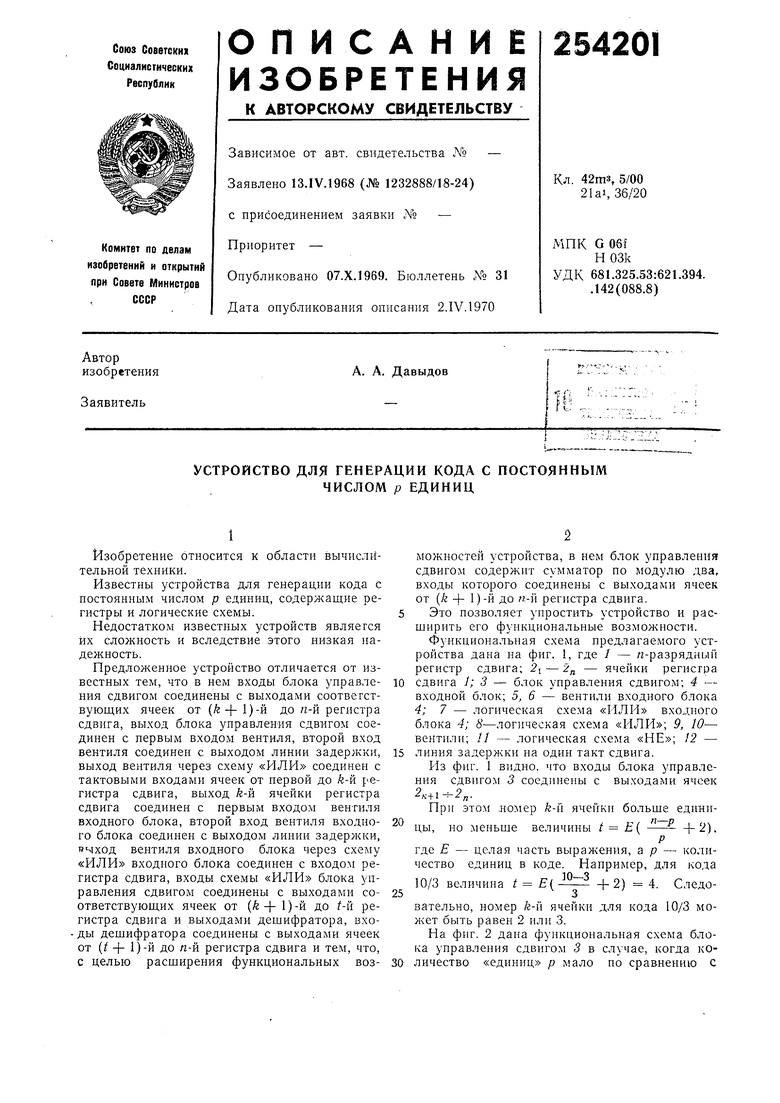

На фиг. 2 дана функциональная схема блока управления сдвигом 3 в случае, когда количество «единиц р мало по сравнению с длиной кода п (например, п/р - коды 5/2, 6/2, 6/3, 7/2, 7/3, 8/2, 9/3, 10/3, 12/3). Цифрой 13 на фиг. 2 обозначена логическая схема «ИЛИ блока управления сдвигом 3. Входы схемы «ИЛИ 13 соединены с выходами ячеек ,. Так, например, если для кода 10/3 выбрано k 2, то входы схемы «ИЛИ 13 связаны с выходами ячеек 2з, 2. На фиг. 3 дана функциональная схема бло-ю ка управления сдвигом 3 для произвольпого соотношения между р и и. Цифрой 14 на фиг. 3 обозначен дешифратор блока управления сдвигом 3. Входы дешифратора 14 соединены с прямыми или инверсны-is ми выходами ячеек - 2„, а выходы дешифратора 14 связаны со входами логической схемы «ИЛИ 13. Количество t выходов дешифратора 14 значительно меньше величины (я - t - число входов), т. е. дешифра-20 тор 14 является неполным дешифратором. Если номер k-ii ячейки больше двух (), входы дешифратора 14 соединены как с прямыми, так и с инверсными выходами ячеек 2t+i - 2„ таким образом, что дешифратор 14 25 Быделят i различных комбинаций в разрядах (+1)-п регистра 1. Если номер k-и ячейки равен двум (А 2), входы дешифратора 14 соединены только с прямыми выходами ячеек 2 t+i - 2„. При этом к каждому выходу ЗО дешифратора 14 подключена логическая схема «И (на фиг. 3 не показана), входы которой соединены с ирямыми выходами (р-I) ячеек регистра 1. Так, нанример, для кода 9/4 / 4, / 3 и /г 2. Дешифратор 14 имеет 35 два выхода (), причем к первому выходу дещифратора 14 присоединена схема «И, связанная с выходами ячеек 2, 2г„ 2, а ко второму выходу дешифратора 14 нодсоедипена схема «И, связанная с выходами ячеек 40 4, 5, 2т. На фиг. 4 дана функциональная схема блока управления сдвигом 3 в случае, когда структура, изображенная на фиг. 3, не позволяет генерировать код п/р в полиом объеме. 45 На фиг. 4 75 - сумматор по модулю два, входы которого связаны с выходами ячеек . 2„. Так, например, для кода 10/5 t 3, k 2, а входы сумматора по модулю два 15 связаны с выходами ячеек 2з, 2, 2$. При работе устройства переход от текущей комбинации, хранящейся в регистре сдвига 1 (см. фиг. 1), к очередной осуществляется при иомощи двух операций: сдвиг полный и сдвиг частичный. При выиолнении полного сдвига 55 происходит сдвиг на один разряд влево во всем регистре /. При выполнении частичного сдвига происходит сдвиг на одии разряд злево в разрядах 1-k регистра сдвига 1. Полный сдвиг осуществляется при всех переходах, 60 а частичный сдвиг выполняется только тогда, когда после полного сдвига сигнал на выходе блока управления сдвигом 3 равен «1. 5 50 имеющая нужный вес р, а на входную шину устройства подается сигнал «О. Через время, равное одному такту сдвига, этот сигнал проходит на выход линии задержки 12, закрывает вептиль 5 входного блока и открывает (через схему «ИЕ 11) вентиль 6 входного блока и вентиль 9. Цепь частичного сдвига (выход ячейки 2„ , вентиль 5 входного блока, схема «ИЛР1 7 входного блока, вход ячейки 2i) paзомкнута, и цепь полного сдвига (выход ячейки 2„, вентиль 6 входного блока, схема «ИЛИ 7 входного блока вход ячейки 2, выход ячейки 2, вентиль 9, вход ячейки 2к+1 замкнута, Устройство тем самым к работе подготовлено, На входную шину устройства с интервалом не менее двух тактов сдвига начинают поступать входные импульсы. Входной сигнал «1 поступает на тактовые входы ячеек - (через схему «ИЛИ 5) и на тактовые входы ячеек 2i - 2„. Ироисходит полный сдвиг. При этом межедииичные расстояния в комбинации не изменяются. Так, например, после осуществления полпого сдвига в комбинации Л 0101001 получаем комбинацию Ai 1010010. В обеих комбинациях расстояние между единицами равно соответственно 1, 2 и 1. Иосле окончания полного сдвига блок управления сдвигом 5 на основании значений выходных сигналов ячеек 2к+1 - 2„ вырабатывает управляюш,ий сигнал, равный «1, если частичный сдвиг нужно произвести. Выработка управляющего сигнала на выходе блока управления 3 происходит следующим образом (см. фиг. 3). Если хотя бы в одной из ячеек - 2 записана «Ь, то на выходе схемы «ИЛИ 13 блока управлепия сдвигом сигнал также равеп «1. В этом случае сигналы на выходах дешифратора 14 блока управления сдвигом ие имеют значения для управления сдвигом, Если же во всех ячейках 2к+1 - 2f записаны «О, то на выходе схемы «ИЛИ 13 блока управления сдвигом сигнал будет равен «1 только в том случае, когда есть «1 хотя бы па одном выходе дешифратора 14 блока управлепия сдвигом. Так как случаи, когда в ячейках 2к 1-2f есть хоть одна «1, встречаются чаще, чем случаи, когда в этих ячейках записаны все «О, то фактически получается, что выходы ячеек 2к+1 - 2/, подсоединенные к входам схемы «ИЛИ 13, образуют осиовную логическую фупкцию управления, а дешифратор 14 осуществляет коррекцию этой функции, В нринцнпе основная логическая функцияможет иметь более сложный характер, чем «Р1ЛИ, и зависеть от сигналов в ячейках 2 -1-1-2„. В этом случае входными сигналами дешифратора 14 также могут быть сигналы ячеек - 2„. К моменту выработки управляющего сигна12, открывает вентиль 5 входного блока и закрывает (через схему «НЕ //) вентиль 6 входного блока и вентиль 9. Цепь частичного сдвига замыкается, день полного сдвига размыкается.

Если сигнал на выходе блока управления сдвигом 3 равен «1, то вентиль 10 открывается, и импульс с выхода линии задержки 12 проходит через вентиль 10 и схему «ИЛИ 8 на тактовые входы ячеек 2 - 2. Происходит частичный сдвиг. При этом, как правило, изменяются межединичные расстояния в комбинации. Так, например, если в комбинация AI 1010010 произвести частичный сдвиг (k 2), то получим комбинацию Л/+1 1010001, в которой расстояния между единицами равны 1, 3 и 0.

После осуществления частичного сдвига образование очередной комбинации кода л/р закончено.

К этому времени сигнал на выходе линии задержки 12 снова равен нулю, так как интервал между соседними входными импульсами не меньше, чем два такта сдвига. Вновь цепь частичного сдвига разомкнута, а цепь полного сдвига замкнута. Устройство готово к приходу следующего входного сигнала и т. д.

Осуществляя, аналогично описанному, переходы от текущей комбинации к очередной комбинации, мы через С циклов работы устройства вновь получим начальную комбинацию. При этом будут прогенерированы все комбинации когда п/р.

В качестве примера рассмотрим код 6/2 (см.таблицу).

Для этого кода / 4 и, следовательно, номер k-ii ячейки может быть равен 2 или 3. Выбрано k 2. Тогда к входам схемы «ИЛИ 13 подсоединены выходы .ячеек 2я и 24. Дешифратор 14 для генерации этого кода не нужен (т. е. схема имеет вид, изобрал еннь й па фиг. 2).

Предмет изобретения

. Устройство для генерации кода с постоянным числом р единиц, содержащее /г-разрядный регистр сдвига, блок управления сдвигом, выполненный на схеме «ИЛИ и дешифраторе, входной блок, логические схемы «ИЛИ, «НЕ, вентили и линию задержки, вход которой соединен с входной щиной непосредственно и через логические схемы с тактовыми входами ячеек регистра сдвига, отличающееся тем, что, с целью упрощения устройства, входы блока управления сдвигом соединены с выходами соответствующих ячеек от (fe -f- 1)-й до га-й регистра сдвига, выход блока управления сдвигом соединен с первым входом вентиля, второй вход вентиля соединен с выходом линии задержки, выход вентиля через схему «ИЛИ соединен с тактовыми входами ячеек от первой до k-fi регистра сдвига, выход -й ячейки регистра сдвига соединен с первы входом вентиля входного блока, второй вход вентиля входного блока соединен с выходом линии задержки, выход вентиля входного блока через схему «ИЛИ входного блока соединен с входом регистра сдвига, входы схемы «ИЛИ блока управления сдвигом соединены с выходами соответствующих ячеек 5 от (/г + 1)-й до й регистра сдвига и выходами дешифратора, входы дешифратора соединены с выходами ячеек от (t -(- 1)-й до я-й регистра сдвига.

2. Устройство по п. 1, отличающееся тем,

что, с целью расширения функциональн1лх возможностей устройства, в нем блок управ, 1ения сдвигом содержит сумматор по модулю два, входы которого соединены с выходами ячеек от (/г + 1)-й до л-й регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР ДВОИЧНОГО КОДА ПОСТОЯННОГО ВЕСА | 1969 |

|

SU238228A1 |

| УСТРОЙСТВО для ГЕНЕРАЦИИ ТРОИЧНОГО КОДА С ПОСТОЯННЫМ КОЛИЧЕСТВОМ «НУЛЕЙ» | 1969 |

|

SU251931A1 |

| УСТРОЙСТВО ДЛЯ ГЕНЕРАЦИИ КОДА ПОСТОЯННОГО ВЕСА | 1969 |

|

SU238886A1 |

| Устройство для логарифмирования | 1982 |

|

SU1030800A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| УСТРОЙСТВО для ГЕНЕРАЦИИ п-РАЗРЯДНОГО ТРОИЧНОГО КОДА ПОСТОЯННОГО ВЕСА | 1968 |

|

SU231219A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

Г z:r

©-.

2,.гЬЧгл-./Н 9К-2лc;rz:

/4

51

..г./

-Vv; Л

uZ.

Даты

1969-01-01—Публикация