00 О

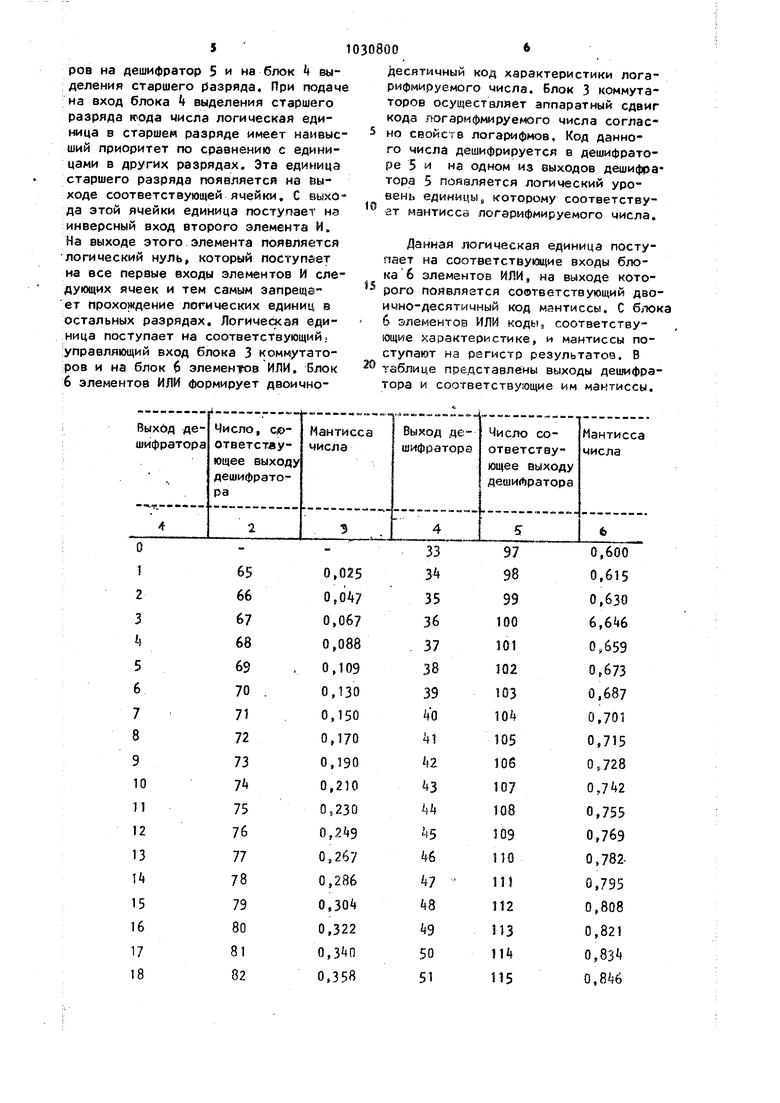

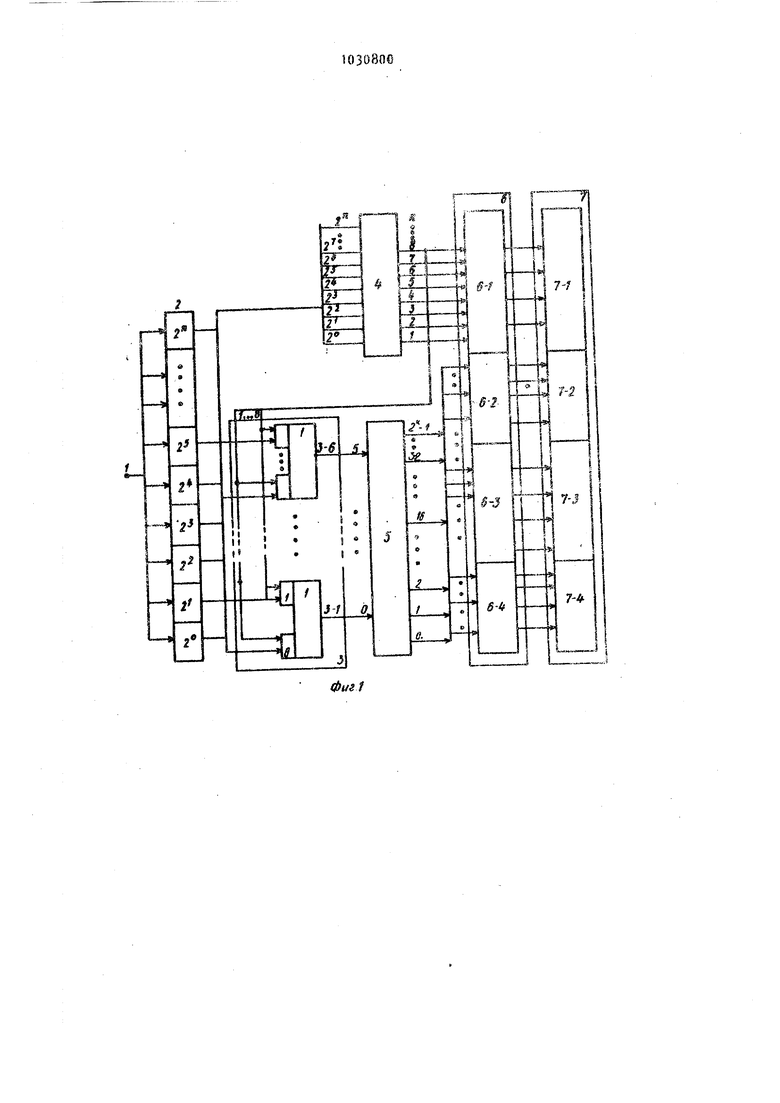

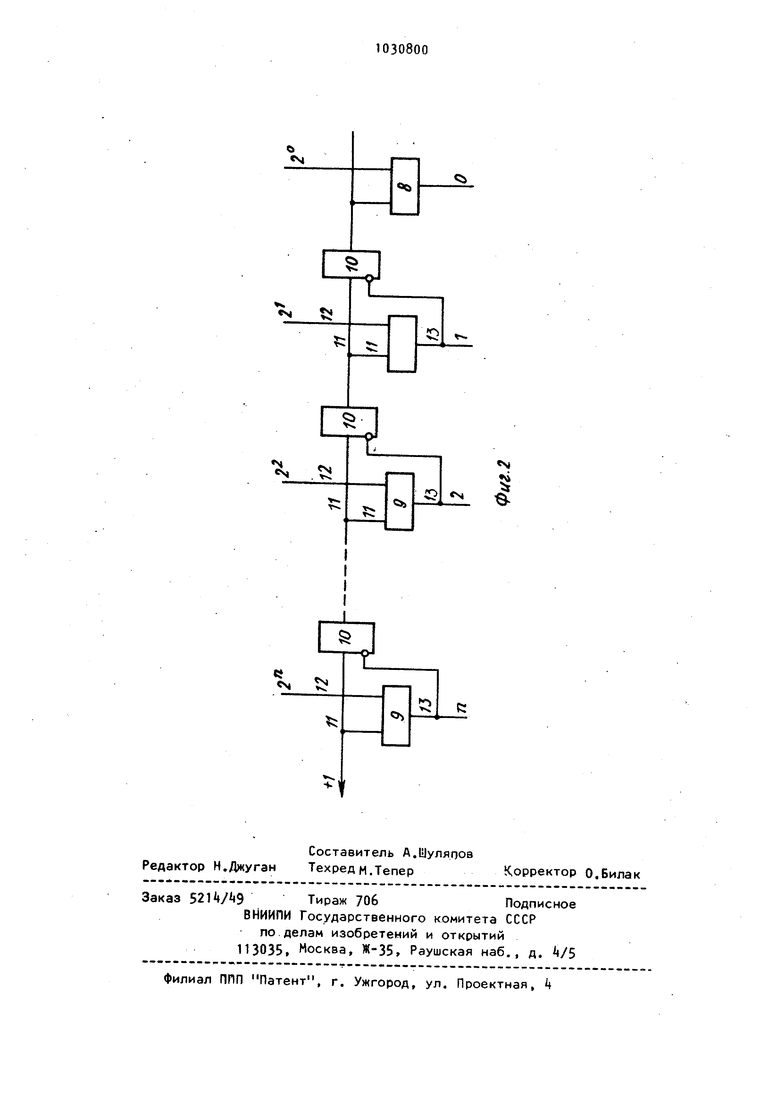

с Изобретение относится к вычисли тельной технике и может быть исполь зовано в цифровых вычислительных И измерительных устройствах, а также в устройствах электронного синтеза телевизионных изображений. Известен цифровой логарифматор, содержащий запоминающий регистр, сдвигающий регистр, блок вычисления характеристики, регистры харак теристики и мантиссы, дешифратор и блок априорной информации . Недостатком устройства является недостаточное быстродействие. Наиболее близким к изобретению является устройство для логарифмирования, содержащее регистр резуль тата, входной регистр, регистр сдри га, блок выделения старшего разряд Дешифратор, блок элементой ИЛИ, Время вычисления логарифма числ TQ в этом устройстве определяется равенством Tg--(C-vn), И) где (К-т) - количество сдвигов двоичных разрядов логарифмируемого числа; К - число входов в дешифраторе;m - характеристика логарифма;Т - период тактовых импульсов;„ - время задержки включени выходного сигнала относительно входного в регистре сдвига, дешифраторе, блоке элементов ИЛИ, регистре результат и блоке выделения стар шего разряда 21. Как видно из выражения (Т) время вычисления логарифма Т зависит от ха|рактеристики логарифма и непостоянно-для различных чисел. Данный не достаток не позволяет использоват устройство в различных системах моделирования, работающих в реальном масштабе времени, например при формировании сигнала телевизионного изображения с помощью цифровых вычислительных машин. Цель изобретения - повышение быстродействия устройства и достижение постоянной скорости вычисления логарифма. Указанная цель достигается тем, ЧТО в устройство для логарифмирова800Iния, содержащее входной регистр, входы которого соединены с входами устройства, а выходы соединены с входами блока выделения старшего разряда, выходы которого через элементы ИЛИ первой группы соединены с входами первой группы регистра результатов, дешифратор, выходы которого через элементы ИЛИ второй, третьей, четвертой групп соединены соответственно с входами второй, третьей, четвертой групп регистра результатов, введен блок коммутаторов, информационные входы которого соединены с выходами входного регистра, управляющие входы подключены к выходам блока выделения старшего разряда, а выходы блока коммутаторов соединены с входами дешифратора, На фиг, 1 представлена структурная схема устройства для логарифмирования; на фиг, 2 - принципиальная схема блока выделения старшего разряда. Устройство содержит информационный вход 1 устройства, входной регистр 2, блок 3 коммутаторов, блок выделения старшего разряда, дешифратор 5, блок 6 элементов ИЛИ, первая, вторая, третья и четвертая группы элементов ИЛИ 6-1, 6-2, 6-3 и 6- соответственно,,-.регистр 7 результата, первая, вторая, третья и четвертая группы регистра результата 7-1, 7-2, 7-3 и 7- соответственно, элементы И 8-10, В основе работы устройства для логарифмирования лежит следующее свойство логарифмов. Так как мантиссы чисел, кратных друг другу по основанию логарифма, в степени п (где ,2,3...) одинаковы, зная мантиссы, чисел, например, от б5 до 127, можно определить мантиссы других чисел, не попавших в эту группу, путем деления или умножения на 2 , Такое деление или умножение осуществляется простыч сдвигом двоичных разрядов двоичного кода вправо или влево соответственно, С учетом этого свойства входящие в устройство вычислительные блоки выполнены следующим образом. Блок 3 коммутаторов состоит из шести групп элементов 2И-8 ИЛИ, Первые входы первых элементов И всех ести групп соединены и образуют ервую шину управления. Первые вхоы вторых элементов и всех шести групп также объединены и образуют вторую шину управления и т.д. Всего соответствующие входы (по номеру до 8) образуют восемь шин управления. Вторые входы элементов И всех шести групп образуют сорок восемь информационных шин. Вторые входы первых элементов И всех шести групп соединены соответственно с шестью младшими разрядами входного регистра 2. Первая шина управления соединена с шестым выходом бл ка 4 выделения старшего разряда. Вторые входы вторых элементов И все шести групп соединены с шестью млад шими разрядами входного регистра та ким образом, чтобы обеспечить аппаратный сдвиг кода числа на один раз ряд влево. Вторая шина управления соединена с пятым входом блока выделения старшего разряда и т.д, до шестых элементов И всех шести групп. Вторы входы седьмых элементов И всех шести групп соединены с шестью младшим разрядами таким образом, чтобы обес печивать сдвиг кода чисел на один разряд вправо, а седьмая шина управ ления соединена с седьмым выходом блока выделения старшего разряда. Вторые входы восьмых элементов И всех шести групп соединены .с входным регистром таким образом, чтобы обеспечивать аппаратный сдвиг кода числа на два разряда вправо, а вось мая шина управления соединена с вос мым выходом блока выделения старшего разряда. Выходы блока 3 коммутат ров соединены с входами дешифратора 5. Блок 4 выделения старшего разряда состоит из последовательно соеди ненных ячеек, каждая из которых соо ветствует определенному разряду. Количество ячеек определяется числом разрядов логарифмируемого числа. Ячейка нулевого разряда состоит из одного логического элемента И 8, первый вход которого соединен с выходом следующей ячейки, второй вход соединен с нулевым выходом входного регистра, выход не соединяется ни с чем, так как log . Каждая ячеек последующих разрядов состоит из двух логических элементов И и 10. В данных ячейках первые входы 11 двух логических элементов И 9 и 10, соединены с выходом второго логического элемента И 10 следующей ячейки, второй вход 12 первого логического элемента И 9 соединен с соответствующим выходом входного регистра. Выход 13 первого логического элемента И 9 соединен с вторым инверсным входом второго логического элемента И 10 и соответствующим управляющим входом блока 3 коммутаторов. Первый вход п-ой ячейки соединен с источником логической единицы. В блоке k вход старшего разряда имеет высший приоритет по сравнению с младшим. Например разряд 2 имеет приоритет выше разрядов . ,... 2 ,.... 2 , разряд 2 имеет приоритет выше разрядов 2, 2 , 2 и т.д. Это значит, что число, записанное в двоичном коде 1, в старшем разряде будет иметь высший приоритет по сравнению с другими разрядами и пройдет на соответствующий выход блока k выделения старшего разряда, исключив тем самым прохождение 1 на выход блока от разрядов, имеющих меньший приоритет. Каждый выход блока k соединяется в группе элементов ИЛИ 6 с теми элементами ИЛИ, которые обеспечивают набор в двоично-десятичном коде числа, соответствующего характеристике логарифмируемого числа. Дешифратор 5 представляет комбинационную схе.му, которая дешифрирует шестиразрядный код в один из шестидесяти четырех выходов и имеет шесть двоичных входов, т.е. . Таким образом, дешифратор расшифровывает 2 комбинации кодов чисел от О до 63, появляющихся на выходах блока 3 коммутаторов. Первому выходу дешифратора 5 соответствует мантисса числа 65, второму выходу-мантисса числа 66, третьему - манти-сса числа б7 и т.д., шестидесяти третьему - мантисса числа 127 2-2-1, т.е. каждому выходу дешифратора соответствует своя мантисса (см. таблицу) . Каждый выход дешифратора 5 соединяется в блоке 6 элементов ИЛИ с теми элементами ИЛИ, которые в своей группе обеспечивают набор в двоично-десятичном коде мантиссы, соответствующей выходу дешифратора. Устройство работает следующим образом. С информационного входа 1 на входной регистр . поступает код числа. С выхода входного регистра 2 код числа поступает через блок 3 коммутатоsров на дешифратор 5 и на блок k выделения старшего разряда. При подаче на вход блока k выделения старшего разряда юода мисяа логическая единица в старшем разряде имеет наивысший приоритет по сравнению с единицами в других разрядах. Эта единица старшего разряда появляется на выходе соответствующей ячейки. С выхода этой ячейки единица поступает на инверсный вход второго элемента и. На выходе этого элемента появляется логический нуль, который поступает на все первые входы элементов И следующих ячеек и тем самым запрещает прохождение логических единиц в остальных разрядах. Логическая единица поступает на соответствующий. Управляющий вход блока 3 коммутаторов и на блок 6 элементов ИЛИ, Блок 6 элементов ИЛИ формирует двоично00Йеснтичный код характеристики логарифмируемого числа. Блок 3 коммутаторов осуществляет аппаратный сдвиг кода логарифмируемого числа согласно свойств логарифмов. Код данного числа дешифрируется в дешифраторе 5 и на одном из выходов дешифратора 5 появляется логический уровень единицыS которому соответствует мантисса логарифмируемого числа. Данная логическая единица поступает на соответствущие входы блока б элементов ИЛИ, на выходе которого появляется соответствующий двоично-десятичный код мантиссы, С блока 6 элементов ИЛИ коды, соответствующие характеристике, и мантиссы поступают на регистр результатоэ. В таблице представлены выходы дешифратора и соответствующие им мантиссы.

8

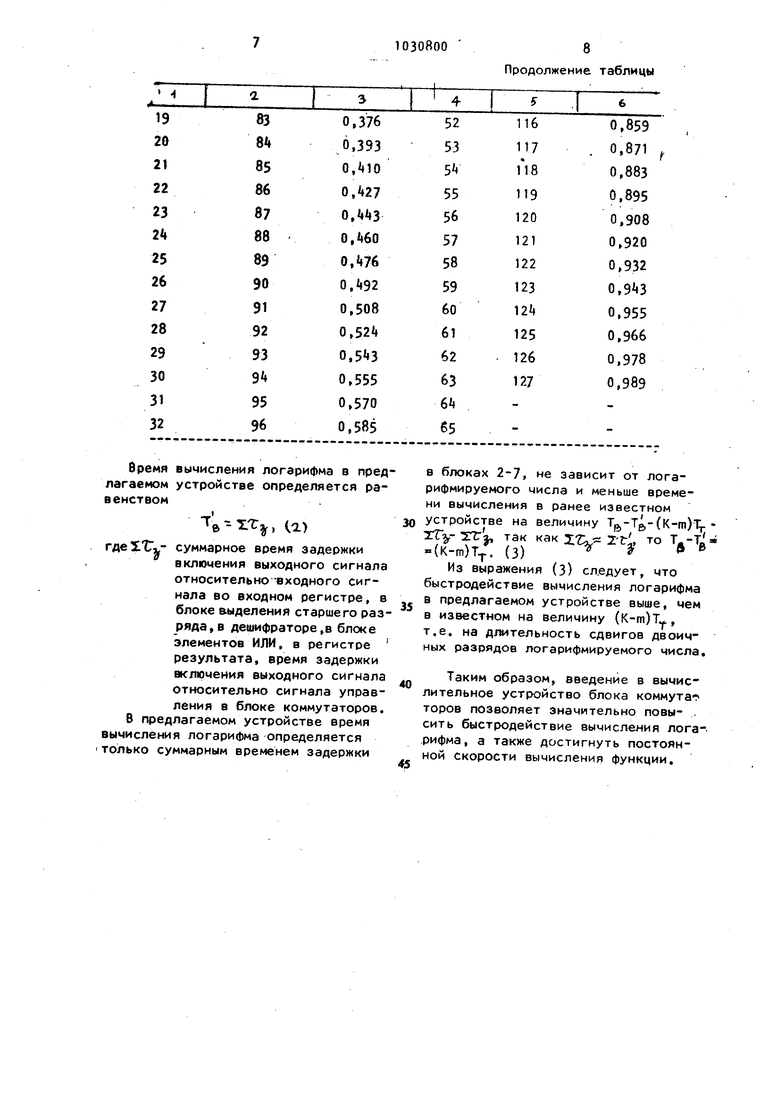

1030800 Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифма | 1978 |

|

SU744560A1 |

| Устройство для вычисления логарифмачиСлА | 1979 |

|

SU849210A1 |

| Устройство для вычисления логарифмов чисел | 1981 |

|

SU972504A1 |

| Устройство для вычисления логарифмов | 1984 |

|

SU1203518A1 |

| Логарифмирующее устройство | 1976 |

|

SU634272A1 |

| Цифровое логарифмирующее устройство | 1976 |

|

SU624233A1 |

| Устройство для логарифмирования | 1980 |

|

SU959072A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для логарифмирования | 1977 |

|

SU708343A1 |

| Цифровое устройство для вычисления логарифма числа | 1979 |

|

SU1003082A1 |

УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ, содержащее входной реГпстр, входы которого соединены с входами устройства, а выходы соединены с вхЬдами блока выделения старшего разряда, выходы которого через элементы-ИЛИ первой группы соединены с входами первой группы регистра результатов, дешифратор, выходы которого через элементы ИЛИ, второй, третьей, четвертой групп соединены соответственно с входами второй, третьей, четвертой групп регистра результатов, отличающееся тем, что, с целью повышения быстродействия и достижения постоянной скорости вычисления логарифма, введен блок коммутаторов, информационные входы которого соединены с выходами входного регистра, управляющие входы подключены к выходам блока выделения старшего разряда а выходы блока коммутаторов соединены с входами дешифратора.

Время вычисления логарифма в предлагаемом устройстве определяется равенством

.-г, U)

гдеХТ,- суммарное время задержки

включения выходного сигнала относительно ВХОДНОГО сигнала во входном регистре, в блоке выделения старшего разряда, в дешифраторе,в блоке элементов ИЛИ, в регистре результата, время задержки включения выходного сигнала относительно сигнала управления в блоке коммутаторов. В предлагаемом устройстве время

вычисления логарифма определяется только суммарным временем задержки

в блоках 2-7, не зависит от логарифмируемого числа и меньше времени вычисления в ранее известном устройстве на величину Tg,(K-m)T ТГу ТГ J, так как Jt,.- Г, то -(К-П1)Тт. (3)

Из выражения (3) сл.едует, что быстродействие вычисления логарифма в предлагаемом устройстве выше, чем в известном на величину (К-т)Т., т.е. на длительность сдвигов двоичных разрядов логарифмируемого числа.

Таким образом, введение в вычислительное устройство блока коммутаг торов позволяет значительно повысить быстродействие вычисления лога-рифма, а также достигнуть постоянной скорости вычисления функции.

5

s

N

«-. t

«N

2 N

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления очередностью обслуживания | 1976 |

|

SU603993A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР ff , кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-07-23—Публикация

1982-01-11—Подача