Изобретение предназначено для использования в вычисЛИтельной технике.

Известны элементы вычислительной среды с переменной структурой настройки. Таким элементам свойственны большие затраты оборудования, необходимого для построения схемы управления настройкой элемента, и большое, по сравнению с координатной системой настройки, время настройки одного элеме:5та вычислительной среды. Это происходит вследствие того, что как информация, служащая для образования путей настройки, так и настроечная информация передаются на элемент вычислительной среды последовательным способом через соседние элементы.

Целью изобретения является упрош,ение конструкции элемента и повышение быстродействия системы его настройки.

Сущность изобретения заключается в том, что в вычислительной среде, построенной на базе предлагаемого элемента, каждый элемент получает от соседних элементов только сигнал, разрешаюш.ий прием информации в память настройки и в схему выбора направления, а информация настройки и информация о направлении передачи сигнала на соседние элементы подводится непосредственно к входным полюсам каждого элемента, причем после записи настроечной информации в рамять настройки осуществляется выбор направления передачи сигнала на соседний элемент.

Это позволяет упростить элемент вследствие того, что при таком способе настройки

не нужно хранить в настроечном поле информациЕО о всей выбранной цепочке настраиваемых элементов. Кроме того, уменьшается время, необходимое для настройки одного элемента вычислительной среды, так как в предлагаемом элементе информация подается на входы параллельным способом.

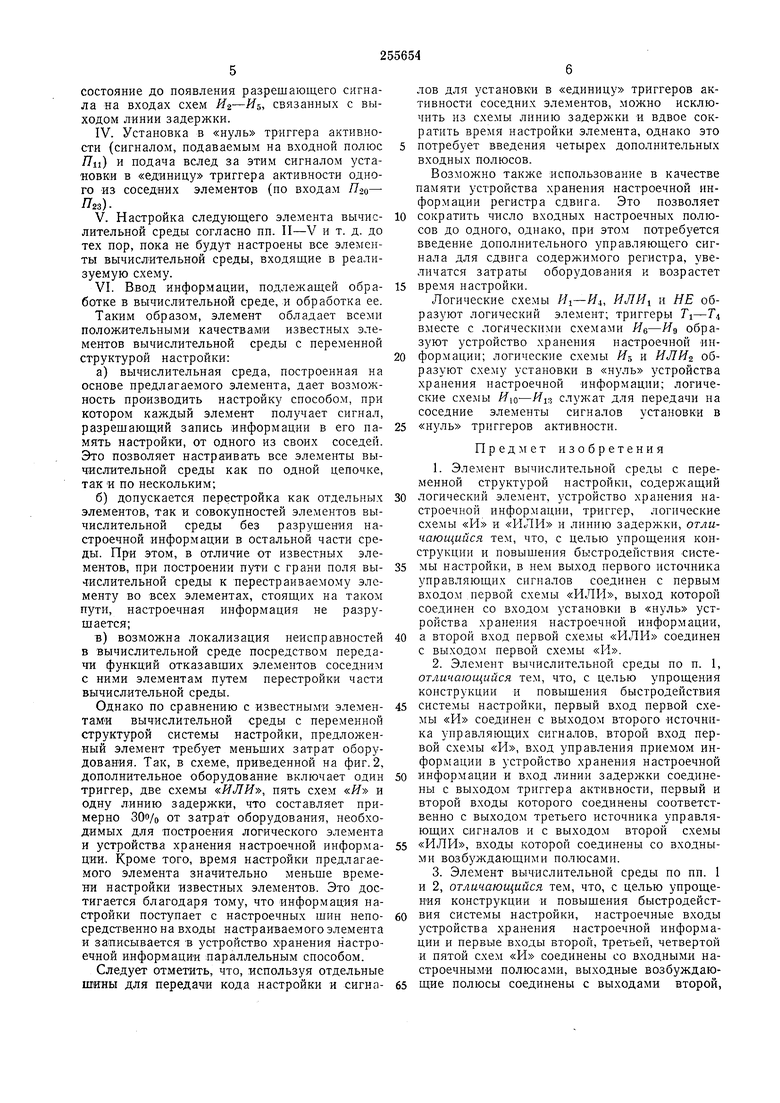

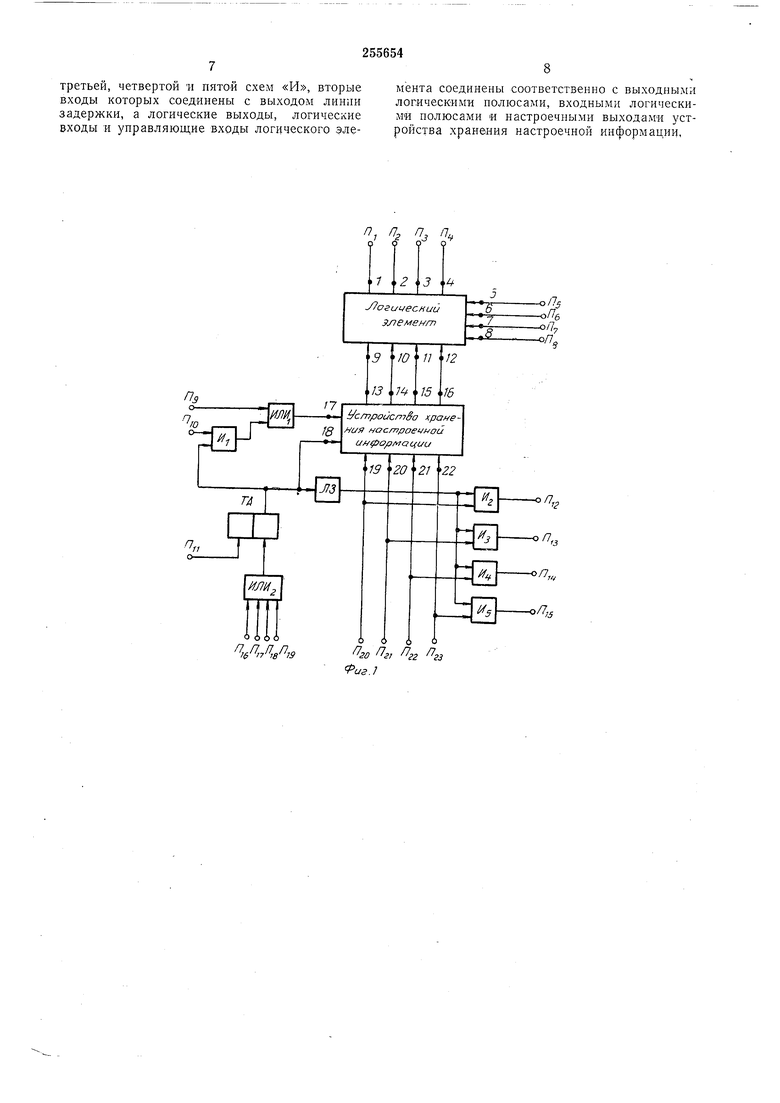

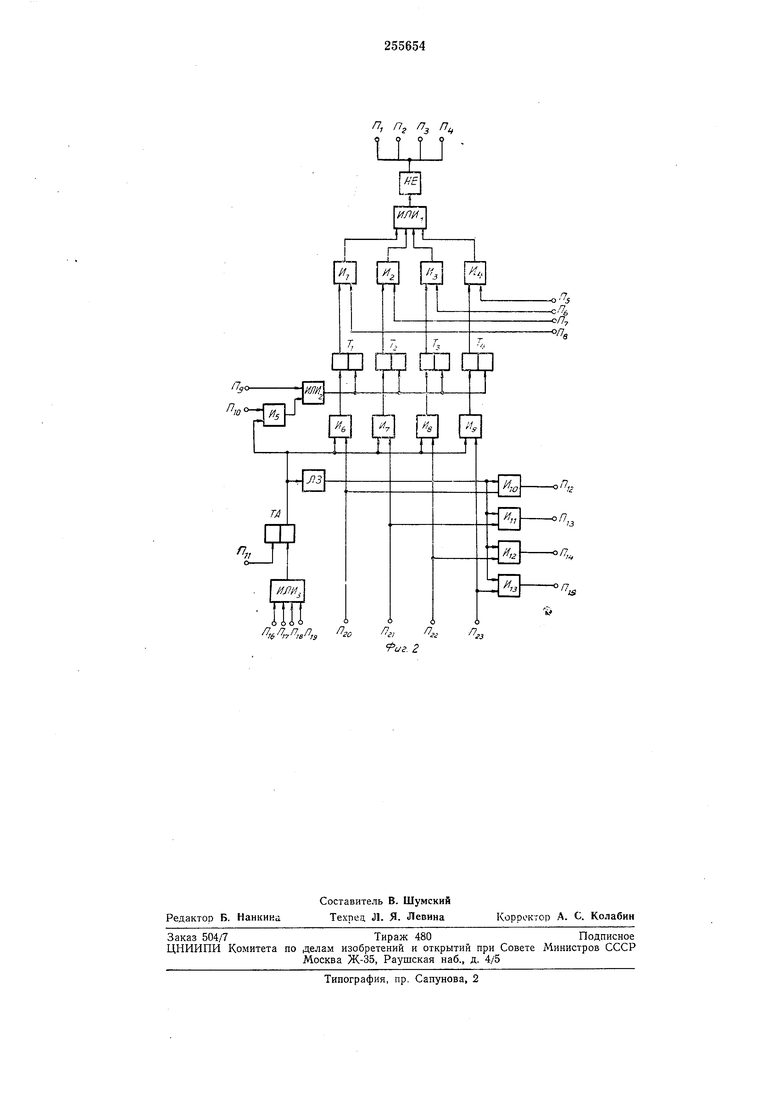

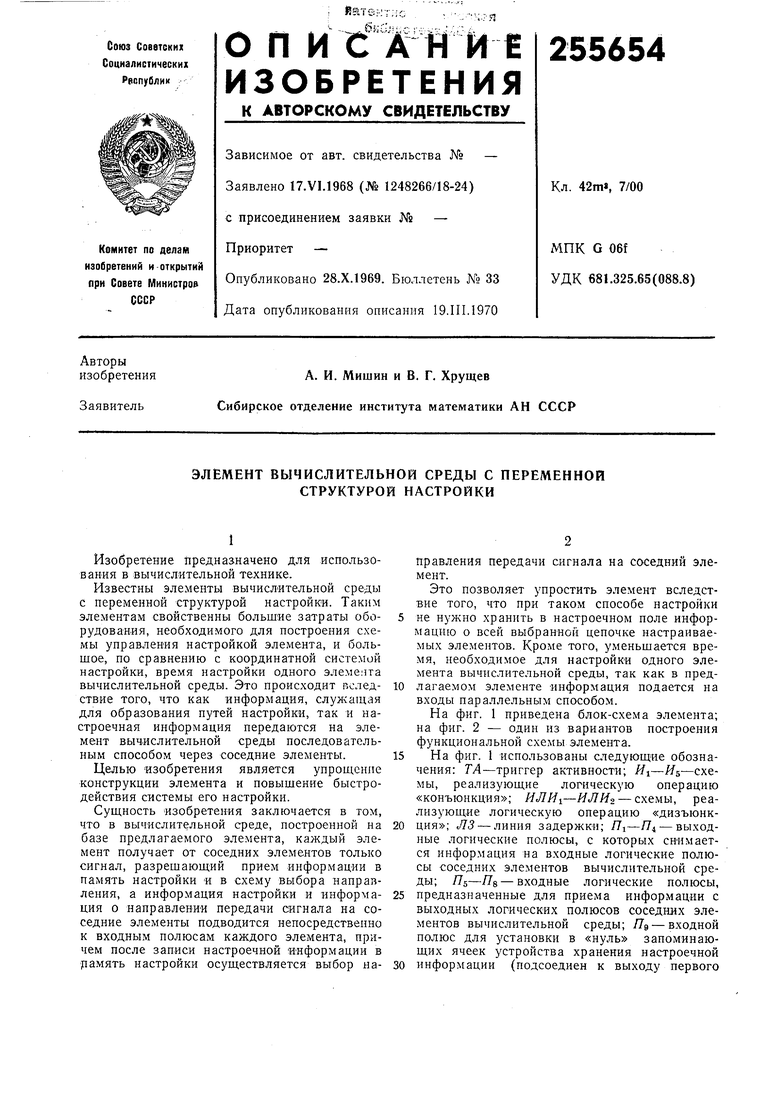

На фиг. 1 приведена блок-схема элемента; на фиг. 2 - один из вариантов построения функциональной схемы элемента.

На фиг. 1 использованы следующие обозначения: ТА-триггер активности; И -И -схемы, реализующие логическую операцию «конъюнкция ; - схемы, реализующие логическую операцию «дизъюнкция ; ЛЗ--линия задержки; - выходные логические полюсы, с которых снимается информация на входные логические полюсы соседних элементов вычислительной среды; - входные логические полюсы,

предназначенные для приема информации с выходных логических полюсов соседних элементов вычислительной среды; Яд - входной полюс для установки в «нуль запоминающих ячеек устройства хранения настроечной источника управляющих сигналов), независимо от состояния триггера активности; Яю - входной полюс, предназначенный для установки в «нуль запоминающих ячеек устройства хранения настроечной информации при условии, что триггер активности находится в состоянии «единица (подсоединен к выходу второго источника управляющих сигналов); Яц - входной полюс для установки в «нуль триггера активности (подсоединен к выходу третьего источника управляющих сигналов); Яха-Я15 - выходные возбуждающие полюсы, предназначенные для передачи на входные возбуждающие полосы соседних элементов сигналов, устаиавливающих в «единицу их триггеры активности; - входные возбуждающие полюсы для приема с выходных возбуждающих полюсов соседних элементов сигналов, устанавливающих в «единицу тр:иггер активности; IJso-Яаз-входные настроечные полюсы, предназначенные для приема кода настройки и сигналов о выборе направления передачи сигнала, устанавливающего в «единицу триггеры активности соседних элементов; 1-4 логические выходы логического элемента, сигналы с которых поступают на выходные логические полюсы; 5-8 - логические входы логического элемента, предназначенные для приема сигналов со входных логических полюсов; 9-}2 - управляющие входы логического элемента, предназначенные для приема сигналов с настроечных выходов устройства хранения настроечной информации; 13-16 - настроечные выходы устройства хранения настроечной информации, сигналы с которых поступают на управляющие входы логического элемента; 17 - вход установки в «нуль запоминающих ячеек устройства хранения настроечной информации; 18- вход управления приемом информации в устройство хранения настроечной информации; если на этот вход поступает сигнал «единица, то разрещается запись настроечной информации в запоминающие ячейки устройства хранения настроечной информации; 19- 22 -настроечные входы устройства хранения настроечной информации, предназначенные для приема кода настройки, поступающего на входные настроечные полюсы. Обозначения полюсов на фиг. 2 соответствуют обозначе- 5 ниям на фиг. 1. Триггер активности выполняет следующие функции: а)запрещает изменение состояния запом-и- 5 нающих ячеек устройства хранения настроечной информации по входному полюсу Яю и выдачу сигналов на входные возбуждающие полюсы, если он находится в состоянии «нуль ; б)разрещает установить в «нуль запоминающие ячейки устройства хранения настроечной информации сигналом, поступающим на полюс Яю, и записать в них новую информа6нолюсы Яго--Я2з, если он находится в состоянии «единица ; в) непосредственно после перехода из состояния «единица в состояние «нуль разрешает передать сигналы на выходные возбуждающие полюсы элемента для установки в «единицу триггеров активности соседних элементов. Для этого подаются сигналы на входные полюсы Ян и Я2о-Поз, что обеспечивает благодаря наличию линии задержки переход триггера активности в «нуль при одновременном переходе триггера активности соседнего элемента в «единицу, Устройство хранения настроечной информации предназначено для хранения кода настройки. Оно состоит из запоминающих ячеек я логических цепей, управляющих записью информации настройки (фиг. 2). Логический элемент предназначен для обработки логической информации, поступающей на его входы. Логическая схема ИЛИ предназначена для объединения сигналов установки в «нуль, поступающих с входного полюса Яд и с выхода схемы И. Логическая схема И предназначена для подачи сигнала, поступающего на входной полюс Яю, иа вход схемы ИЛИ при условии, что триггер активности находится в состоянии «единица. Логическая схема ИЛИ предназначена для объединения сигналов, поступающих на входные возбуждающие полюсы, Эти сигналы предназначены для установки триггера активности в «единицу, Логические схемы И-2-И при наличии сигнала, поступающего через линию задержки с выхода триггера активности, вырабатывают сигнал для установки в «единицу триггера активности соседнего элемента. Для этого на входные полюсы Яго-Я2з подается с.оответствующий код. Алгоритм работы вычислительной среды, построеннои па основе предлагаемого элемента, состоит из следующих основных этапов:I.Установка в «нуль триггеров активности и триггеров устройства хранения настроечной информации всех элементов вычислительной среды, для чего подаются сигналы на входные полюсы Яэ и Яц. II.Установка в «единицу триггера активности элемента, расположенного на грани поля вычислительной среды. Для этого подается сигнал ла один из его входных возбуждающих полюсов Я18-Я1д. III.Подача на входные настроечные полюы Я20-Ягз кода настройки элемента вычисительной среды. Так как на вход 18 устройтва хранения настроечной информации в тот момент времени -подан разрешающий игнал с выхода триггера активности, код астройки поступает на входы запоминающих чеек устройства хранения настроечной инормации и запоминается в них. Величина адержки линии задержки выбирается такой.

состояние до появления разрешающего сигнала на входах схем HZ-И, связанных с выходом линии задержки.

IV.Установка в «нуль триггера активности (сигналом, подаваемым на входной полюс Яп) и подача вслед за этим сигналом установки в «единицу триггера активности одного из соседних элементов (по входам Яао-

Ягз).

V.Настройка следующего элемента вычислительной среды согласно пп. II-V и т. д. до тех пор, пока не будут настроены все элементы вычислительной среды, входящие в реализуемую схему.

VI.Ввод информации, подлежащей обработке в вычислительной среде, и обработка ее.

Таким образом, элемент обладает всеми положительными качествами известных элементов вычислительной среды с переменной структурой настройки:

а)вычислительная среда, построенная на основе предлагаемого элемента, дает возможность производить настройку способом, при котором каждый элемент получает сигнал, разрешающий запись информации в его память настройки, от одного из своих соседей. Это позволяет настраивать все элементы вычислительной среды как по одной цепочке, так и по нескольким;

б)допускается перестройка как отдельных элементов, так и совокупностей элементов вычислительной среды без разрушения настроечной информации в остальной части среды. При этом, в отличие от известных элементов, при построении пути с грани поля вычислительной среды к перестраиваемому элементу во всех элементах, стояш,их на таком пути, настроечная информация не разрушается;

в)возможна локализация неисправностей в вычислительной среде посредством передачи функций отказавших элементов coceдни с ними элементам путем перестройки части вычислительной среды.

Однако по сравнению с известными элементами вычислительной среды с переменной структурой системы настройки, предложенный элемент требует меньших затрат оборудования. Так, в схеме, приведенной на фиг. 2, дополнительное оборудование включает один триггер, две схемы «ИЛИ, пять схем «Я и одну линию задержки, что составляет примерно ЗОо/о от затрат оборудования, необходимых для построения логического элемента и устройства хранения настроечной информации. Кроме того, время настройки предлагаемого элемента значительно меньше времени настройки известных элементов. Это достигается благодаря тому, что информация настройки поступает с настроечных шин непосредсТВенно на входы настраиваемого элемента и записывается ъ устройство хранения настроечной информации параллельным способом.

лов для установки в «единицу триггеров активности соседних элементов, можно исключить из схемы линию задержки и вдвое сократить время настройки элемента, однако это потребует введения четырех дополнительных входных полюсов.

Возможно также использование в качестве памяти устройства хранения настроечной информации регистра сдвига. Это позволяет

сократить число входных настроечных полюсов до одного, однако, при этом потребуется введение дополнительного управляющего сигнала для сдвига содержимого регистра, увеличатся затраты оборудования и возрастет

время настройки.

Логические схемы HI-Н, НЛН и НЕ образуют логический элемент; триггеры Ti-T.i вместе с логическими схемами Яе-Яд образуют устройство хранения настроечной информации; логические схемы Я,, и НЛН образуют схему установки в «нуль устройства хранения настроечной информации; логические схемы Яю--Я13 служат для передачи на соседние элементы сигналов установки в

«нуль триггеров активности.

Предмет изобретения

1.Элемент вычислительной среды с переменной структурой настройки, содерл ащий

логический элемент, устройство хранения настроечной информации, триггер, логические схемы «И и «ИЛИ и линию задержки, отличающийся тем, что, с целью упрощения конструкции и повышения бьзстродействия системы настройки, в нем выход первого источника управляющих сигналов соединен с первым входом первой схемы «ИЛИ, выход которой соединен со входом установки в «нуль устройства хранения настроечной информации,

а второй вход первой схемы «ИЛИ соединен с выходом первой схемы «И.

2.Элемент вычислительной среды по п. 1, отличающийся тем, что, с целью упрощения конструкции и повыщения быстродействия

системы настройки, первый вход первой схемы «И соединен с выходом второго источника управляющих сигналов, второй в.ход первой схемы «И, вход управления приемом информации в устройство хранения настроечной

информации и вход линии задержки соединены с выходом триггера активности, первый и второй входы которого соединены соответственно с выходом третьего источника управляющих сигналов и с выходом второй с.хемы

«ИЛИ, входы которой соединены со входными возбуждающими полюсами.

3.Элемент вычислительной среды по пп. 1 и 2, отличающийся тем, что, с целью упрощения конструкции и повышения быстродейстВИЯ системы настройки, настроечные входы устройства хранения настроечной информации и первые входы второй, третьей, четвертой и пятой схем «И соединены со входными настроечными полюсами, выходные возбуждаютретьей, четвертой и пятой схем «И, вторые входы которых соединены с выходом линии задержки, а логические выходы, логические входы и управляющие входы логического элемента соединены соответственно с выходными логическими нолюсами, входными логическими полюсами и настроечными выходами устройства хранения настроечной информации,

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1970 |

|

SU267183A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1970 |

|

SU266361A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СРЕДА | 1970 |

|

SU259474A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1972 |

|

SU355611A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1971 |

|

SU314203A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1970 |

|

SU259475A1 |

| СО АН СССР | 1969 |

|

SU239661A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ПЕРЕМЕННОЙ СТРУКТУРОЙНАСТРОЙКИ | 1971 |

|

SU322775A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫВСЕСОЮЗНАЯnAT?HTHO-TLEHHE:H/.'БИБЛИОТЕКА | 1971 |

|

SU290275A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫо r-i о ( !i »э.hfsur? q;^r?rtjTOn.vUlil^ id>&;y;!i:r isjfS | 1972 |

|

SU419887A1 |

,.

П,о Пг, П,2 fua.l

/7, П, П П

I М 1 /7

4

«/7

СП СП Ш

Даты

1969-01-01—Публикация