Данное изобретение относится к области вычислительной техники и автоматики.

Известен элемент вычислительной среды с Ьеременной структурой настройки, содержащий логический элемент, регистр сдвига, триггер, линию задержки и логические схемы «И и «ИЛИ, который позволяет изменять конфигурацию путей передачи информации в вычислительной среде. Такой элемент сложен по конструкции, так как число триггеров активности (триггеров БЫбора направления) определяется ЧИСЛОМ соседних элементов. Вто.рым недостатком этого элемента является то, что при увеличении числа соседних элементов (связей в вычислительной среде) увеличивается не только число триггеров активности, но и происходит увеличение числа внеплних выводов. Это происходит потому, что вход и выход регистра сдвига в каждом элементе необходимо соединять соответственно с выходами и входами всех соседних элементов.

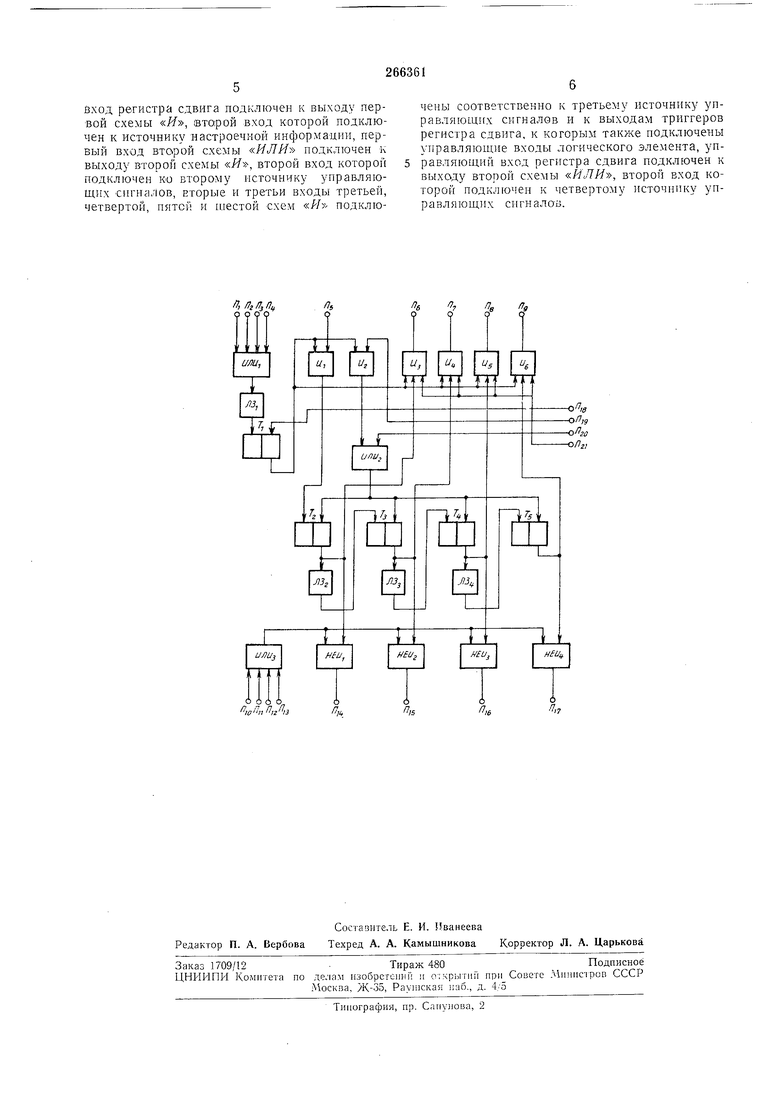

Цель изобретения - упрощение конструкции элемента. Сущность изобретения заключается в том, что предлагаемый элемент вычислительной среды получает от соседних элементов вычислительной среды только информацию о возбуждении триггера активности, а Информацию, которая записывается в его регистр сдвига, он получает с внешних полюсов вычислительной среды. Это упрощает конструкцию Элемента. Возбуждающие в нем входы подсоединены к входам первой схемы «ИЛИ, выход которой через линию задержки подключен к первому входу триггера активности, второй вход которого подключен к первому источнику управляющих сигналов, а выход соединен с первыми входами первой, второй, третьей, четвертой, пятой и шестой схем «И, вход регистра сдвига подключен к выходу нервой

схемы «Ях, второй вход которой подключен к источнику настроечной информации, первый вход второй схемы «ИЛИ подключен к выходу второй схемы «Я, второй вход которой подключен ко второму источнику управляющих сигналов, возбуждающими выходами элемента являются выходы третьей, четвертой, пятой и шестой схем «Я, вторые входы и третьи входы которых подключены соответственно к третьему источнику управляющих сигналов и к выходам триггеров регистра сдвига. К последним также подключены управляющие входы логического элемента, управляющий вход регистра сдвига подключен к выходу второй схемы «ИЛИ, второй вход которой подклк чен к четвертому источнику управляющих сигналов, логические входы и выходы логического элемента являются логическими входами и выходами элемента вычислительной среды. На чертеже представлена функциональная

менной структурой настройки, где Г|-Т - триггеры, - логические схемы, реализующие операцию «конъюнкция, - логические схемы, реализующие операцию «дизъюнкция, «НЕИ- -«HEM.i - логические схемы, реализующие функцию «штрих Шеффера, JI3i-Л3, - линии задержки. /7;-/74 - возбуждающие входы элемента - предназначены для установки в «единицу триггера активности 7|, вход Яб - для подачи информации настройки (кода настройки) на вход регистра сдвига. Сигналы с возбуждающих выходов Я«-Яд элемента поступают на соседние элементы среды для установки в «единицу их триггеров активности. На логические входы Яю-Я1з элемента поступают сигналы с логических выходов соседних элементов среды или извне, а с логических выходов Ям-Яп элемента снимается информация, обработанная логическим элементом среды. Вход Пк предназначен для установки в «нуль триггера активности , входы fho - для подачи сдвигающих управляющих импульсов, вход Я21 - для подачи сигнала, который разрещает содерл имое регистра сдвига передать на выходы Яе-Яд.

Триггер активности Г совместно с регистром сдвига и сигналом, подаваемым по входу Яо1, управляет цепями выдачи информации на возбуждающие выходы Яц-Яд. Этот же триггер совместно с логической схемой управляет приемом информации в регистр сдвига, а также через схемы , управляет подачей в регистр сдвига сдвигающих импульсов, поступающих по входу HIQ.

Триггеры TI-Т совместно с линиями задержки ЛЗ-2-ЛЗ образуют регистр сдвига, логические схемы ,}, ,, образуют логический элемент.

Регистр сдвига совместно с сигналом, подаваемым по входу Яз, а также с триггером активности Т) и линией задержки c./73i выполняет функцию выбора направления установки в «единицу триггеров активности соседних элементов.

Выбор направления осуществляется следуюЩим образом.

Если «единица находится в первом разряде регистра сдвига (триггер активности находится также в состоянии «единица), то при подаче разрещающего сигнала на вход Я21, она поступает через схему на выход Яз - осуществляется выборка первого направления. Если «единица находится во втором разряде регистра сдвига, то при подаче разрещающего сигнала на вход Я21 она поступает через схему на выход П - осуществляется выборка второго направления и т. д..

Таким образом, в зависимости от положения «единицы в регистре сдвига выбирается одно из возмол ных направлений для установки в «единицу триггеров активности последующего (соседнего) элемента.

мента. Этот код подается с выхода каждого разряда регистра сдвига на управляющие входы логического элемента. Линия задержки У/З выполняет функцию запоминания сигнала устаиовки в «единицу триггера активности выбранного соседнего элемента на время, которое определяется временем записи кода настройки в регистр сдвига и временем установки триггера активности в состояние «нуль.

Один из возможных алгоритмов работы предлагаемого элемента вычислительной среды, а следовательно, и вычислительной среды складывается из следующих основных этапов: а) установка в «нуль триггеров активности;

б) возбуждение триггера активности элемента вычислительной среды, расположенного на внещней стороне вычислительной среды;

в) установка в «нуль регистра сдвига путем подачи сигналов на вход Я19;

г) запись сигнала, соответствующего логической единице, в иервый разряд регистра сдвига возбужденного элемента (осуществляется путем подачи сигнала на вход

д)выбор требуемого направления для возбуждения триггера активности последующего

элемента среды (осуществляется путем подачи сигналов на вход //2t, а также путем сдвига единицы в регистре сдвига);

е)запись в регистр сдвига кода настройки логического элемента (запись это.го кода осуществляется по входу Яз).

Настройка последующего элемента вычислительной среды производится по пунктам а)-е) и т. д. до тех пор, пока не будут настроены

все требуемые элементы среды. Носле выполнения пункта а) триггеры активности всех элементов среды устанавливаются в состояние «нуль, запоминание сигнала установки в единицу (сигнала о выборе направления) триггера активности осуществляется с помощью линии задержки ./73.

Из приведенного алгоритма работы вычислительной среды, выполненной на базе иредлагаемого элемента, видно, что вычислительную

среду можно настраивать как по одной цепочке, так и по нескольким цепочкам, а также производить перестройку части вычислительной сред без нарущения настройки в другой ее части.

Предмет изобретения

Элемент вычислительной среды с переменной структурой настройки, содержащий логический элемент, регистр сдвига, триггер, линию задержки и логические схемы «Я и «ИЛИ, отличающийся, тем, что, с целью упрощения конструкции, в нем возбуждающие входь элемента подсоединены к входам первой схемы

«ИЛИ, выход которой через линию задержки под1 лючен к первому входу триггера активности, второй вход которого подключен к первому источнику управляющих сигналов, а выход соединен с первыми входами первой, второй,

вход регистра сдвига подключен к выходу первой схемы «//, второй вход которой подключен к источнику настроечной информацни, первый вход второй схемы «ИЛИ- подключен к выходу второй схемы «Я, второй вход которой подключен ко второму источнику управляющих сигналов, вторые и третьи входы третьей, четвертой, пятой и гпестой схем «Я подключепы соответственно к третьему источнику управляющих сигналов и к выходам триггеров регистра сдвига, к когорым также подключены управляющие входы логического элемента, управляющий вход регистра сдвига подключен к выходу второй схемы «ИЛИ, второй вход которой подключен к четвертому источнику управляющих сигналоВ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1969 |

|

SU255654A1 |

| СО АН СССР | 1969 |

|

SU239661A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1970 |

|

SU259475A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1971 |

|

SU314203A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1970 |

|

SU267183A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1972 |

|

SU355611A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1972 |

|

SU342180A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫо r-i о ( !i »э.hfsur? q;^r?rtjTOn.vUlil^ id>&;y;!i:r isjfS | 1972 |

|

SU419887A1 |

| Элемент однородной вычислительной структуры | 1978 |

|

SU733107A1 |

| Устройство для решения игровых задач на вычислительных сетях | 1982 |

|

SU1104522A1 |

Даты

1970-01-01—Публикация