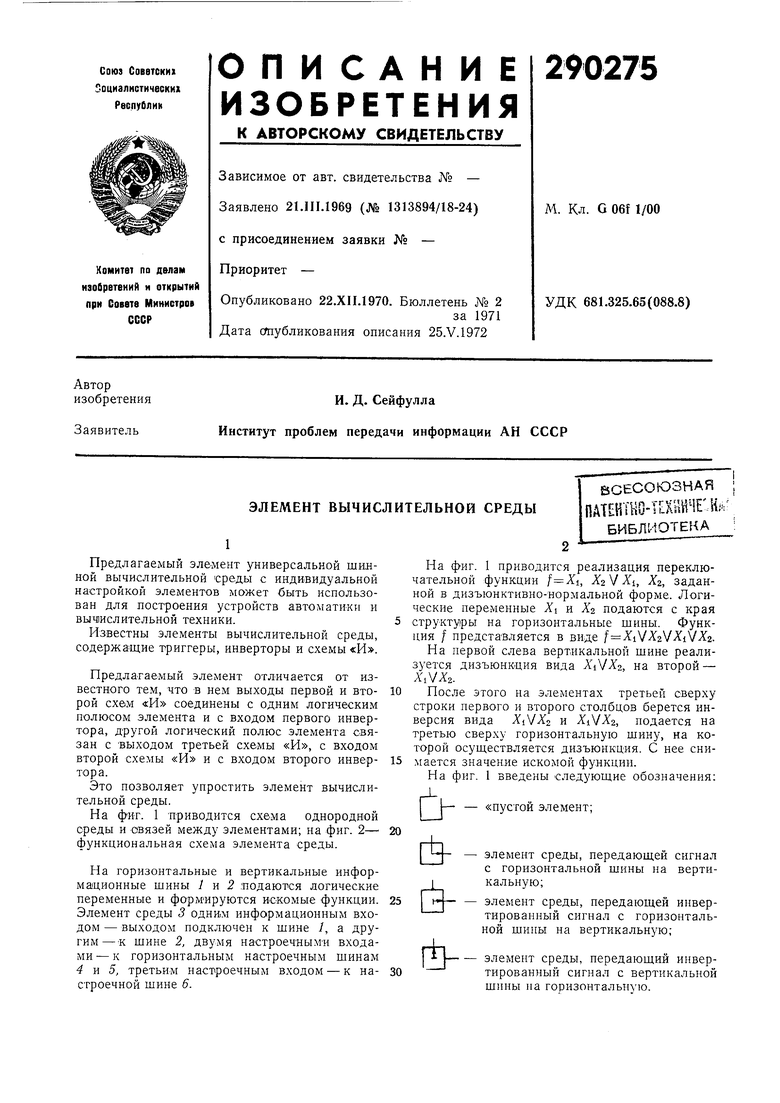

Предлагаемый элемент универсальной шилной вычислительной среды с индивидуальной настройкой элементов может быть использован для построения устройств автоматики и вычислительной техники. Известны элементы вычислительной среды, содержащие триггеры, инверторы и схемы «И. Предлагаемый элемент отличается от известного тем, что в нем выходы первой и второй схем «И соединены с одним логическим полюсом элемента и с входом первого инвертора, другой логический полюс элемента связан с ВЫХОДОМ третьей схемы «И, с входом второй схемы «И и с входом второго инвертора. Это позволяет упростить элемент вычислительной среды. На фиг. 1 Приводится схема однородной среды и связей между элементами; на фиг. 2- функциональная схема элемента среды. На горизонтальные и вертикальные информационные шины 1 и 2 ,подаются логические переменные и формируются искомые функции. Элемент среды 3 одним информационным входом-выходом подключен к шине /, а другим- К шине 2, дву.мя настроечными входами- к горизонтальным настроечным шинам 4 и 5, третьим настроечным входом - к настроечной шине 6. На фиг. 1 приводится реализация переключательной функции , XzM Xi, Xz, заданной в дизъюнктивно-нормальной форме. Логические переменные i и 2 подаются с края структуры на горизонтальные шины. Функция / представляется в виде f Xi /XzVХ УXz. На первой слева вертикальной шине реализуется дизъюнкция вида , на второй - После этого на элементах третьей сверху строки первого и второго столбцов берется инверсия вида XiMXz и , подается на третью сверху горизонтальную шину, на которой осушествляется дизъюнкция. С нее сни.мается значение искомой функции. На фиг. 1 введены следующие обозначения: - - «пустой элемент; элемент среды, передающей сигнал с горизонтальной шины на вертикальную;-элемент среды, передающей инвертированный сигнал с горизонтальной шины на вертикальную;

Все пути на схеме .получаются одинаковой длины в том смысле, что задержка, вносимая средой при изменении состояния любого из входов, постоянна и равна 2т, где т - единичная задержка одного элемента среды.

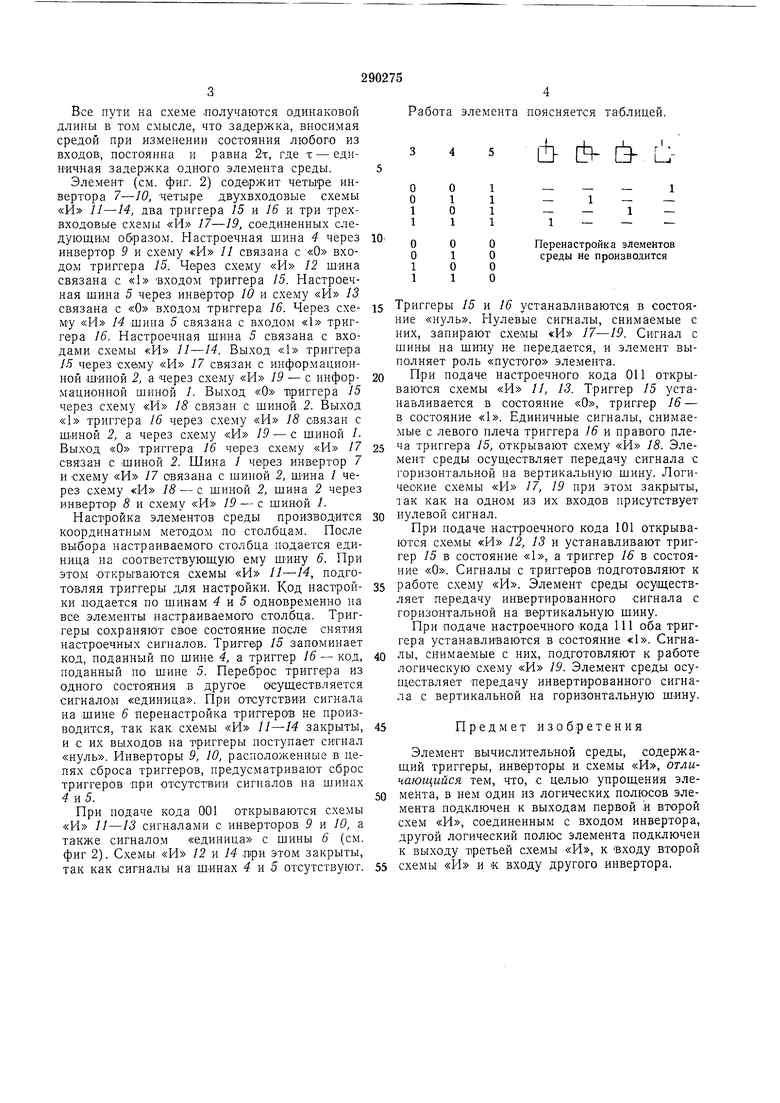

Элемент (см. фиг. 2) содержит четыре инвертора 7--10, четыре двухвходовые схемы «И 11-14, два триггера 15 -я 16 vi три трехвходовые схемы «И 17-19, соединенных следующиА образом. Настроечная шина 4 через инвертор 9 и схему «И 11 связана с «О входом триггера 15. Через схему «И 12 Шина связана с «1 входом триггера 15. Настроечная шина 5 через инвертор W и схему «И 13 связана с «О входом триггера 16. Через схему «И 14 шина 5 связана с входом «1 триггера 16. Настроечная шина 5 связана с входами схемы «И 11-14. Выход «1 триггера /5 через схему «И 17 связан с информационной -Шиной 2, а через схему «И 19 - с информационной шиной 1. Выход «О Tipnrrepa 15 через схему «И 18 связан с шиной 2. Выход « триггера 16 через схему «И 18 связан с ш.иной 2, а через схему «И 19 - с шиной /. Выход «О триггера 16 через схему «И 17 связан с шиной 2. Шина 1 через инвертор 7 и схему «И 17 связана с шиной 2, шяна / через схему «И 18 - с шиной 2, шина 2 через инвертор 8 и схему «И 19 - с шиной /.

Настройка элементов среды производится координатны1М методом по столбцам. После выбора настраиваемого столбца подается единица на соответствуюш;ую ему ш-ину 6. При этом открываются схемы «И 11-14, подготовляя триггеры для настройки. Код настройки .подается по шинам 4 vi 5 одновременно на все элементы настраиваемого столбца. Триггеры сохраняют свое состояние .после снятия настроечных сигналов. Триггер 15 запоминает код, поданный по шине 4, а триггер 16 - код, поданный по шине 5. Переброс триггера из одного состояния .в другое осуш.ествляется сигналом «единица. При отсутстви.и сигнала на шине 6 перенастройка триггеров не производится, так как схемы «И //-14 закрыты, и с их выходов на триггеры поступает сигнал «нуль. Инверторы 9, 10, расположенные в цепях сброса триггеров, предусматривают сброс триггеров При отсутствии сигналов на шинах 4 и 5.

При подаче кода 001 открываются схемы «И 11-13 сигналами с инверторов 9 10, & также сигналом «единица с шины 6 (см. фиг 2). Схемы «И 12 и 14 .при этом закрыты, так как сигналы на ш.инах 4 и 5 отсутствуют.

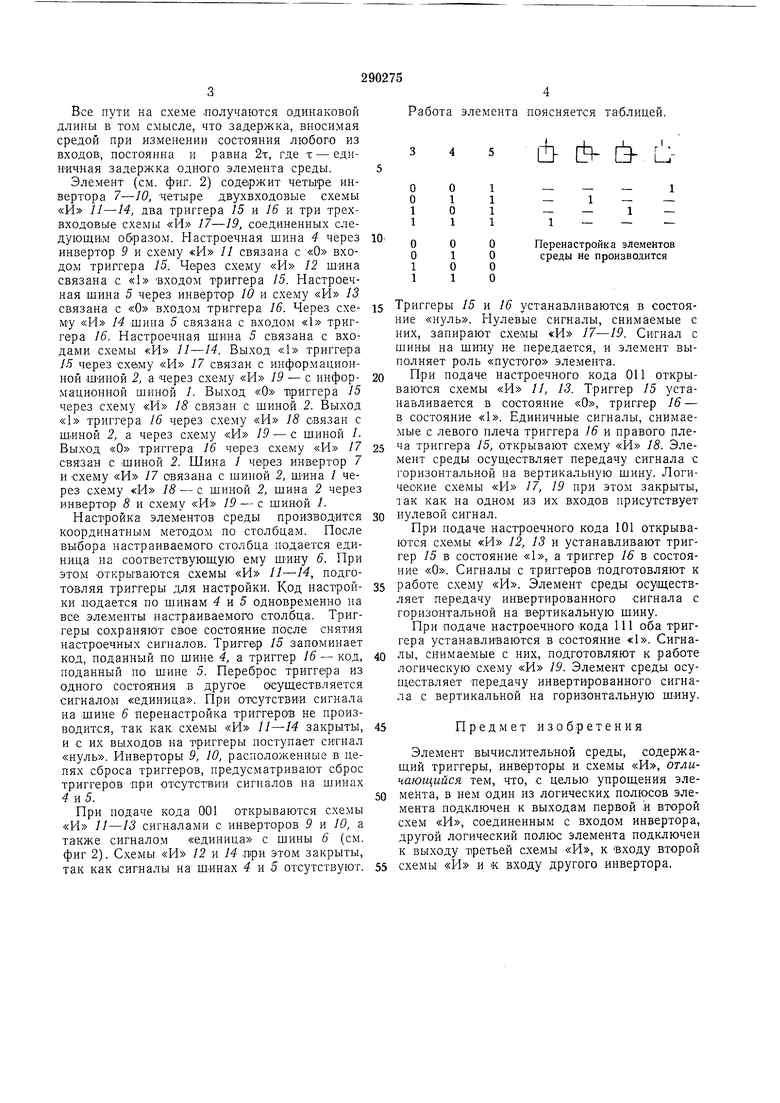

Работа элемента поясняется таблицей.

Q Й- - - 1

I

J

1 - - -

Перенастройка элементов среды не производится

Триггеры 15 и 16 устанавливаются в состояние «нуль. Нулевые сигналы, снимаемые с них, запирают схе.мы «И 17-19. Сигнал с шины на шину не передается, и элемент выполняет роль «пустого элемента.

Нри подаче настроечного кода 011 открываются схемы «И 11, 13. Триггер 15 устанавливается в состояние «О, триггер 16- в состояние «1. Единичные сигналы, снимаемые с левого плеча триггера 16 и правого плеча триггера 15, открывают схе.му «И 18. Элемент среды осуществляет передачу сигнала с горизонтальной на вертикальную шину. Логические схемы «PI 17, 19 при этом закрыты, так как на одном из их входов присутствует

нулевой сигнал.

При подаче настроечного кода 101 открываются схемы «И 12, 13 и устанавливают триггер 15 в состояние «1, а триггер 16 в состояние «О. Сигналы с триггеров -подготовляют к

работе схему «И. Элемент среды .осуществляет передачу инвертированного сигнала с горизонтальной на вертикальную шину.

При подаче настроечного кода 111 оба триггера устанавливаются в состояние «Ь. Сигналы, снимаемые с них, подготовляют к работе логическую схему «И 19. Элемент среды осушествляет передачу инвертированного сигнала с вертикальной на гориз.0нтальную шину.

Предмет изобретения

Элемент вычислительной среды, содержаший триггеры, инверторы и схемы «И, отличающийся тем, что, с целью уцрош,ения элемента, в нем один из логических полюсов элемента подключен к выходам первой .и второй схем «И, соединенным с входом инвертора, другой логический полюс элемента подключен к выходу третьей схемы «И, к входу второй

схемы «И и К входу другого инвертора,

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическая ячейка | 1975 |

|

SU577525A1 |

| МАТРИЧНЫЙ КОММУТАТОР С ПРОГРАММИРУЕМОЙ ЛОГИКОЙ | 2003 |

|

RU2251792C2 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1970 |

|

SU259475A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1969 |

|

SU255654A1 |

| Программируемое логическое устройство | 1984 |

|

SU1257702A1 |

| Программируемое запоминающее устройство | 1985 |

|

SU1282219A1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1972 |

|

SU355611A1 |

| БЛОК НАСТРОЙКИ ЯЧЕЙКИ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1973 |

|

SU407311A1 |

| ЯЧЕЙКА МАТРИЧНОЙ ОДНОРОДНОЙ СТРУКТУРЫ | 1973 |

|

SU395832A1 |

Даты

1971-01-01—Публикация