Изобретение относится к вычислительнбй Технике и может быть использовано для обработки частотно-импульсной информации.

Известны, устройства для умножения и Деления частотно-имоульспых сигналов, содержащие множительно-делительное устройство и дешифратор.

Однако эти устройства имеют недостаточную точность.

С целью повышения точности предлагаемое устройство содержит реверсивный счетчик, схемы сов-падения, линии задержки, реверсивный запоминающий регистр, вычитающие устройства, схему сборки и частотно-импульсную следящую систему, вход которой соединен с выходом миожительно-делительного устройства и со входом реверсивного счетчика, другой вход которого подключен к выходу частотноимлульсной следящей системы, выходы разрядов реверсивного счетчика соединены с первыми входами соответствующих схем совпадения, вторые входы которых соединены с одним из входов устройства, подключенного через линию задерл ки ко входам разрядов реверсивного счетчика, а выходы схем совпадения соединены со входами разрядов реверсивного запоминающего регистра, выходы которых подключены ко .входам дещиф ратора, выходами соединенного со входами двух схем совпадения, у одной из которых ко -входу соединена шина опорной частоты, а выход соединен с отрицательным входом реверсивного запоминающего регистра и первым входом вычитающего устройства, а у другой - ко

входу подключен выход частотно-импульсной следящей системы, а выход соединен с положительным входом реверсивного запоминающего регистра и вторым входом вычитающего устройства, один из выходов которого подключен через линию задержки к первому входу выходного вычитающего устройства, а другой - подключен ко входу схемы сборки, другой вход которой соединен с выходом частотно-импульсной следящей системы, а выход

схемы сборки подключен ко второму входу выходного вычитающего устройства.

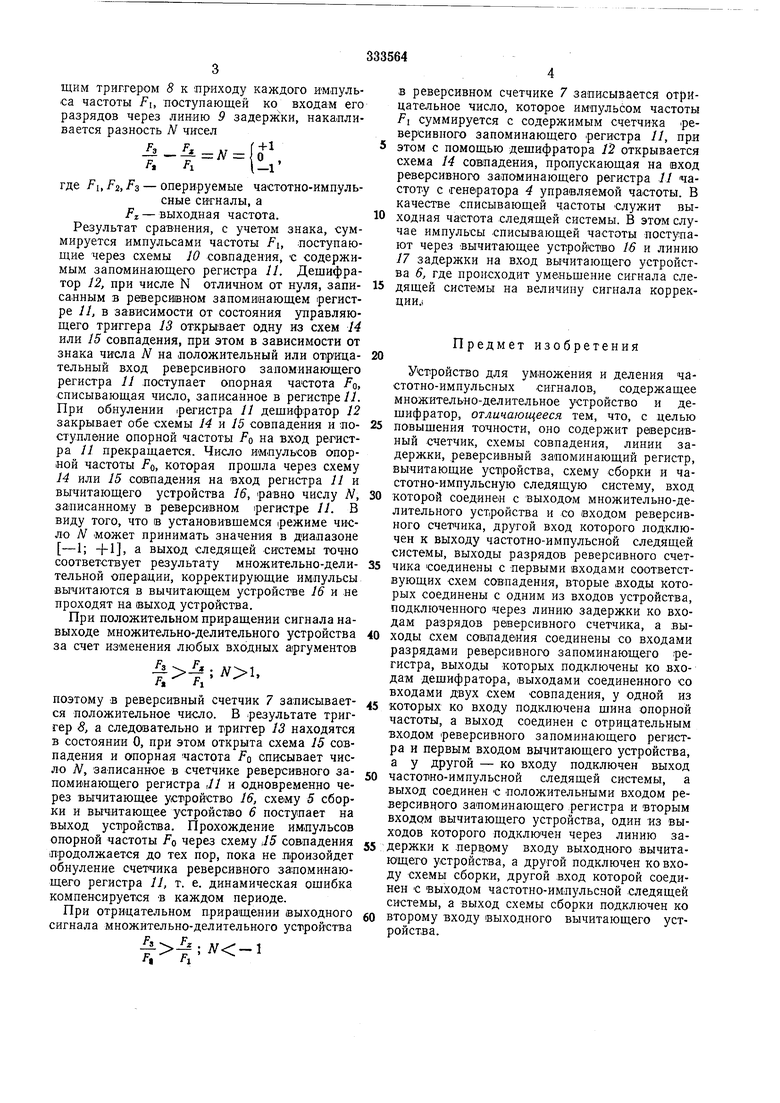

На чертеже приведена блок-схема предлагаемого устройства. В установившемся режиме с выхода Множительно-делительного устройства 1 на вход частотно-импульсной следящей системы, состоящей из реверсивного счетчика 2, преобразователя 3 кода в напряжение, генератора 4 упра.вляемой частоты, поступает лачечная последовательность импульсов, преставляющая результат множительно-делительной оиерацип. С выхода частотно-импульсной следящей системы сглаженный сигнал поступает через схему 5 сборки И выходное вычитающее устройстщим триггером 8 к приходу каждого импульса частоты FI, поступающей ко входам его разрядов через лииию 9 задержки, накапливается разность Л чисел

+1

N о

Ft

-1

где FI, FZ, РЗ - оперируемые частотно-импульсные сигналы, а Ff - выходная частота.

Результат сравнения, с учетом знака, суммируется импульсами частоты FI, поступающие через схемы JO совпадения, с содержимым запоминающего регистра 11. Дешифратор 12, при числе N отличном от нуля, записанным в реверсивном запоминающем регистре 11, в зависимости от состояния управляющего триггера 13 открывает одну из схем 14 или 15 совпадения, при этом в зависимости от знака часла N на .положительный или отрицательный вход реверсивного запоминающего регистра 11 поступает опорная частота FO, списывающая число, записанное в регистре 11. При обнулении .регистра // дешифратор 12 закрывает обе схемы 14 и 15 совпадения и :поступление опорной частоты FQ на вход регистра // прекращается. Число импульсов опорной частоты FO, которая прошла через схему 14 или 15 совпадения на вход регистра 11 и вычитающего устройства 16, равно числу N, записанному в реверсивном регистре 11. В виду того, что в установивщемся режиме число N может принимать значения в диапазоне -1; +1, а выход следящей системы тючно соответствует результату множительно-делительной операции, корректирующие импульсы вычитаются в вычитающем устройстве 16 и не проходят на выход устройства.

При положительном приращении сигнала навыходе множительно-делительного устройства за счет изменения любых входных аргументов

..

поэтому в реверсивный счетчик 7 записывается положительное число. В результате триггер S, а следовательно и триггер 13 находятся в состоянии О, при этом открыта схема 15 совпадения и опорная частота о списывает число N, записанное в счетчике реверсив-ного запоминающего регистра ,11 и одновременно через вычитающее устройство 16, схему 5 сборки и вычитающее устройство 6 поступает на выход устройства. Прохождение имлульсов опорной частоты FO через схему ,75 сов-падения продолжается до тех пор, пока не произойдет обнуление счетчика реверсивного запоминающего регистра 11, т. е. динамическая ошибка компенсируется в каждом периоде.

При отрицательном приращении выходного сигнала множительно-делительного устройства

м а

в реверсивном счетчике 7 запнсываетсй отрицательное число, которое импульсом частоты FI суммируется с содержимым счетчика реверсивного запоминающего регистра 11, при этом с помощью дешифратора 12 открывается схема 14 совпадения, пропускающая на вход реверсивного запоминающего регистра 11 частоту с генератора 4 управляемой частоты. В качестве списывающей частоты служит выходная частота следящей системы. В этом случае импульсы списывающей частоты поступают через вычитающее устройство 16 и линию 17 задержки на вход вычитающего устройства 6, где происходит уменьшение сигнала следящей системы на величину сигнала коррекции.

Предмет изобретения

Устройство для умножения и деления частотно-импульсных сигналов, содержащее множительно-делительное устройство и дешифратор, отличающееся тем, что, с целью

повышения точности, оно содержит реверсивный счетчик, схемы совпадения, линии задержки, реверсивный запоминающий регистр, вычитающие уст1ройства, схему сборки и частотно-импульсную следящую систему, вход

которой соединен с выходом множительно-делительного устройства и со входом реверсивного счетчика, другой вход которого подключен к выходу частотно-импульсной следящей системы, выходы разрядов реверсивного счетчика соединены с первыми входами соответствующих схем совпадения, вторые входы которых соединены с одним из входов устройства, подключенного через линию задержки ко входам разрядов реверсивного счетчика, а выходы схем совпадения соединены со входами разрядами реверсивного запоминающего регистра, выходы которых подключены ко входам дешифратора, выходами соединенного со входами двух схем совпадения, у одной из

которых ко входу подключена шина опорной частоты, а выход соединен с отрицательным входом реверсивного запоминающего регистра и первым входом вычитающего устройства, а у другой - ко входу подключен выход

частотно-импульсной следящей системы, а выход соединен с положительными входом реверсивного запоминающего регистра и вторым входом вычитающего устройства, один из выходов которого подключен через линию задержки к перв.ому входу выходного вычитающего устройства, а другой подключен ко входу схемы сборки, другой вход которой соединен с выходом частотно-импульсной следящей системы, а выход схемы сборки подключен ко

второму входу выходного вычитающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВРЕМЯ-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU363990A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU419921A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU399865A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ ВЫЧИТАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU284442A1 |

| Частотно-импульсный функциональный преобразователь | 1982 |

|

SU1023342A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| ОДТЕНТНО-ТЕХНН-Г- :^':и|БИБЛИОТЕКА | 1970 |

|

SU287404A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1995 |

|

RU2097829C1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1972 |

|

SU424188A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО- ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО-^ | 1973 |

|

SU375651A1 |

Даты

1972-01-01—Публикация