Известны устройства для регистрации последовательности двоичных сигналов, считываемых с однодорожечной магнитной ленты, содержащие расщепитель сигнала по полярности, к выходам которого подключены два канала обработки, каждый из которых имеет схему совпадения с подключенной к ее выходу цепочкой из делителя частоты следования импульсов и схемы «ИЛИ.

Предлагаемое устройство отличается от известного тем, что в нем проведена коррекция ощибок приема до восстановления каждого пропущенного сигнала и запрещения каждого ложного. Для этой цели введен не один, а два канала обработки и узлы исправления ощибок принятых двоичных сигналов, что обеспечивает уменьщение вероятности при ощибке приема при укорочении и удлинении принятых двоичных электрических сигналов по длительности.

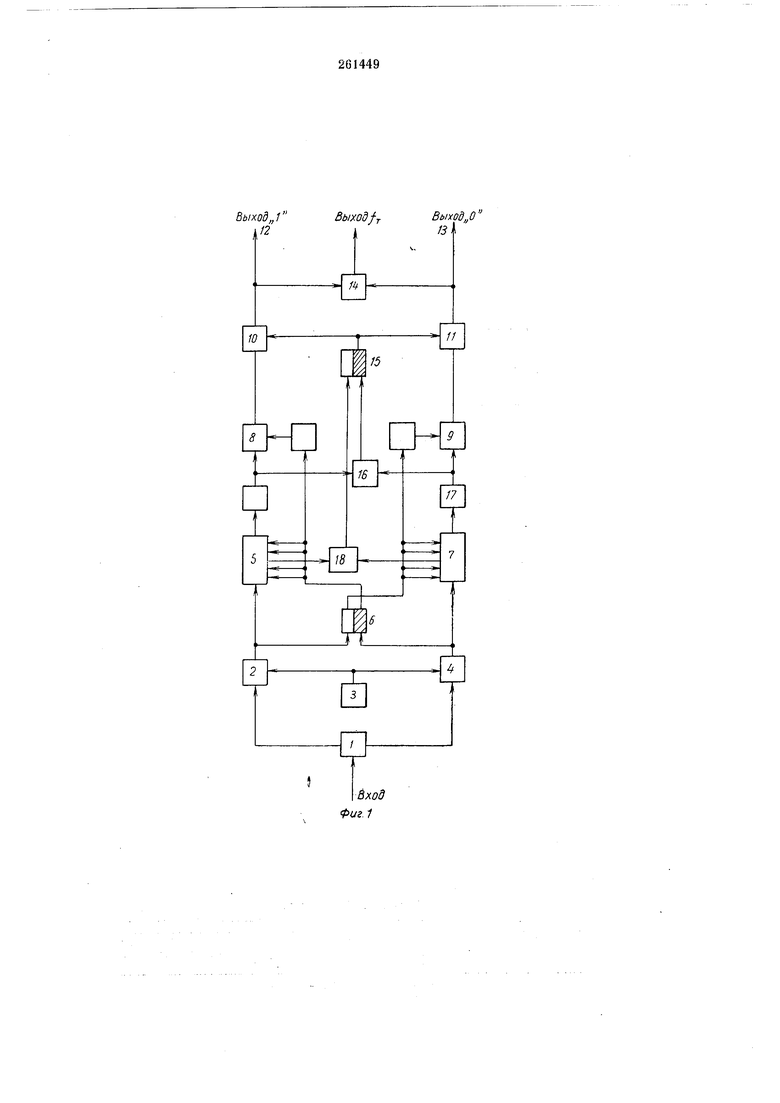

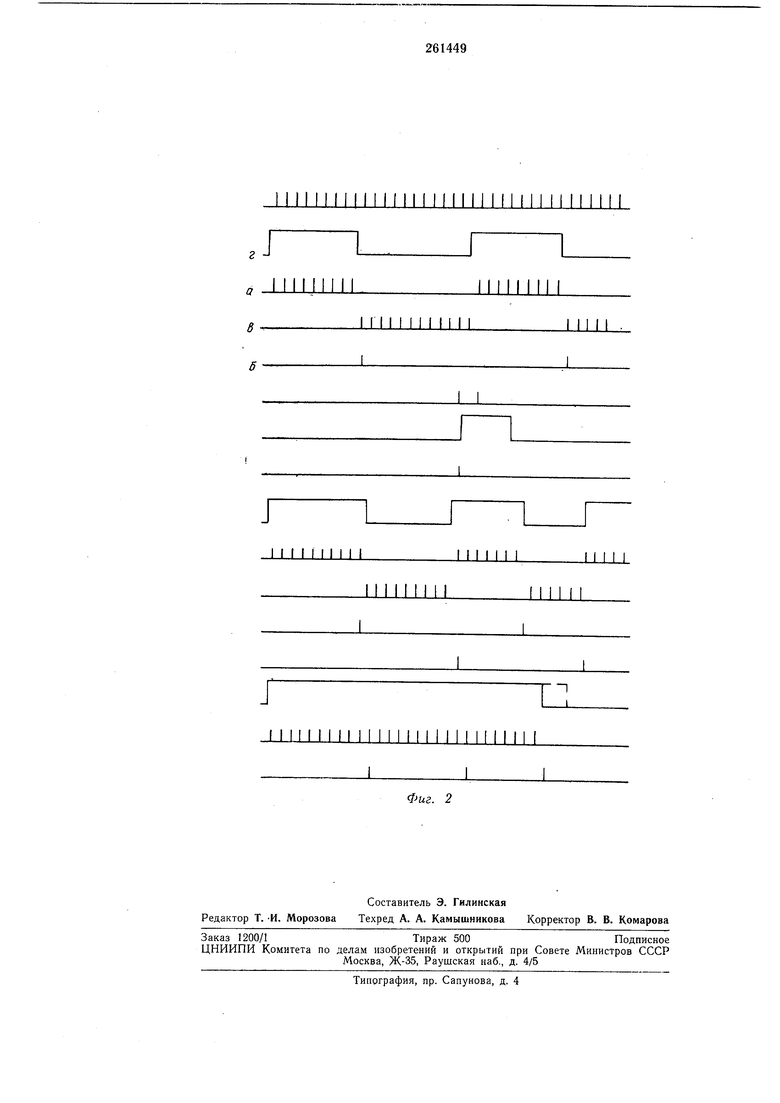

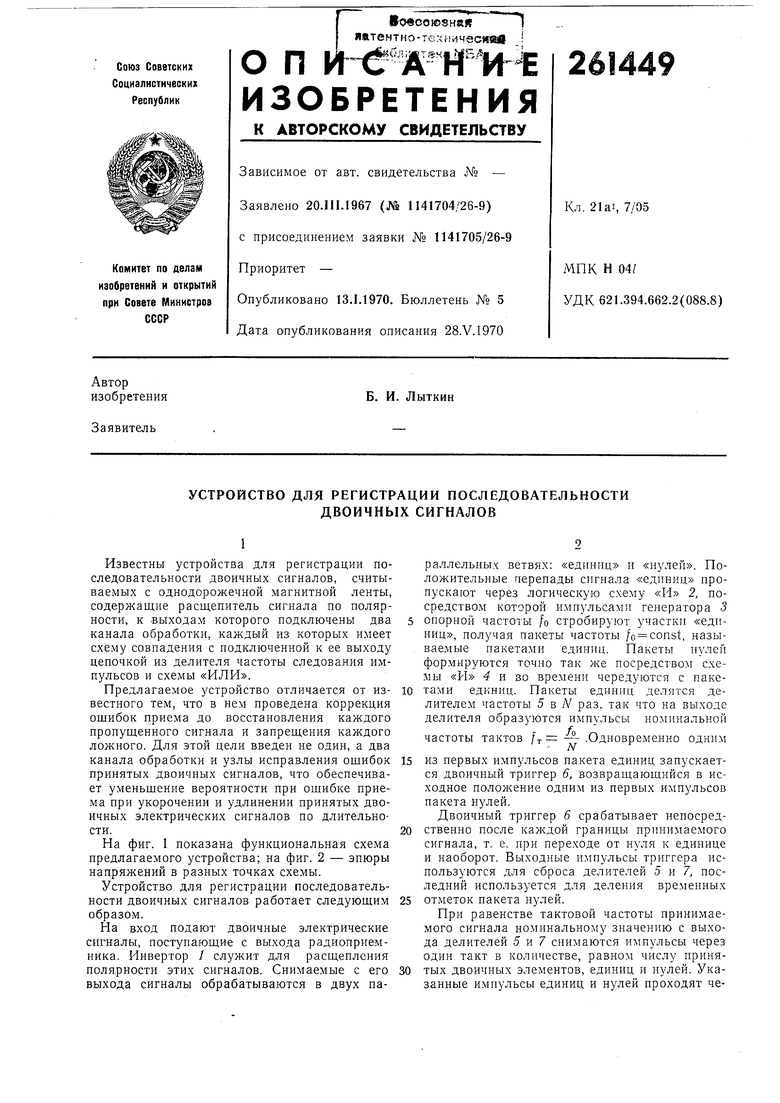

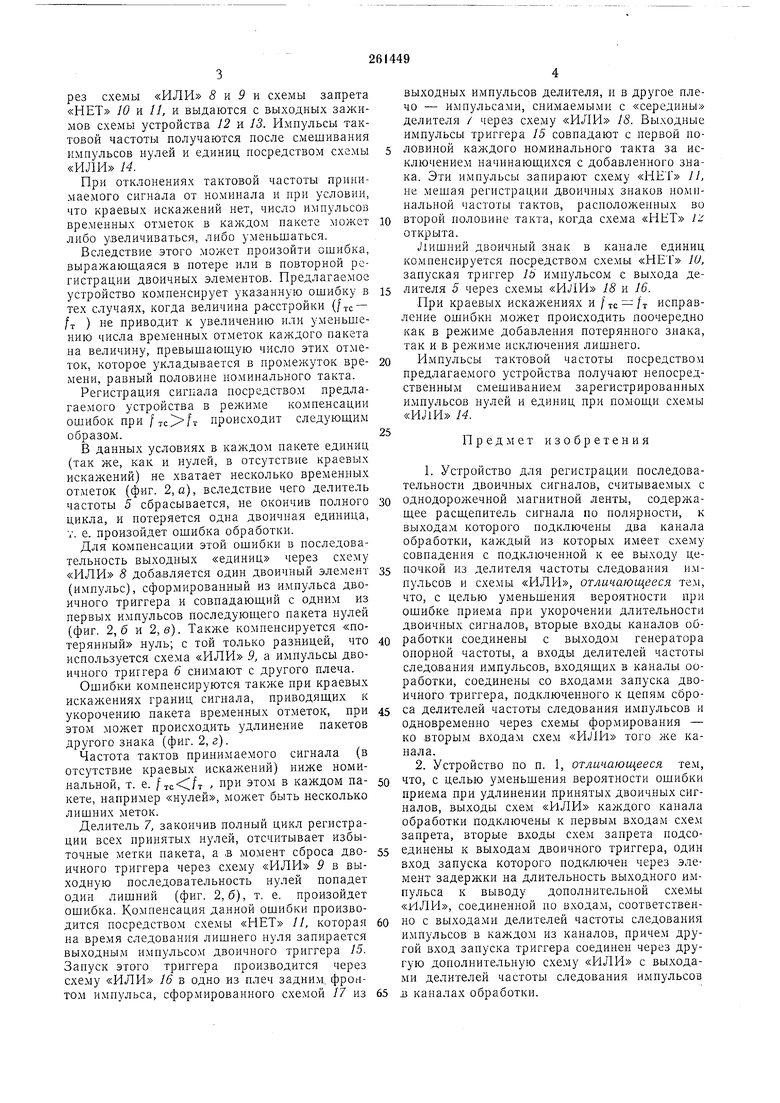

На фиг. 1 показана функциональная схема предлагаемого устройства; на фиг. 2 - эпюры напряжений в разных точках схемы.

Устройство для регистрации последовательности двоичных сигналов работает следующим образом.

На вход подают двоичные электрические сигналы, поступающие с выхода радиоприемника. Инвертор / служит для расщепления полярности этих сигналов. Снимаемые с его выхода сигналы обрабатываются в двух параллельных ветвях: «единиц и «нулей. Положительные перепады сигнала «единиц пропускают через логическую схему «И 2, посредством которой импульсами генератора 3 опорной частоты fo стробируют участки «единиц, получая пакеты частоты /о const, называе.мые пакетами единиц. Пакеты нулей формируются точно так лее посредством схемы «И 4 и во времени чередуются с пакетами единиц. Пакеты единиц делятся делителем частоты 5 в Л раз, так что на выходе делителя образуются импульсы номинальной

частоты тактов /т - -Одновременно одним

Л

из первых импульсов пакета единиц запускается двоичный триггер 6, возвращающийся в исходное положение одним из первых импульсов пакета нулей.

Двоичный триггер 6 срабатывает непосредственно после каждой границы принимаемого сигнала, т. е. ири переходе от нуля к единице и наоборот. Выходные и.мпульсы триггера используются для сброса делителей 5 и 7, последний используется для деления временных отметок пакета нулей.

При равенстве тактовой частоты принимаемого сигнала номинальному значению с выхода делителей 5 и 7 снимаются импульсы через один такт в количестве, равном числу принятых двоичных элементов, единиц и нулей. Указанные импульсы единиц и нулей проходят через схемы «ИЛИ S и 5 и схемы запрета «НЕТ 10 и 11, и выдаются с выходных зажимов схемы устройства 12 и 13. Импульсы тактовой частоты получаются после смешивания импульсов пулей и единиц посредством схемы «ИЛИ 14. При отклонениях тактовой частоты принимаемого сигнала от номинала и при условии, что краевых искажений нет, число имиульсов временных отметок в каждом пакете может либо увеличиваться, либо умепьшаться. Вследствие этого может произойти ошибка, выражаюш,аяся в потере или в повторной регистрации двоичных элементов. Предлагаемое устройство компенсирует указанную ошибку в тех случаях, когда величина расстройки (/тс /т ) пе приводит к увеличению или уменьшению числа временных отметок каждого пакета на величину, превышающую число этих отметок, которое укладывается в промежуток времени, равный половине номинального такта. Регистрация сигнала посредством предлагаемого устройства в режиме компенсации ошибок при происходит следующим образом. В данных условиях в каждом пакете единиц (так же, как и пулей, в отсутствие краевых искажений) не хватает несколько временных отметок (фиг. 2, а), вследствие чего делитель частоты 5 сбрасывается, не окончив полного цикла, и потеряется одна двоичная единица, V. е. произойдет ошибка обработки. Для компенсации этой ошибки в последовательность выходных «единиц через схему «ИЛИ 8 добавляется один двоичный элемент (импульс), сформированный из импульса двоичного триггера и совпадаюший с одним из первых импульсов последующего пакета нулей (фиг. 2,6 и 2, е). Также компенсируется «потерянный нуль; с той только разницей, что используется схема «ИЛИ 9, а импульсы двоичного триггера 6 снимают с другого плеча. Ошибки компенсируются также при краевых искажениях границ сигнала, приводящих к укорочению пакета временных отметок, при этом может происходить удлинение пакетов другого знака (фиг. 2, г). Частота тактов принимаемого сигнала (в отсутствие краевых иекал ений) ниже номинальной, т. е. /. при этом в каждом пакете, например «нулей, может быть несколько лишних меток. Делитель 7, закончив полный цикл регистрации всех принятых нулей, отсчитывает избыточные метки пакета, а .в момент сброса двоичного триггера через схему «ИЛИ 9 в выходную последовательность нулей попадет один лищпий (фиг. 2,6), т. е. произойдет ошибка. Компенсация данной ошибки производится посредством схемы «НЕТ 11, которая на время следования лишнего пуля запирается выходным импульсом двоичного триггера 15. Запуск этого триггера производится через схему «ИЛИ 16 в одно из плеч задним, фронтом импульса, сформированного схемой 17 из выходных импульсов делителя, и в другое плечо - импульсами, снимаемыми с «середины делителя / через схему «ИЛИ 18. Выходные импульсы триггера 15 совпадают с первой половиной каждого номинального такта за исключением начинающихся с добавленного знака. Эти импульсы запирают схему «НЕТ 11, не мешая регистрации двоичных знаков номинальной частоты тактов, расположенных во второй половине такта, когда схема «НЕТ Уоткрыта. Лишний двоичный знак в канале единиц компенсируется посредством схемы «НЕТ W, запуская триггер 16 импульсом с выхода делителя 5 через схемы «ИЛИ 18 и 16. При краевых искажениях и /тс -/т исправление ошибки может происходить поочередно как в режиме добавления потерянного знака, так и в режиме исключения лишнего. Импульсы тактовой частоты посредством предлагаемого устройства получают непосредственным смешиванием зарегистрироваппых импульсов нулей и единиц при помощи схемы «ИЛИ 14. „ Предмет изооретения 1. Устройство для регистрации последовательности двоичных сигналов, считываемых с однодорожечиой магнитной лепты, содержащее расщепитель сигнала по полярности, к выходам которого подключены два канала обработки, каждый из которых имеет схему совпадения с подключенной к ее выходу цепочкой из делителя частоты следования импульсов и схемы «ИЛИ, отличающееся тем, что, с целью уменьщения вероятности при ощибке приема при укорочении длительности двоичных сигналов, вторые входы каналов обработки соединены с выходом генератора опорной частоты, а входы делителей частоты следования импульсов, входящих в каналы ооработки, соединены со входами запуска двоичного триггера, подключенного к цепям сброса делителей частоты следования импульсов и одновремеппо через схемы формирования - ко вторым входам схем «ИЛИ того же капала. 2. Устройство по п. 1, отличающееся тем, что, с целью уменьшения вероятности ошибки приема при удлипении принятых двоичных сигпалов, выходы схем «Р1ЛИ каждого капала обработки подключены к первым входам схем запрета, вторые входы схем запрета подсоединены к выходам двоичного триггера, один вход запуска которого подключен через элемент задержки па длительность выходного импульса к выводу дополнительной схемы ИЛИ, соединенной по входам, соответствено с выходами делителей частоты следования мпульсов в из каналов, причем друой вход запуска триггера соедипеи через друую дополнительную схему «ИЛИ с выходаи делителей частоты следования импульсов

Выход„1

Bbixodfr 12

Bbii(od,,0 /JM

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 1971 |

|

SU319096A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Устройство для формирования кода времени | 1978 |

|

SU763845A1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| Способ синхронной передачи дискретной информации в волоконно-оптических системах связи | 1989 |

|

SU1688430A1 |

| Устройство для приема биимпульсных сигналов | 1987 |

|

SU1471315A1 |

| Устройство для приема последовательности двоичных сигналов | 1985 |

|

SU1343557A1 |

| Устройство для считывания графической информации | 1974 |

|

SU669363A2 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

Фиг. 1

Вход

I I I I I I I I I I

I I

Фиг. 2

Даты

1970-01-01—Публикация