Настоящее изобретение относится к области лередачи сообщений и быть использовало в системах передачи дискретной информ.ации с рещающей обратной связью.

Известны системы передачи дискретной информации с рещающей обратной связью, в которых, кроме «О и «1, предусматривается передача третьей позиции, соответствующей сигналу «Запрос. Они содержат блок переключения, два триггера, делитель частоты на два, делитель частоты на семь, ячейку памяти, блок для Обнаружения ощибок и выходное передающее реле.

Предлагаемое устройство отличается от известных тем, что с целью обеспечения высокой надежности приема .выходы делителя частоты на два соединены соответственно с двумя входами первого триггера, выходы первого триггера соединены со входами выходного передающего реле, выход «передающего реле.соединен со входом блока переключения; -первый выход делителя частоты на семь, соответствующий первому такту, соединен с первым входом второго триггера, а второй выход, соответствующий третьему такту, соединен со входом ячейки памяти, второй вход ячейки памяти соединен с выходом блока для обнаружения ощибки, а выход соединен со вторым входом второго триггера, первый и второй выходы второго триггера Соединены соответствепйо со входами блоха переключения.

Принцип работы устройства заключается в том, что при обнаружении ощибки в кодовом

элементе на передающую станцию посылается сигнал «Запрос, который представляет собой последовательность из элементарных имлульсов, сдвинутых -по отнощению к кодовым на половину длительности элементарного и.мпульса. Таким образом, на вход приемника будут поступать искан енные импульсы, одна половина которых имеет положительную полярность, а другая - отрицательную.

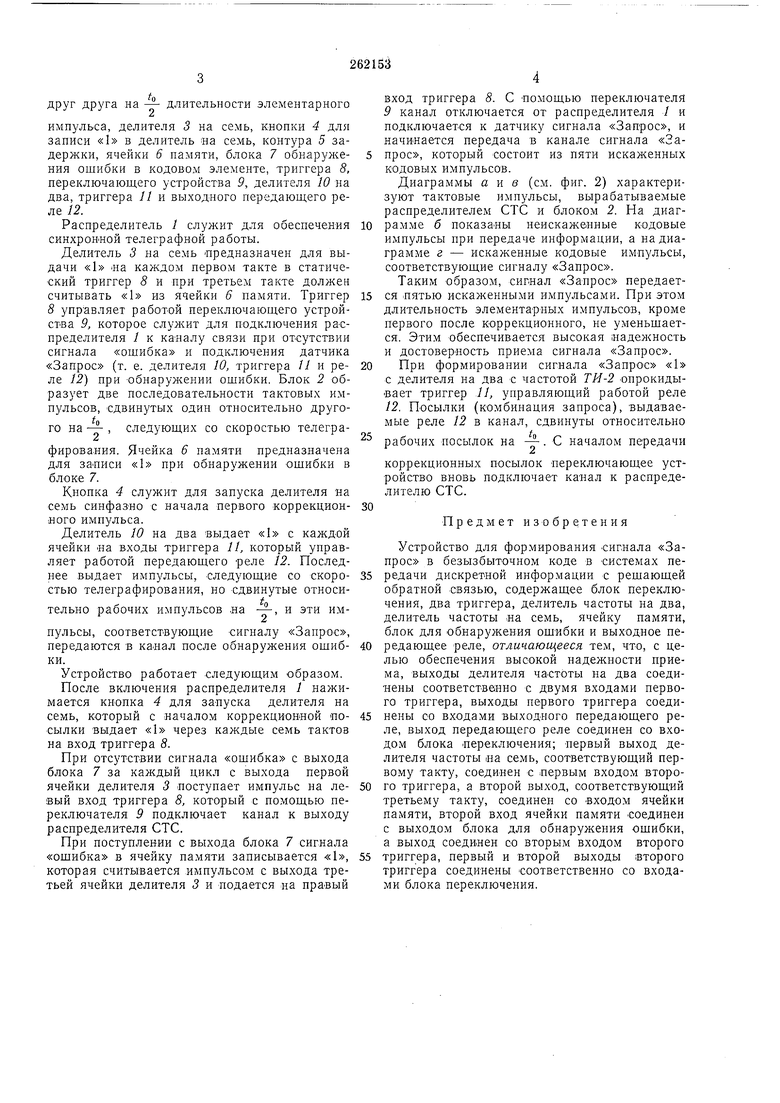

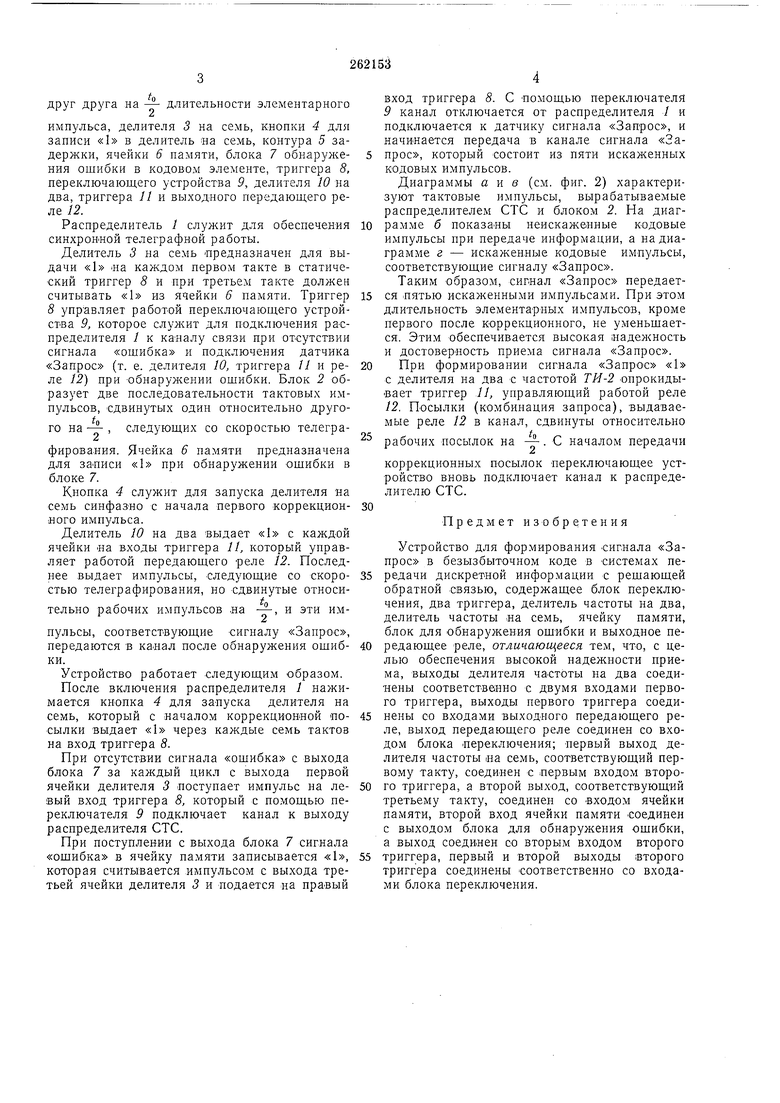

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - диаграммы тактовых, коррекционных и кодовых импульсов: а - тактовые импульсы ТИ-1, формирующие неискаженные кодовые импульсы; б - неискажепные кодовые импульсы; в - тактовые импульсы ТИ-2, формирующие искаженные кодовые импульсы; г - искаженные кодовые импульсы, используемые в качестве сигнала «Запрос.

Оно состоит из передающего распределителя / синхронного телеграфного устройства (СТС), блока 2 формирования двух последовательностей тактовых импультов TH-J и ТИ-2 с частотой следования, равной скорости

0

друг друга на - длительности элементарного

импульса, делителя 3 на семь, кнопки 4 для записи «1 в делитель иа семь, контура 5 задержки, ячейки 6 памяти, блока 7 обнаружения ошибки в кодовом элементе, триггера 8, переключающего устройства 9, делителя 10 на два, триггера 11 и выходного передающего реле 12.

Распределитель 1 служит для обеспечения синхронной телеграфной работы.

Делитель 3 на семь предназначен для выдачи «1 «а каждом первом такте в статический триггер 8 и при третьем такте должен считывать «1 из ячейки 6 памяти. Триггер 8 управляет работой переключающего устройства 9, которое слулсит для подключения распределителя / к каналу связи при отсутствии сигнала «ощибка и подключения датчика «Запрос (т. е. делителя 10, триггера 11 и реле 12) при обнаруж:ении ошибки. Блок 2 образует две последовательности тактовых импульсов, сдвинутых один относительно другоtuго на - , следующих со скоростью телегра i

фирования. Ячейка 6 памяти предназначена для за-писи «1 при обнаружении ошибки в блоке 7.

Кнопка 4 служит для запуска делителя на семь синфаЗНО с начала первого коррекционного импульса.

Делитель 10 на два выдает «1 с каждой ячейки «а входы триггера II, который управляет работой передающего реле 12. Последнее выдает импульсы, следующие со скоростью телеграфирования, но сдвинутые относительно рабочих импульсов на , и эти импульсы, соответствующие сигналу «Запрос, передаются в калал после обнаружения ошибки.

Устройство работает следующим образом.

После включения распределителя I нажимается кнопка 4 для запуска делителя на семь, который с началом коррекционной посылки выдает «1 через каждые семь тактов на вход триггера S.

При отсутствии сигнала «ошибка с выхода блока 7 за каждый цикл с выхода первой ячейки делителя 3 поступает импульс на левый вход триггера 8, который с помощью переключателя 9 подключает канал к выходу распределителя СТС.

При поступлении с выхода блока 7 сигнала «ошибка в ячейку памяти записывается «1, которая считывается импульсом с выхода третьей ячейки делителя 5 и подается на правый

вход триггера 8. С помошью переключателя 9 канал отключается от распределителя / и подключается к датчику сигнала «Запрос, и начинается передача в канале сигнала «Запрос, который состоит из пяти искаженных кодовых импульсов.

Диаграммы а и е (см. фиг. 2) характеризуют тактовые импульсы, вырабатываемые распределителем СТС и блоком 2. На диаграмме б показаны неискаженные кодовые импульсы при передаче информации, а на диаграмме г - искаженные кодовые импульсы, соответствуюшие сигналу «Запрос. Таким образом, сигнал «Запрос передается пятью искаженными импульсами. При этом длительность элементарных импульсов, кроме первого после коррекционного, не у.меньшается. Этим обеспечивается высокая надежность и достоверность приема сигнала «Запрос.

При формировании сигнала «Запрос «1 с делителя на два с частотой Т И-2 опрокидывает триггер И, управляющий работой реле 12. Посылки (комбинация запроса), выдаваемые реле 12 в канал, сдвинуты относительно

рабочих посылок на -. С началом передачи

t

коррекционных посылок переключающее уст ройство вновь подключает капал к распределителю СТС.

Предмет изобретения

Устройство для формирования сигнала «Запрос в безызбыточном коде в системах передачи дискретной информации с рещающей обратной связью, содержащее блок переключения, два триггера, делитель частоты на два, делитель частоты на семь, ячейку памяти, блок для обнаружения ощибки и выходное передающее реле, отличающееся тем, что, с целью обеспечения высокой надежности приема, выходы делителя частоты на два соединены соответственно с двумя входами первого триггера, выходы первого триггера соединень со входами выходного передающего реле, выход передающего реле соединен со входом блока переключения; первый выход делителя частоты (На семь, соответствующий первому такту, соединен с первым входом второго триггера, а второй выход, соответствующий третьему такту, соединен со входом ячейки памяти, второй вход ячейки памяти соединен с выходом блока для обнаружения ощибки, а выход соединен со вторым входом второго

триггера, первый и второй выходы второго триггера соединены соответственно со входами блока переключения.

/W

/

1

ти-1 T/fH

yi Rlfl/lgm гн-2///////

ТН-1 i5. /

Вло

:

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ УСТОЙЧИВОСТИ ФАЗИРУЮЩИХ УСТРОЙСТВ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ | 1968 |

|

SU211151A1 |

| СПОСОБ АНАЛИЗА ПРИНЯТЫХ КОДОВЫХ КОМБИНАЦИЙ | 1966 |

|

SU187395A1 |

| Устройство синхронизации по циклам | 1975 |

|

SU544160A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для обмена информацией | 1986 |

|

SU1363228A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙКОМБИНАЦИИ | 1971 |

|

SU293243A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКИХ КОДОВ | 1971 |

|

SU317066A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

/{oflpff nuo HMe/foi oSh/e ./

ампу/ е сы.

- 1IIII

Даты

1970-01-01—Публикация