Ивобретение относится к области технической диагностики устройства ЦВМ и может быть использовано при 1ПО|строении и эксплуатации 1матри чных сперати-вных запоминающих у1СТ|рОЙ1СТ1В.

Известны оперативные запоминающие устройства (ОЗУ), содерл :ащие куб накопительных матриц, « которому подключен адресный тракт ОЗУ, .блок контроля и блок управления.

Их недостатками является то, что устройство контроля ле решает задачу .коррекции обоя; исключается возможность достове1рного обнаружения аши1бки; разрешающая апо собнасть у1строЙ1ст1ва контроля с точностью до разряда ЧИСЛОВОГО тракта МОЗУ для некоторых типов конструкции неудовлетворительна, организация контроля таким способом уменьшает длительность выдаваемых в числовую магистраль информационных сигналов.

.Предлагаемое устройство отличается от известных тем, что блак контроля содержит регистр контроля, генератор тактовых емпульсав, счетчи1К ажрбса ячеек памяти, дешифратор 1координат неиюправностей, узел формирования сигнала «Oinpoc дешифратора координат неисправностей, узел формирования сигнала «Строб и узел блокировки сигнала «Оброс, ко входу дешифратора подключены выходы узла фор ми1равания сигнала «Опрос

дешифратора координат неисправностей, выходы регистра числа числового тракта ОЗУ и регистра контроля, соответствующие входы которого соединены с выхода1М1И клапанов, связанных с усилителями считывания числового тракта ОЗУ и узлом форлшрования сигнала «Строб, причем входы узла (блокировки сигнала «Сброс подключены ,к выходу блока уп|равления и к выходу дешифратора координат неисправностей, выход генератора тактовых импульсов подключен IKO выходу клапана, а выход клапана .подключен ко входу счетчика адресов и через сОбирательную схему - ко входу блока у1правления; причем выход счетчика адресов соединен со входом регистр адреса числового тракта ОЗУ.

Это позволяет обнаружить и скорректировать обой.

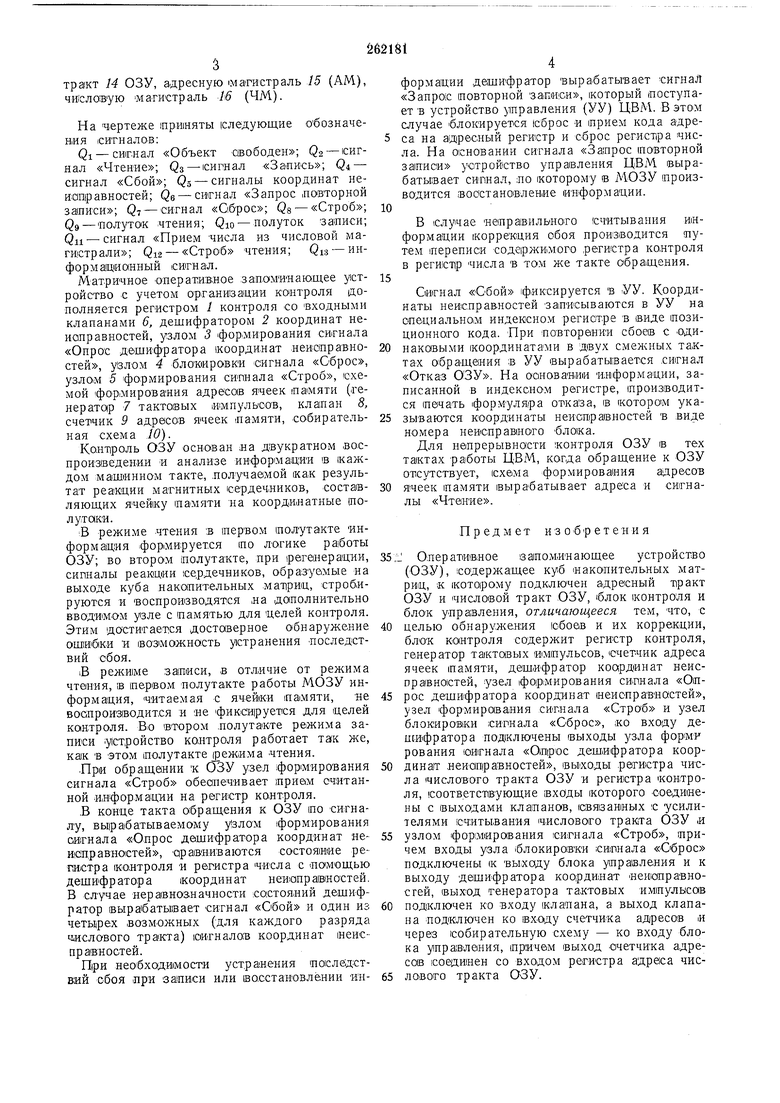

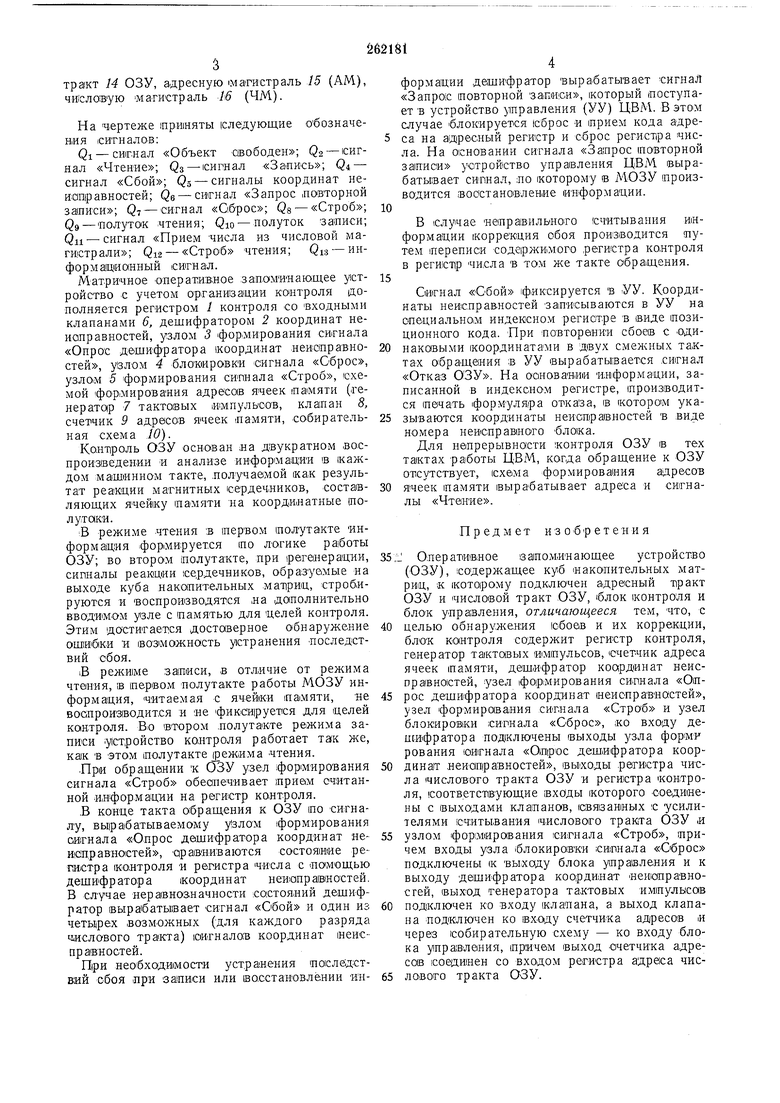

На чертеже дана схема предлагаемого устройства.

Устройство содержит регистр 1 контроля, дешифратор 2 координат неисправностей, узел 3 форМ.ирования сигнала «Опрос дешифратора координат неисправностей, узел 4 блокировки сигнала «Оброс, узел 5 формирования «Строб, клаиаяы 6, генератор 7 тактовых импульсов, клапан 8, очетчик 9 адресов ячеек памяти, собирательную схему 10, блок // управления ОЗУ, адресный тракт 12 ОЗУ, куб 13 накопительных (Матриц ОЗУ, числовой

тракт М ОЗУ, адресную магистраль /5 (AM), Числовую магистраль 16 (ЧМ).

На чертеже шриняты (следующие обозначения сигналов;

QI - сиг.нал «Объект авободен ; Qs - сигнал «Чтение ; Qs - сигнал «Зались ; Q4 - сигнал «Сбой ; Qs - сигналы координат неиацравностей; Qe - сигнал «Запрос лавторной записи ; Q -сигнал «Оброс ; Qs - «Отроб ; QQ - Полуто1К чтения; Qio - полуток заниси; Qii--сигнал «Прием числа из числовой магистрали ; Qi2 - «Строб чтения; Qia - информащианный сигнал.

Матричное оперативное запомИнающее yicTройство с учетом организации контроля дополняется регистром 1 контроля со входными клапанами 6, дешифратором 2 координат неиаправностей, узлом 3 фор мирования сигнала «Опрос дешифратора координат неисправностей, УЗЛОМ 4 блок1ир0(вки сигнала «Сброс, узлом 5 формирования сигнала «Строб, схемой формирования адресов ячеек юамяти (генератор 7 тактовых импульсов, клапан 8, счетчик 9 адресов ячеек памяти, собирательная схема 10).

Ко.нт|роль ОЗУ основан на двукратном воспроизведении и анализе инфор1ма ЦИи в каждом машинном такте, лолучаемой как результат реакции магнитных сердечников, составляюш,их ячейку 1памяти на координатные |полутаки.

:В режиме чтения в первом (полутакте информация |фор|Мируется 1ПО логике работы ОЗУ; во втором полутакте, при регенеращии, сигналы сердечников, образуемые на выходе куба накапительных мат|ри1ц, стробируются и воспроизводятся на дополнительно вводимом узле с памятью для целей контроля. Этим достигается достоверное Oiбнapyжeниe ошибки и 1воэможность у1странения последствий сбоя.

iB режиме записи, в отличие от режима чтения, в первом полутакте работы МОЗУ информация, читаемая с ячейки ламяти, не воспроизводится и не фиксируется для целей контроля. Во втором полутакте режима записи устройство контроля работает так же, как в этом полутакте режима чтения.

.При обращении к ОЗУ узел формирования сигнала «Строб обеапечивает лриам считанной информации на регистр контроля.

В конце такта обращения к ОЗУ по сигналу, вырабатываемому у1злом формирования сигнала «Опрос дешифратора координат неишравностей, сравниваются состояние регистра контроля и регистра числа с помощью дешифратора координат неи1апра1В1ностей. В случае неравнозначности состояний дешифратор выра1батывает сигнал «Сбой и один из четьцрех возможных (для каждого разряда числового тракта) сигналов координат неисправностей.

формации дешифратор выра-батьгвает сигнал «Запрос повторной записи, который поступает в устройство управления (УУ) ЦВМ. В этом случае блокируется сброс и прием кода адреса на адресный регистр и сброс регистра числа. На основании сигнала «Sainpoc повторной записи устройство управления ЦВМ вырабатывает сигнал, :по которому в МОЗУ производится восстановление информации.

В случае неправильного считывания информации коррекция сбоя производится путем переписи содержимого регистра контроля в регисир числа в том же такте обращения.

Сигнал «Сбой |ф,иксируется в УУ. Координаты неисправностей записываются в УУ на специальном индексном региатре в виде позиционного кода. При повторении сбоев с одинаковыми координатами в двух смежных тактах обращения в УУ вырабатывается сигнал «Отказ ОЗУ. На ооновании информации, записанной в индексном регистре, производится печать формуляра отказа, в котором указываются координаты неисправностей в виде номера неисправного -блока.

Для непрерывности контроля ОЗУ в тех TaiKTax работы ЦВМ, когда обрашение к ОЗУ отсутствует, схема формирования адресов

0 ячеек памяти вырабатывает адреса и сигналы «Чтение.

Предмет и з о -б р е т е н и я

5;J Оперативное запоминающее устройство (ОЗУ), содерл ащее куб накопительных матриц, к которому подключен адресный тракт ОЗУ и числовой тракт ОЗУ, блок контроля и блок управления, отличающееся тем, что, с

0 целью обнаружения (сбоев и их коррекции, блок контроля содержит регистр контроля, генератор тактовых емпульсов, счетчик адреса ячеек памяти, дешифратор координат неисправностей, узел формирования сигнала «Oin5 рос дешифратора координат неисправностей, узел формирования сигнала «Строб и узел блокировки сигнала «Сброс, ко входу децшфратора подключены выходы узла форми рования юигнала «Опрос дешифратора координат неиаправностей, выходы регистра числа числового тракта ОЗУ и регистра контроля, соответствующие входы которого соединены с выходами клапанов, ювяванных с усилителями считывания числового тракта ОЗУ .и

5 узлом формирования сигнала «Строб, причем входы узла |блокиро вки сигнала «Сброс подключены к выходу блока управления и к выходу дешифратора координат неиаправносгей, выход генератора тактовых им1пулБсов

подключен ко входу клапана, а выход клапана подключен ко входу счетчика адресов и через собирательную схему - ко входу блока упра1вления, причем выход очетчика адресов соединен со входом регистра адреса чис8,

Q fisfi.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Устройство для сопряжения | 1980 |

|

SU962906A2 |

| Устройство для сопряжения | 1979 |

|

SU896613A2 |

| Устройство для восстановления информации при сбоях в блоках ЦВМ | 1988 |

|

SU1689954A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Многокоординатная система числового программного управления | 1972 |

|

SU448435A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU930388A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

Даты

1970-01-01—Публикация