MsEeCTHo ноелбДовательйое Запоминающее устройство по авт. св. № 195214.

Предлагаемое устройство отличается тем, что оно содержит дешифратор, счетчик, схему установки начальных условий, реверсивный счетчик и схему управления им, входы которой подсоединены к выходам триггеров, а выходы подключены к управляющим входам реверсивного счетчика. Один из входов последнего соединен через схему установки начальных условий со счетчиком тактов, а выходы через дешифратор - со входами вентилей схемы хранения.

Это позволяет стабилизировать период рециркуляции при изменении температуры.

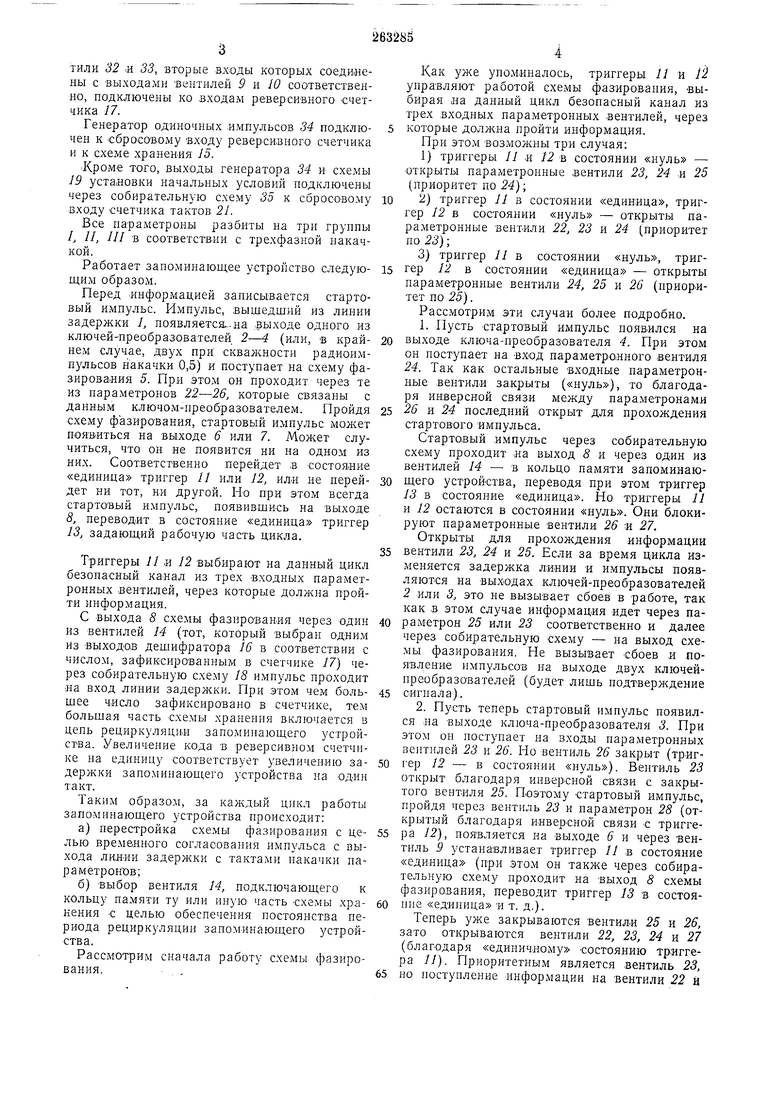

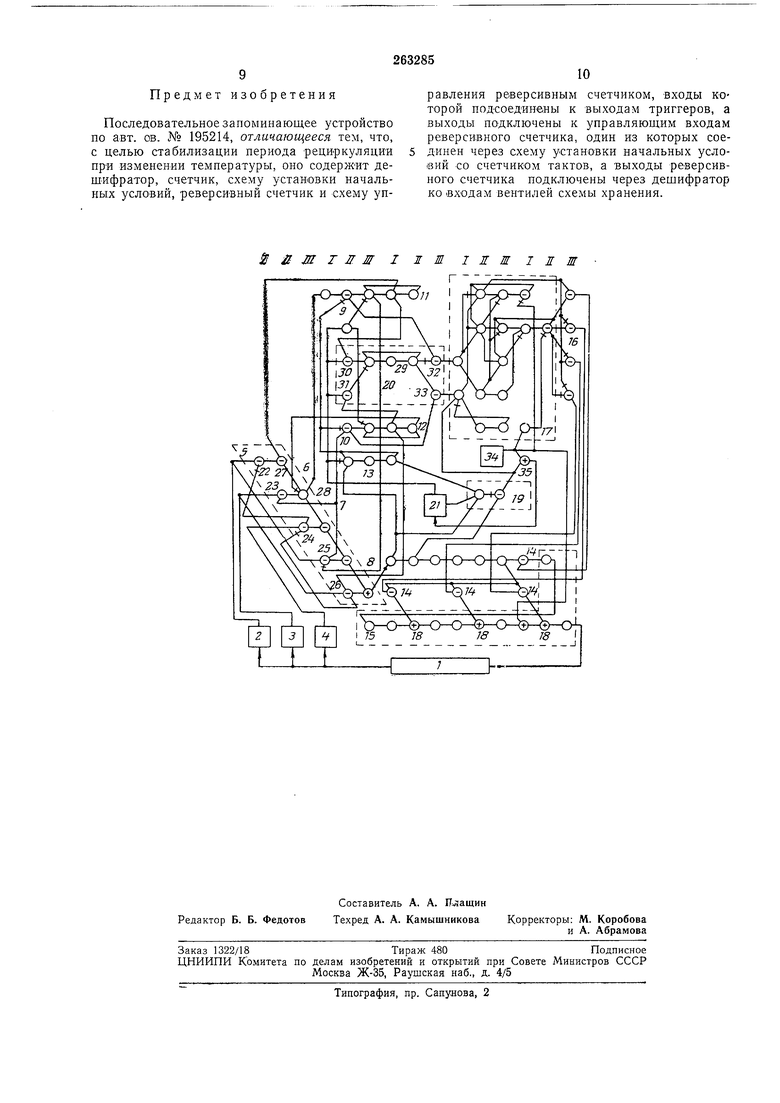

На чертеже представлена схема устройства.

Выход линии задержки / через ключи-преобразователи 2-4 соединен со схемой фазирования 5 с тремя выходами 6-S. Выходы 6 и 7 через вентили 9 и 10 соединены соответственно со входами триггеров 11 и 12, а выход 5 подсоединен к установочному входу триггера 13 рабочей части цикла и вентилям 14, управляющим подключением той или иной части схемы хранения 15. Вторые входы вентилей 14 соединены через дешифратор 16 с выходами триггеров реверсивного счетчика 17, а выходы через собирательные схемы :18- с параметронами схемы хранения 15. Входы реверсивного счетчика через схему 19 установки начальных условий И схему 20 ynpasления реверсированием подключены к выходам счетчика тактов 21, которые соединены также со сбросовыми входами триггеров 11-

13.

Схема фазирования 5 состоит из десяти параметров, пять из которых (22-26) являются входными параметронными вентилями, а пять других соединены последовательно между собой, причем каждый из них одновременна соединен с соответствующим входным параметронным вентилем. Кроме того, входы трех входных параметронных вентилей 22-24 соединены с выходами последних трех входных

параметронных вентилей 24-26 соответственно. Выходы триггеров 11 и 12 соединены соответственно со входам и параметров 27, 25 и 28, 26. Схема 19 установки начальных условий 1вынолнена в виде схемы антисовпадения, входы которой соединены с выходами схемы фазирования 5, счетчика тактов 21 и триггера 13 рабочей части цикла, а выход - со входом реверсивного счетчика 17.

Схема 20 управления реверсированием вы полнена в виде триггера 29, установочный и сбросовый входы которого через вентили 30 и 31, вторые входы которых подключены к выходам триггеров } и 12, соединены с выхотили 32 .и 33, вторые входы которых соединены с выходами вентилей 9 и 10 соответственно, подключены ко входам реверсивного счетчика 17. Генератор одиночных импульсов 34 подключен к сбросовому входу реверсивного счетчика и к схеме хранения J5. iKpOMe того, выходы генератора 34 и схемы J9 устааовкн начальных условий подключены через собирательную схему 35 к сбросовому входу счетчика тактов 21. Все нараметроны разбиты на три группы /, //, /// в соответствии с трехфазной накачкой. Работает запоминающее устройство следующим образом. Перед информацией записывается стартовый импульс. Импульс, вышедший из линии задержки 1, появляетса.,.на выходе одного из ключей-преобразователей 2-4 (илн, в крайнем случае, двух при скважности радиоимпульсов накачки 0,5) и поступает на схему фазирования 5. При этом он проходит через те из параметронов 22-26, которые связаны с данным ключом-преобразователем. Пройдя схему фазирования, стартовый импульс может Может ПОЯВИТЬСЯ на выходе 6 или 7. Может случиться, что он не появится ни на одном из них. Соответственно перейдет в состояние «единица триггер // или 12, или не нерейдет ни тот, ни другой. Но при этом всегда стартовый импульс, появившись на выходе 8, переводит в состояние «единица триггер 13, задающий рабочую часть цикла. Триггеры 11 и 12 выбирают на данный цикл безопасный канал из трех входных параметронных вентилей, через которые должна пройти информация. С выхода 8 схемы фазирования через один из вентилей 14 (тот, который выбран одним из выходов дешифратора 16 в соответствии с числом, зафиксированным в счетчике 17) через собирательную схему 18 импульс проходит на вход линии задержки. При этом чем большее число зафиксировано в счетчике, тем большая часть схемы хранения включается в цепь рециркуляции запоминающего устройства. Увеличение кода в реверсивном счетчике на единицу соответствует увеличению задержки запоминающего устройства на один такт. Таким образом, за каждый цикл работы запоминающего устройства происходит: а)перестройка схемы фазирования с целью временного согласования импульса с выхода линии задерл ки с тактами накачки параметронЪв;б)выбор вентиля 14, подключающего к кольцу памяти ту или иную часть схемы хранения с целью обеспечения постоянства периода рециркуляции запоминающего устройства. Как уже уном-иналось, триггеры 11 и Г правляют работой схемы фазирования, выбирая на данный цикл безопасный канал из рех входных параметронных вентилей, через которые должна пройти информация. При этом возможны три случая: 1)триггеры 11 ,и 12 в состоянии «нуль - открыты параметронные вентили 23, 24 ,и 25 (приоритет по 24); 2)триггер 11 в состоянии «единица, тригер 12 в состоянии «нуль - открыты параметронные вентили 22, 23 и 24 (приоритет по 23); 3} триггер 11 в состоянии «нуль, триггер 12 в состоянии «единица - открыты нараметронные вентили 24, 25 и 26 (приоритет по 25). Рассмотрим эти случаи более подробно. 1. Пусть стартовый импульс появился на выходе ключа-преобразователя 4. При этом он ноступает на вход параметронного вентиля 24. Так как остальные входные нараметронные вентили закрыты («нуль), то благодаря инверсной связи между параметронами 26 и 24 последний открыт для прохождения стартового импульса Стартовый .импульс через собирательную схему проходит на выход 8 и через один из вентилей 14 - в кольцо памяти запоминающего устройства, переводя при этом триггер 13 в состояние «единица. Но триггеры 11 и 12 остаются в состоянии «нуль. Они блокируют нараметронные вентили 26 и 27. Открыты для прохождения информации вентили 23, 24 и 25. Если за время цикла изменяется задержка линии и импульсы ноявляются на выходах ключей-преобразователей 2 или 3, это не вызывает сбоев в работе, так как в этом случае информация идет через параметрон 25 или 23 соответственно и далее через собирательную схему - на выход схемы фазирования. Не вызывает сбоев и появление импульсов на выходе двух ключейпреобразователей (будет лишь подтверждение сигнала). 2. Пусть теперь стартовый импульс появился на выходе ключа-преобразователя 3. При этом он поступает на входы параметронных вентилей 23 и 26. Но вентиль 26 закрыт (триггер 12 - в состоянии «нуль). Вентиль 23 открыт благодаря инверсной связи с закрытого вентиля 25. Поэтому стартовый импульс, пройдя через вентиль 23 и параметров 28 (открытый благодаря инверсной связи с триггера 12), появляется на выходе 6 и через вентиль 9 устанавливает триггер 11 в состояние «единица (при этом он также через собирательную схему проходит на выход 8 схемы фазирования, переводит триггер 13 в состояпие «единица и т. д.). Теперь уже закрываются вентил.и 25 и 26, зато открываются вентили 22, 23, 24 и 27 (благодаря «единичному состоянию триггера 11). Приоритетным является вентиль 23, но ноступление информации на вентили 22 и

24 также не вызывает сбоев, поскольку все они объединены собирательной схемой. Аналогичло не нарушает нормальной работы и поя:вленне импульсов на выходах двух ключей-преобразователей.

3. Стартовый импульс появляется па выходе ключа-преобразователя 2. При этом он поступает на входы параметронных вентилей 22 и 25. Оба вентиля открыты: вентиль 22- благодаря инверсной связи с закрытого вентиля 24, вентиль 25 - благодаря илверсной связи с триггера 11, находящегося в «нулевом состоянии. Стартовый импульс проходит через вентили 22 и 25, но в первом случае его дальнейшее прохождение блокирует закрытый вентиль 27, во втором он появляется на выходе 7 схемы фазирования и через вентиль 10 переводит триггер 12 в «единичное состояние.

При этом прохождение информации оазрешается только через вентили 24, 25 и 26. Через вентили 22 и 23 информация может пройти, но ее дальнейшее прохождение блокируют закрытые вентили 27 и 28 (первый - благодаря «нулевому состоянию триггера //, второй - благодаря «единичлому состоянию триггера 12). Приоритетным в данном случае является вентиль 25. Однако появление импульсов на входах вентилей 24 и 26 также не вызывает нарушений в хранящейся информации.

В случае появления импульсов иа выходах двух ключей-преобразователей опасность сбоя возникает лишь в том случае, когда рабочими являются крайние из входных параметрических вентилей (22 и 24, 23 и 25, 24 и 26). Во избежание сбоя один из этих вентилей блокируется другим.

стартовым импульсом и последующей информацией должен быть интервал минимум в два такта, необходимый для перестройки триггеров // и 12. После того как триггер 13 переходит в состояние «единица, он блокирует вентили 9 и 10. Таким образом, вся последующая информация не вызывает перестройки триггеров 11 и 12. После прохождения через схему фазирования последнего бита информации триггеры //, 12 и 13 сбрасываются в «нуль сигналом с одного из выходов счетчика тактов 2, непрерывно пересчитывающего тактовые импульсы. Емкость счетчика определяется длительностью задержки запоминающего устройства. С одного из двух его выходов импульс окончания рабочей части цикла поступает на сброс триггеров //, 12 и 13, с другого импульс переполнения поступает на вход схемы установки начальных условий.

В следующий цикл стартовый импульс снова появляется на выходе линии задержки, проходит схему фазирования и перестраивает триггеры 11 к 12 к т. л.

При пуске «нулевое состояние реверсивного счетчика 17 с соответствующего выхода дешифратора 16 открывает тот из вентилей 14, который подключает наименьшую часть схемы хранения. При этом время задержки запоминающего устройства меньше наперед заданного. Пусковой (стартовый) импульс с ге ератора одиночных импульсов 34 проходит в кольцо памяти и сбрасывает при этом счетчик

тактов 21, который начинает считать уже с «нуля. Так как врел1я задержки кольца памяти меньше заданного, стартовый импульс появляется на выходе 8 схемы фазирования раньше, чем импульс переполнения счетчика

тактов 21, и через схему 19 установки начальных условий проходит ня cyм иpyющий вход реверсивного счетчика (выходной вентиль схемы уста1ювки начальных условий открыт вследствие инверсной связи с нредыдущего

параметрона, находящегося в «нулевом состоянии благодаря «нулевому состоянию триггера 13 и отсутствию сигнала переполнения счетчика тактов). Число в реверсивном счетчике увеличивается на единицу, выбирается следующий выход дешифратора 16 и открывается уже другой из вентилей 14, подключающий к кольцу памяти еше часть схел1Ы хранения из трех параметронов, т. е. задержка запоминающего устройства увеличивается на один такт.

При этом импульс с выхода схемы установки начальных условий через собирательную схему 35 снова перестраивает счетчик тактов 21 на работу с «нуля.

Стартовый импульс снова, тенерь уже через другой вентиль 14, проходит в схему хранения, а затем через линию задержки - на схему фазирования (несколько нараметронов между выходом 8 схемы фазирования и входом вентилей 14 включены для задержки сигнала с выхода схемы фазирования на время пеоестройки реверсивного счетчика).

Если опять время задержки запоминающего устройства меньше заданного, еще один импульс добавляется в реверсивный счетчик 17, выбирается очередной выход дешифратора 16, к кольцу памяти добавляются еще три параметрона и т. д.

Наконец, стартовый импульс с выхода 8 схемы фазирования совпадает с импульсом переполнения счетчика тактов 21, и выход схемы установки начальных условий блокируется. В реверсивном счетчике фиксируется

код, выбирается соответствующий выход дешифратора 16 и через соответствующий вентиль 14 подключается часть схемы хранения таким образом, что время задержки запоминающего устройства становится равным наперед заданному, а именно - периоду работы счетчика тактов 21.

ся -с помощью схемы 20 управления реверсированием.

Работает схема следующим образом.

После появления с выхода счетчика тактов 21 .импульса окончания рабочей части цикла и сброса триггеров 11, 12 и 13 триггер 29 «запоминает на время паузы, какой из триггеров 11 и 12 находился во время носледнего цикла в состоянии «единица и соотв етственно управляет добавлением в счетчик импульса или его вычитанием.

Возможны соответственно три случая. Рассмотрим их подробнее.

1. Пусть в предыдущем цикле триггер // находился в состоянии «единица, а триггер 12 - в состоянии «нуль (понижение температуры). Импульс окончания рабочей части цикла через вентиль 30 взводит триггер 29 в состояние «единица. При этом открывается вентиль 5с.

Если в результате дальнейшего снижения температуры стартовый импульс появится на выходе 7 схемы фазирования, то через вентили 10 и 33 он нройдет на суммирующий вход реверсивного счетчика. Содержимое счетчика увеличится на единицу, ,и через соответствующий выход дешифратора 16 и вентиль 14 к кольцу памяти добавятся еще три параметрона, которые скомпенсируют «укорочение линии задержки.

2.Пусть в предыдущем цикле триггер // находился в состоянии «нуль, а триггер 12- в состоянии «единица (повышение температуры). Тогда импульс окончания рабочей части цикла через вентиль 31 устанавливает триггер 29 в «нулевое состояние. Соответственно подготавливается вентиль 32.

Если в результате дальнейшего повышения температуры стартовый импульс появится на выходе 6 схемы фазирования, то через вентили 9 32 оя пройдет на вычитающий .вход реверсивного счетчика 17. Содержимое счетчика уменьшится на единицу и соответственно из кольца памяти исключатся три параметрона.

3.Пусть в предыдущем цикле триггеры // и 12 находились в состоянии «нуль. Тогда вентили 30 и 31 будут закрыты, и состояние триггера 29 не изменится. Но оба вентиля 32 и 33 все равло будут заблокированы, так как закрыты вентили 9 и 10.

При повышении тел1пературы в первом из разобранного случая и понижении во втором схема управления реверсированием заблокирована (вентили 9 и 10 закрыты), и изменение линии задержки компенсируется самой схемой фазирования.

Количество разрядов реверсивного счетчика (и соответственно количество параметронов схемы хранения) определяется требуемым диапазоном изменения температуры (для примера на чертеже изображены два разряда реверсивного счетчика).

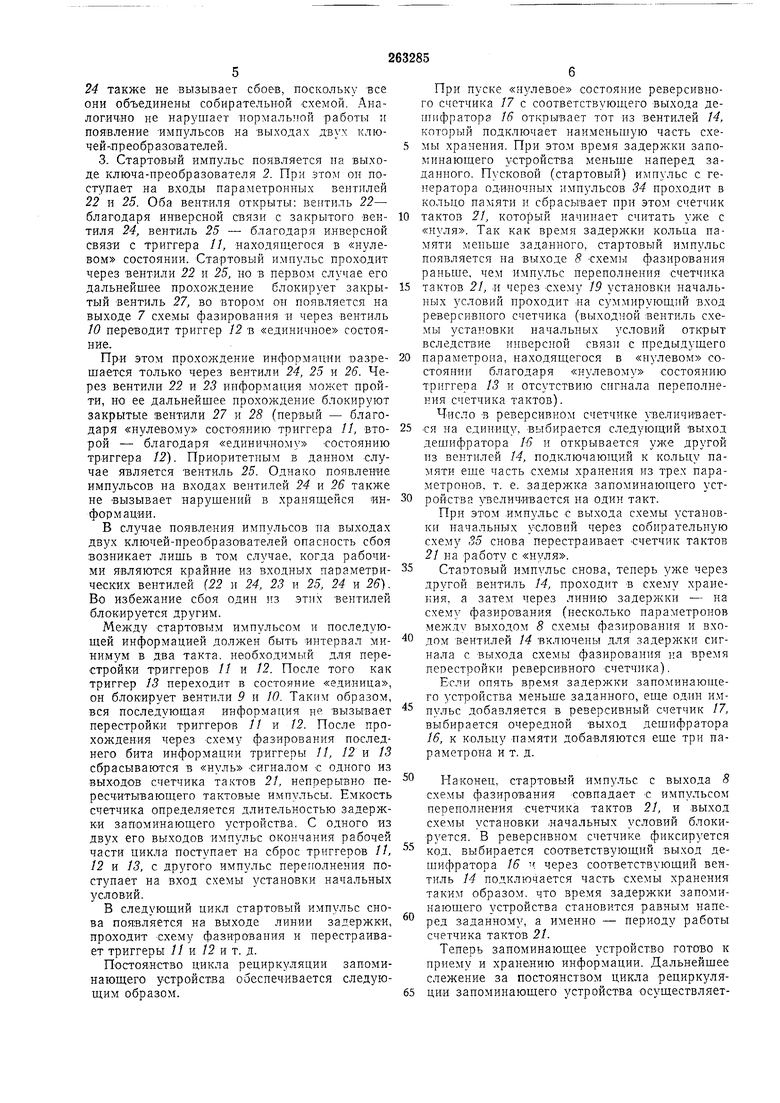

Количество параметронов п схемы хранения определяется из соотношения

--, зГсг - Тгг,

где Гсх - время прохождения сигнала через параметроны схемы хранения;а -температурный коэффициент расщирения линии; L -длина;

А/°С - заданный интервал температур; Т - длительность периода тактовых импульсов.

Так ка.к температура может измениться и в момент пуска, покажем, что работа схемы управления реверсированием не мещает установлению начальных условий.

В самом деле, так как триггер 29 может при включении находиться IB любом состоянии, то не исключено прохождение стартового импульса с выходов 5 и 7 схемы фазирования через вентили 9, 32 и 10, 33 соответственно на входы вычитания и сложения реверсивного счетчика.

В первом случае состояние реверсивного счетчика не изменяется, так как вслед за (ВЫчитанием импульса через схему установки начальных условий в реверсивный счетчик добавляется единица (время установления начальных условий увеличивается на один цикл, что не играет роли).

Во втором случае импульс добавляется в реверсивный счетчик. Второй импульс со схе.мы установки начальных условий блокируется задержкой сигнала с суммирующего входа реверсивного счетчика на один такт и возвратом его на этот суммирующий вход с инверсией.

Предлагаемое запоминающее устройство выполнено на магниевой линии задержки и е.мкостных параметронах. В качестве ключапреобразователя использован полупроводниковый диод, включенный в цепь связи между двумя параметронами, один из которых является эталонным. Нормально этот диод заперт и отпирается лишь импульсом с выхода линии задержки. Если амплитуда импульса с выхода линии задержки мала и не отпирает диода, и.мпульс предварительно усиливается (как и было в нашем случае).

На вход линии задержки поступает радиоимпульс непосредственно с параметрона схемы хранения (сложенный с эталонным).

Аналогичное запоминающее устройство может быть выполнено на любой линии задержки, а также на магнитном барабане и любых трехтактовых мажоритарных элементах.

Предлагаемое запоминающее устройство последовательного типа может найти щирокое применение в качестве оперативного запоминающего устройства в параметронных вычислительных мащинах.

Предмет изобретения

Последовательное запоминающее устройство но авт. св. № 195214, отличающееся тем, что, с целью стабил изации нериода рецнркуляциИ нри изменении температуры, оно содержит дешифратор, счетчик, схему установки начальных условий, реверсивный счетчик и схему унравления реверсивным счетчиком, входы которой нодсоединены к выходам триггеров, а выходы подключены к управляющим входам реверсивного счетчика, один из которых соединен через схему установки начальных условий со счетчиком тактов, а выходы реверсивного счетчика подключены через дешифратор ко входам вентилей схемы хранения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство задержки импульсных сигналов | 1981 |

|

SU945970A1 |

| УСТРОЙСТВО для РЕГИСТРАЦИИ ОРДИНАТ СЧИТЫВАЕМЫХ ГРАФИКОВ | 1968 |

|

SU220652A1 |

| Устройство управления групповой трикотажно-вязальных машин | 1971 |

|

SU501602A1 |

| КОРРЕЛЯТОР | 1973 |

|

SU374607A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕЙ ЧАСТОТЫ СЛУЧАЙНО РАСПРЕДЕЛЕННЫХ ИМПУЛЬСОВ | 1971 |

|

SU311281A1 |

| УСТРОЙСТВО для ВЫЧИСЛЕНИЯ ДИСПЕРСИИ СЛУЧАЙНОГОПРОЦЕССА | 1971 |

|

SU304584A1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ДВОИЧНО-п-ИЧНОГО КОДА | 1973 |

|

SU387360A1 |

| КОРРЕЛЯТОР | 1972 |

|

SU432510A1 |

| УСТРОЙСТВО ДЛЯ ИНДИКАЦИИ | 1973 |

|

SU386393A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМИ ДВИГАТЕЛЯМИ | 1972 |

|

SU330433A1 |

Даты

1970-01-01—Публикация