Изобретение относится к области запоминающих устройств.

Известно запоминающее устройство (ЗУ), содержащее магнитный накопитель с К-мерной выборкой, К дещифраторов, в котором кодовые щины адреса разделены на группы. При кодовые шины младших разрядов счетчика или регистра соединены со входами дешифратора А , а кодовые шины старших разрядов - со входами дешифратора У. При обращении к ячейке памяти открываются два ключа по шине X и по шине У.

Недостатком таких устройств является неравномерное использование координатных (адресных) ключей при обработке информации, размещенной в ячейках массива, адреса которых отличаются на постоянную величину (например на единицу младшего разряда).

Известно также, что при использовании ЗУ для хранения команд и тем более при обработке информации, сгруппированной в массивы, большой процент выборов (70%) осуществляется из последовательно размещенных (по адресам) ячеек.

Целью изобретения является повышение надежности, быстродействия и уменьшение габаритов адресной части ЗУ. Это достигается тем, что кодовые шины, соединяющие счетчик или регистр с дешифраторами, разбиваются на группы, каждая из которых содержит К соседних шин сменных разрядов, а шины первой группы соединяются с первыми входами всех дешифраторов, шины второй группы - со вторыми входами всех дешифраторов и т. д.

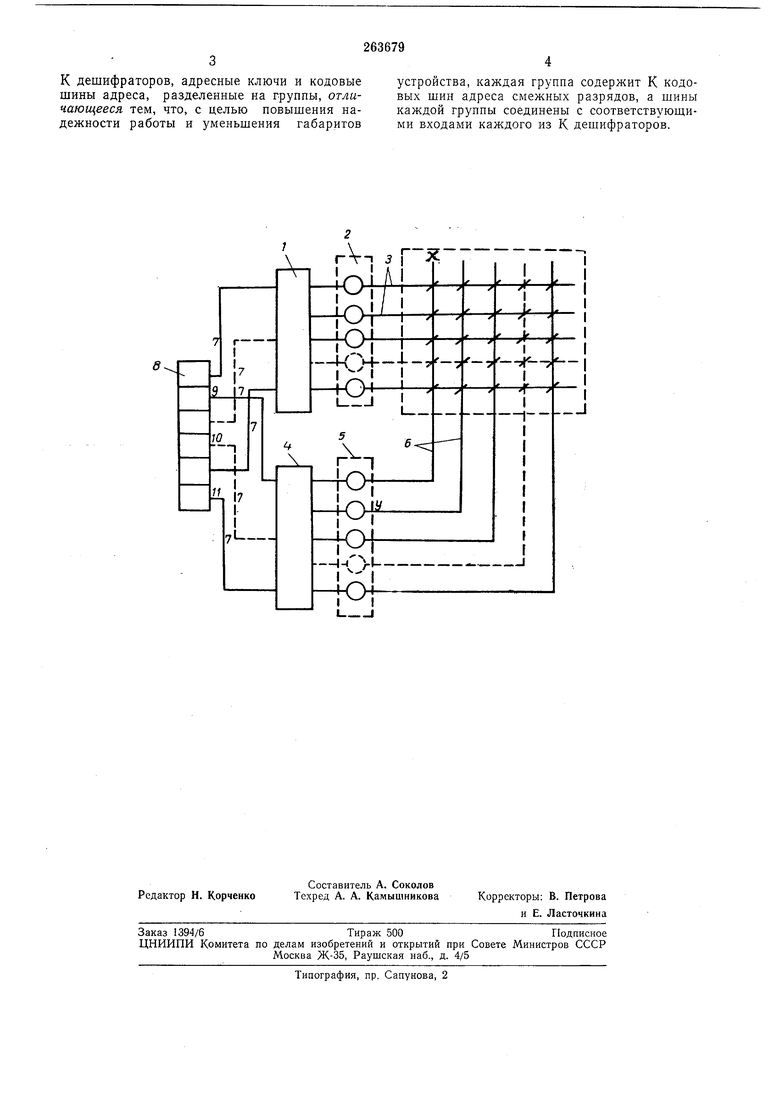

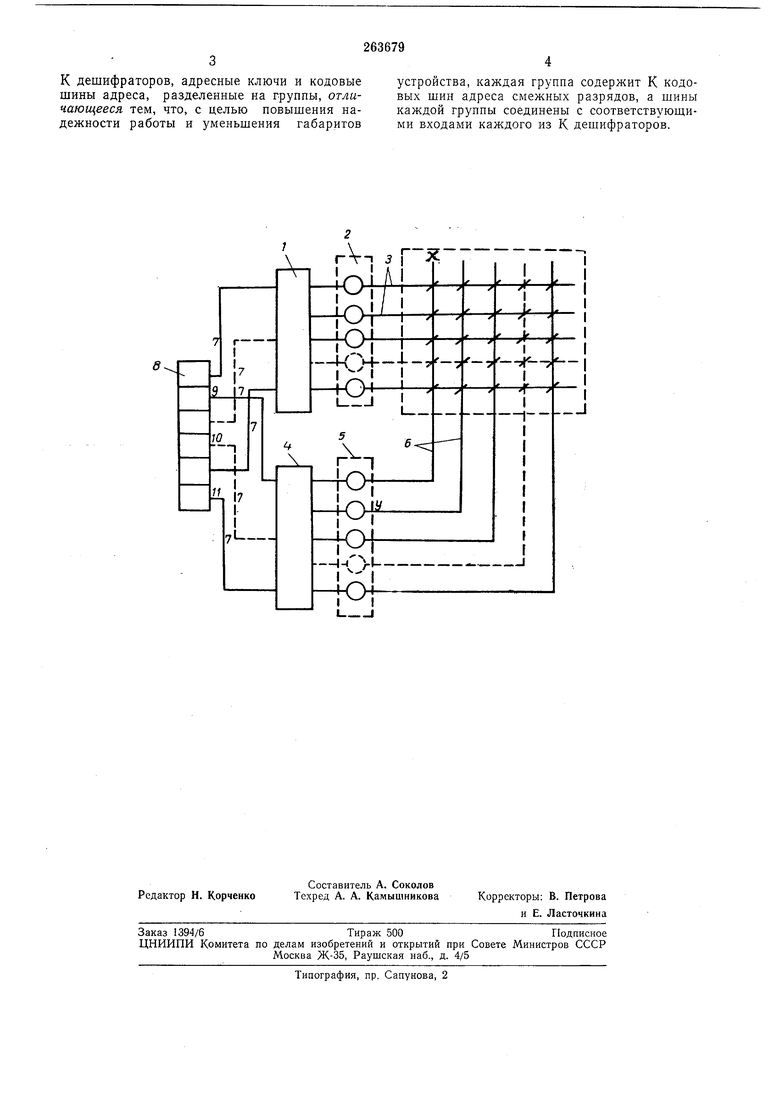

На чертеже показана блок-схема адресной части ЗУ с двухмерной выборкой.

Она содержит дешифратор X 1, выходы которого соединены со входами адресных клю,чей X 2, причем каждый из них переключает

адресный ток в шинах X 3 магнитного накопителя. Выходы дешифратора У 4 соединены с адресными ключами У 5, переключающими адресный ток в шипах У 6 магнитного накопителя. Кодовые шины 7 с регистра адреса 8

разбиты на группы 9-11 но 2() и подсоединены ко входам дешифраторов 1 у( 4.

Шина первого разряда первой группы 9 кода адреса соединена с первым входом дешифратора }, шина второго разряда группы 9 -

с первым входом дешифратора 4. Шина первого разряда второй группы 10 соединена со вторым входом дешифратора /, шина второго разряда - со вторым входом дешифратора 4 и т. д. Такое соединение обеспечивает уменьшение частоты обращения к каждому адресному ключу.

Предмет изобретения

К дешифраторов, адресные ключи и кодовые шины адреса, разделенные на группы, отличающееся тем, что, с целью повышения надежности работы и уменьшения габаритов

устройства, каждая группа содержит К кодовых шин адреса смежных разрядов, а шины каждой группы соединены с соответствуюшими входами каждого из К дешифраторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ МАГПИТНЫМ НАКОПИТЕЛЕМ | 1970 |

|

SU265952A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| Многоканальный измеритель временных интервалов | 1981 |

|

SU970306A1 |

| Устройство для связи процессора с запоминающим устройством | 1983 |

|

SU1083196A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

Даты

1970-01-01—Публикация