Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении быстродействующих ЗУ из блоков памяти, не обладающих достаточным быстродействием, с сохранением функциональных возможностей ЗУ с произвольной выборкой.

Известны ОЗУ [1, 2], содержащие накопители, логические компоненты, элементы управления и позволяющие повысить быстродействие (уменьшить цикл обращения) за счет расслоения памяти. Недостатком ОЗУ является невозможность их использования в качестве полноценного ОЗУ с произвольным доступом, быстродействие которого одинаково как в режиме записи, так и в режиме чтения.

Наиболее близким по техническим признакам к предлагаемому является ЗУ [3] , содержащее два блока памяти, регистры адреса и числа, счетчик адреса, триггер, коммутаторы.

Так как цикл записи или считывания определяется работой одного блока памяти, а при считывании адрес определяется счетчиком адреса, то, следоовательно, известному ЗУ свойственны следующие недостатки: невозможность реализации с быстродействием, превосходящим возможности блоков памяти, невозможность считывания по произвольно выбранному адресу и, следовательно, невозможность использования как ЗУ с произвольной выборкой.

Целью изобретения является повышение быстродействия за счет уменьшения цикла обращения с одновременным обеспечением произвольности доступа к ЗУ.

Сущность изобретения заключается в организации структуры памяти в виде матрицы накопителей, причем запись слова производится параллельно по одному и тому же адресу в два накопителя одной строки матрицы с чередованием во времени по строкам матрицы моментов записи слова при одновременной фиксации в дополнительной одноразрядной памяти признака поступления информации, а считывание производится по тому же адресу параллельно из двух накопителей одного и того же столбца матрицы с чередованием во времени по столбцам моментов выдачи слова при одновременном анализе зафиксированного признака поступления информации для того, чтобы на выход ЗУ выдать информационный код с того накопителя, к которому производилось последнее по времени обращение при записи. При этом одновременно обеспечиваются сокращение в 2 раза цикла обращения по всему ЗУ по сравнению с периодом обращения к каждому из накопителей, входящих в его состав, и возможность записи и чтения по произвольно выбранному адресу.

Для достижения цели в ЗУ, содержащее накопитель, регистр числа, блок управления и коммутатор, введены три накопителя, четыре фиксатора записи, второй регистр числа, блок приоритета. Информационные входы нечетных и четных накопителей соответственно объединены и соединены с выходами первого и второго регистров, входы которых объединены. Выходы нечетных и четных накопителей соответственно объединены и соединены с первым и вторым информационными входами коммутатора, выход которого является выходом устройства, а управляющие входы соединены с выхоодами блока приоритета, входы которого соединены с информационными выходами фиксаторов записи. Адресные входы последних объединены с адресными входами накопителей. Вторые адресные входы предшествующих фиксаторов записи соединены с адресными выходами последующих фиксаторов записи. Входы синхронизации регистров числа, входы выборки накопителей, первые и вторые входы выборки фиксаторов записи соединены с выходами четырех групп блока управления, выходы разрешения установки, адреса установки, режима, а также выходы пятой группы которого соединены соответственно с одноименными входами, а также информационными входами фиксаторов записи.

Каждый из накопителей содержит блок памяти и регистр адреса, выход которого и вход синхронизации соединены соответственно с входом адреса и входом выборки блока памяти, остальные входы и выход которого являются одноименными входами и выходом накопителя.

Фиксатор записи содержит адресный коммутатор, элемент НЕ, два одноразрядных накопителя, выходы, режимные и информационные входы которых соответственно объединены. Адресный коммутатор имеет четыре направления коммутации. Первые входы по направлениям коммутации с первого по четвертое соединены с входом адреса установки, первым адресным входом, первым и вторым информационными входами фиксатора записи. Вторые входы по направлениям коммутации с первого по четвертое соединены с входом разрешения установки фиксатора записи, с выходом элемента НЕ, с входом режима фиксатора записи. Третьи входы по третьему и четвертому направлениям коммутации соединены с первым и вторым адресными входами фиксатора записи, вход режима которого соединен с входом элемента НЕ и входами режима одноразрядных накопителей, входы выборки которых соединены с первым и вторым входами выборки фиксатора записи. Адресные входы и входы информации одноразрядных накопителей соединены соответственно с выходом адресного коммутатора и с первым информационным входом фиксатора записи, информационным и адресным выходами которого являются соответственно выход одноразрядных накопителей и выход регистра одного из одноразрядных накопителей.

Блок управления содержит генератор, элемент И-ИЛИ, счетчик выборки, дешифратор, три группы элементов И, счетчик адреса, два элемента ИЛИ, элемент задержки, триггер, одновибратор, формирователь установки, коммутатор запрета, три коммутатора выборки. Выходы групп с первой по пятую блока управления соединены соответственно с выходами элементов И первой группы, коммутаторов выборки с первого по третий, элементов И второй группы. Выходы адреса установки и разрешения установки, а также режима блока управления соединены с выходами младших и старшего разрядов счетчика адреса, а также с выходом первого элемента ИЛИ. Вход режима блока управления соединен с входом управления первого коммутатора выборки, входом запуска одновибратора и через элемент задержки с входом первого элемента ИЛИ. Выход выборки блока управления, выход генератора и первый выход одновибратора соединены с одними входами элемента И-ИЛИ, с другими входами и выходом которого соединены парафазный выход счетчика адреса и счетный вход счетчика выборки. Выходы последнего соединены с входами дешифратора, первыми входами элементов И первой и второй групп, а также с входом второго элемента ИЛИ и счетным входом триггера, парафазный выход которого соединен с первыми входами других элементов И второй группы. Вход установки счетчика выборки соединен с выходом формирователя установки и одноименными входами триггера и счетчика адреса, парафазный выход старшего разряда которого соединен с вторым входом первого и второго элементов ИЛИ, а также с вторыми входами элементов И первой группы и входом разрешения одновибратора. Выходы одновибратора соединены с входами управления коммутатора запрета, входы и выходы которого соединены соответственно с выходами дешифратора и первыми входами элементов И третьей группы. Выходы элементов И первой группы соединены с входами групп первого, второго и третьего коммутаторов выборки, а также с вторыми входами элементов И третьей группы, выходы которых соединены с входами других групп второго и третьего коммутаторов выборки.

Блок приоритета содержит элементы НЕ и И-ИЛИ. Входы элементов НЕ и выходы элементов И-ИЛИ являются соответственно входами и выходами блока приоритета. Выходы элементов НЕ соединены с четными входами первого и нечетными входами второго элементов И-ИЛИ, входы элементов НЕ соединены с нечетными входами первого и четными входами второго элементов И-ИЛИ.

При исследовании патентной и научно-технической информации не были обнаружены источники, в которых были бы приведены сведения о технических решениях, содержащих совокупность отличительных признаков предлагаемого ЗУ. Хотя известны технические решения, содержащие отдельные отличительные признаки, однако свойства и эффект, которые эти признаки сообщают известным объектом, иные, чем в изобретении, где в соответствии с целью они обеспечивают повышение быстродействия в режимах и записи, и считывания с одновременным сохранением произвольности доступа к памяти.

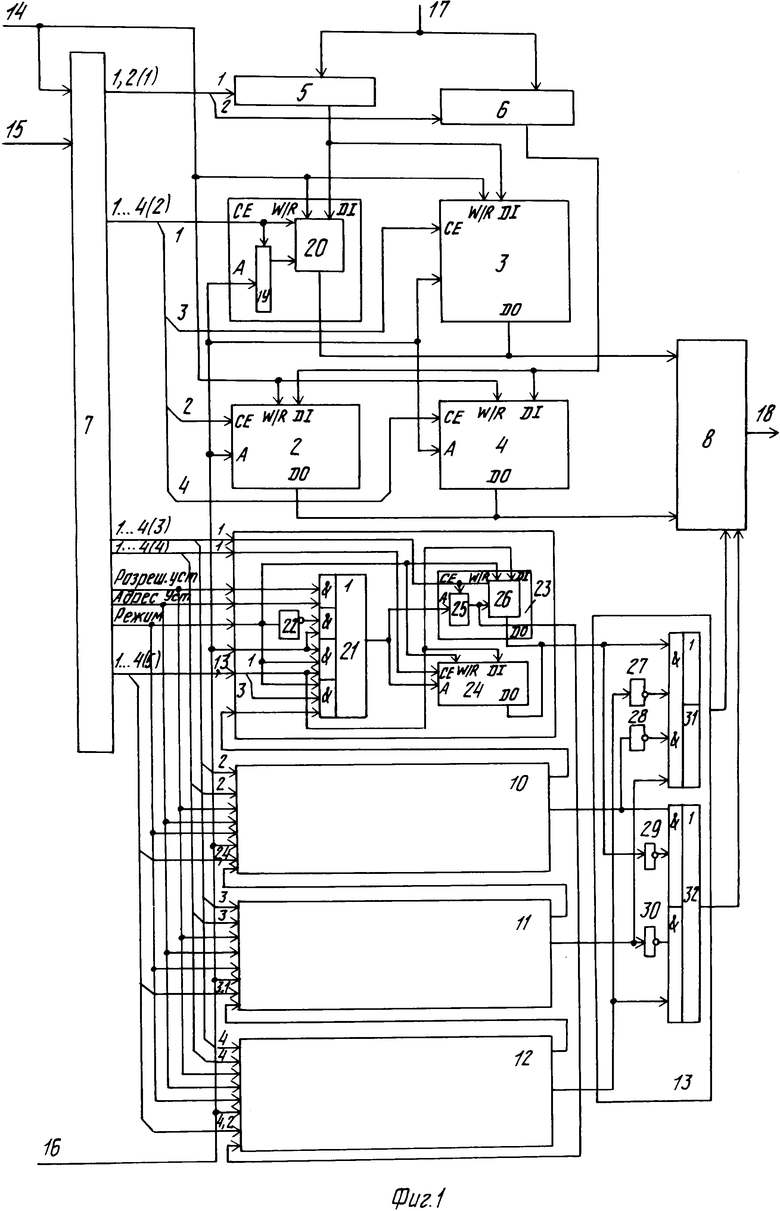

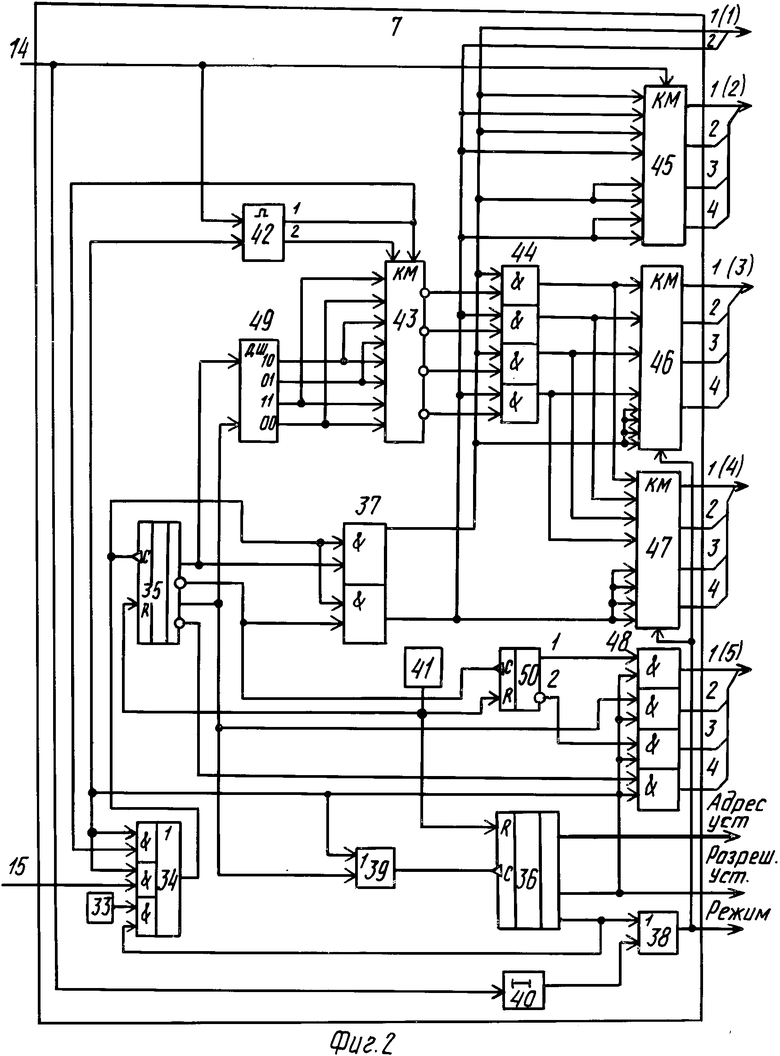

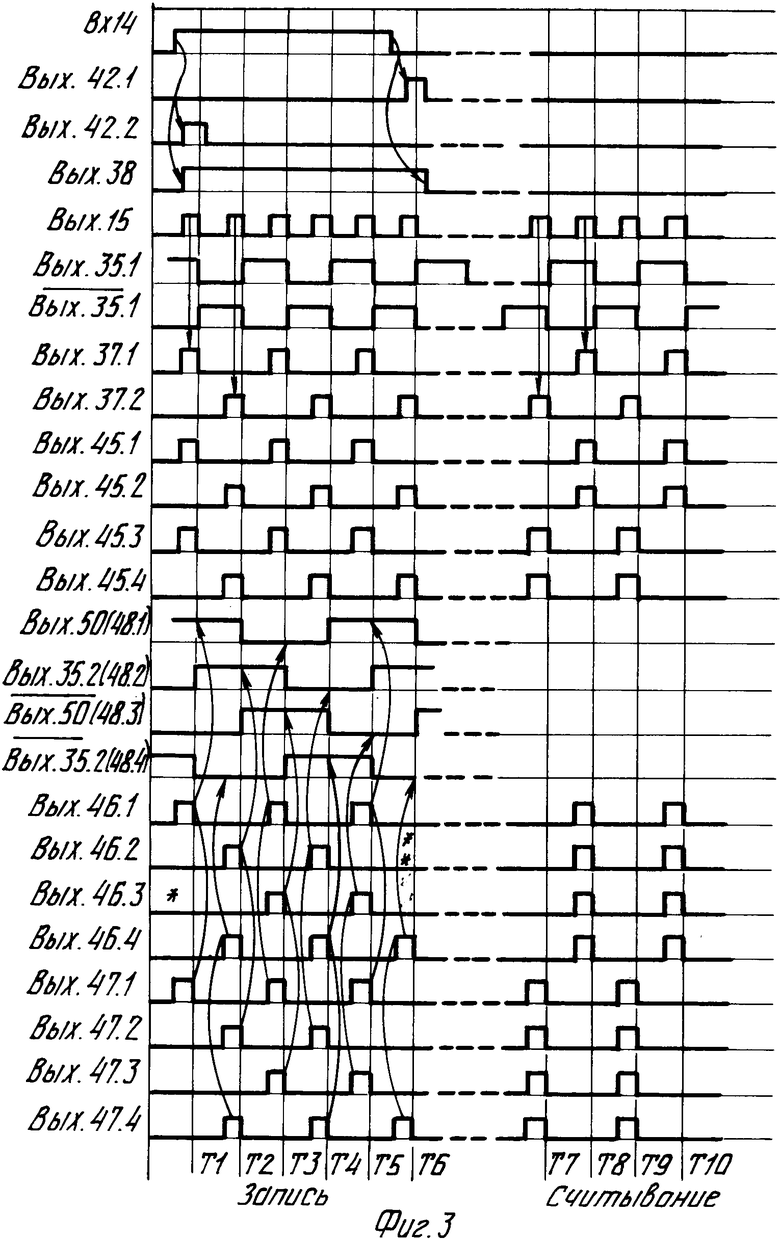

На фиг. 1 представлена блок-схема ЗУ; на фиг. 2 - блок-схема блока управления; на фиг. 3 - временная диаграмма работы в режимах записи и считывания.

ЗУ (фиг. 1) содержит накопители 1...4, регистры 5, 6 числа, блок 7 управления, коммутатор 8, фиксаторы 9...12 записи, блок 13 приоритета.

Вход 14 режима соединен с одноименными входами блока 7 управления и накопителей 1...4. Вход 15 выборки соединен с входом выборки блока 7 управления. Вход 16 адреса соединен с адресными входами накопителей 1...4 и фиксаторов 9. ..12 записи. Информационный вход 17 и выход 18 соединены соответственно с информационными входами регистров 5, 6 числа и выходом коммутатора 8.

Выхооды групп с первой по пятую (номера групп на фиг. 1, 2 помещены в скобках) блока 7 управления соединены соответственно с входами синхронизации регистров 5, 6 числа, входами выборки накопителей 1...4, первыми, вторыми входами выборки и первыми информационными входами фиксаторов 9, 10, 11, 12, вторые информационные входы которых соединены с первыми информационными входами фиксаторов 11, 12, 9, 10 записи. Выходы разрешения установки, адреса установки, режима блока 7 управления соединены с одноименными входами фиксаторов 9...12 записи, информационные выходы которых соединены с входами блока 13 приоритета. Адресные выходы фиксаторов 9, 10, 11, 12 записи соединены с вторыми адресными входами фиксаторов 12, 9, 10, 11 записи.

Информационные входы и выходы накопителей 1, 2 и 3, 4 соответственно объединены, входы соединены с выходами регистров 5 и 6 числа, а выходы - с входами коммутатора 8, управляющие входы которого соединены с выходами блока 13 приоритета.

Каждый из накопителей 1...4 содержит регистр 19 адреса и блок 20 памяти. Информационный вход регистра 19 адреса является входом адреса накопителя (1. . . 4), остальные входы и выход которого соединены с одноименными входами и выходами блока 20 памяти. Выход и синхровход регистра 19 адреса соединены соответственно с адресным входом и входом выборки накопителя (1.. .4).

Каждый из фиксаторов 9...12 записи состоит из адресного коммутатора 21, элемента НЕ 22, одноразрядных накопителей 23, 24, содержащих регистр 25 адреса и одноразрядный блок 26 памяти. Режимные, адресные, информационные входы и выходы одноразрядных накопителей 23, 24 соответственно объединены. Одноразрядные накопители 23, 24 аналогичны по построению накопителям 1...4. Выходы одноразрядных накопителей 23, 24 и выход регистра 25 адреса являются соответственно информационным и адресным выходом фиксатора (9...12) записи. Входы выборки одноразрядных накопителей 23, 24 являются первым и вторым входами выборки фиксаторов 9...12 записи. Адресные входы одноразрядных накопителей 23, 24 соединены с выходом адресного коммутатора 21, имеющего четыре направления коммутации. Первые входы адресного коммутатора 21 по направлениям 1. ..4 соединены с входом адреса установки, первым входом адреса, первым и вторым информационными входами фиксатора (9...12) записи. Вторые входы адресного коммутатора 21 по направлениям 1...4 соединены с входом разрешения установки, выходом и входом элемента НЕ 22, входом режима фиксатора (9. . .12) записи. Третьи входы коммутатора 21 по направлениям 3, 4 соединены с первым и вторым адресными входами фиксатора (9...12) записи. Вход элемента НЕ 22 соединен с входом режима одноразрядных накопителей 23, 24 и входом режима фиксатора (9...12) записи. Первый вход по направлению 3 коммутации адресного коммутатора 21 соединен с информационными входами одноразрядных накопителей 23, 24.

Блок 13 приоритета содержит элементы НЕ 27...30 и элементы И-ИЛИ 31, 32. Входы элементов НЕ 27...30 являются входами блока 13 приоритета и соединены с первым, третьим входами элемента И-ИЛИ 31 и вторым, четвертым входами элементы И-ИЛИ 32. Выходы элементов НЕ 27...30 соединены с вторым, четвертым входами элемента И-ИЛИ 31 и первым, третьим входами элементами И-ИЛИ 32. Выходы элементов И-ИЛИ 31, 32 являются выходами блока 13 приоритета.

Блок 7 управления (фиг. 2) содержит генератор 33 импульсов, элемент И-ИЛИ 34, счетчик 35 выборки, счетчик 36 адреса, группу элементов И 37, элементы ИЛИ 38, 39, элемент 40 задержки, формирователь 41 установки, одновибратор 42, коммутатор 43 запрета, группу элементов И 44, коммутаторы 45, 46, 47 выборки, группу элементов И 48, дешифратор 49, триггер 50.

Выходы групп с первой по пятую блока 7 управления соединены с выходами элементов И 37, коммутаторов 45, 46, 47 выборки, элементов И 48. Выходы адреса установки и разрешения установки, а также режима блока 7 управления соединены соответственно с выходами младших и старшего разрядов счетчика 36 адреса, а также с выходом элемента ИЛИ 38, соединенным с входами управления коммутаторов 46, 47 выборки. Первый (второй) выход элементов И 37 соединен с нечетными (четными) входами первой и нечетной (четной) парой входов второй групп коммутатора 45 выборки, с первыми входами нечетных (четных) элементов И 44, с входами второй группы коммутатора 46 (47) выборки. Выходы элементов И 44 соединены с входами первых групп коммутаторов 46, 47 выборки, а их вторые входы - с выходами коммутатора 43 запрета, входы второй группы которого соединены с выходами дешифратора 49, а нечетная и четная пары входов первой группы соединены соответственно с четной и нечетной парами входов второй группы. Входы управления коммутатора 43 запрета соединены с выходами одновибратора 42, первый выход которого соединен с первым входом элемента И-ИЛИ 34, а вход запуска - с входомо управления коммутатора 45 выборки, входом элемента 40 задержки и входом режима блока 7 управления. Вход разрешения одновибратора 42 соединен с первым и вторым разрешающими входами элемента И-ИЛИ 34, входом элемента ИЛИ 39, входами элементов И 48, выходом старшего разряда счетчика 36 адреса, инверсный выход которого соединен с входом элемента ИЛИ 38 и третьим разрешающим входом элемента И-ИЛИ 34, второй и третий входы которого соединены с входом выборки блока 7 управления и выходом генератора 33. Выход элемента 40 задержки соединен с входом элемента ИЛИ 38. Выход элемента И-ИЛИ 34 соединен со счетным входом счетчика 35 выборки и входами элементов И 37. Выход формирователя 41 установки соединен с установочными входами счетчиков выборки 35 и адреса 36, а также триггера 50. Прямой и инверсный выходы первого разряда счетчика 35 выборки соединены с вторыми входами элементов И 37, а также с первым входом дешифратора 49 и счетным входом триггера 50, прямой и инверсный выходы которого соединены с вторыми входами нечетных элементов И 48. Вторые входы четных элементов И 48 соединены с прямым и инверсным выходами второго разряда счетчика 35 выборки, а также с вторыми входами дешифратора 49 и элемента ИЛИ 39, выход которого соединен со счетным входом счетчика 36 адреса.

Работает ЗУ следующим образом.

При включении питания производится обнуление одноразрядных накопителей 23, 24 фиксаторов 9...12 записи. По перепаду на шине питания формирователь 41 установки устанавливает в исходное состояние счетчик 35 выборки, счетчик 36 адреса, триггер 50. Уровень "0" на выходе старшего разряда счетчика 36 адреса удерживает выходы элементов И 48 в состоянии логического "0", поступающего на информационные входы одноразрядных накопителей 23, 24, а также обеспечивает прохождение импульсов генератора 33 через элемент И-ИЛИ 34 на счетчик 35 выборки и прохождение сигналов через элемент ИЛИ 39 на счетчик 36 адреса. Последний осуществляет перебор адресов на входах адреса установки фиксаторов 9...12 записи. Коды адреса поступают через адресные коммутаторы 21 этих фиксаторов на адресные входы одноразрядных накопителей 23, 24 по сигналу разрешения установки с выхода старшего разряда счетчика 36 адреса. Остальные направления адресных коммутаторов 21 запрещены уровнем "0" с выхода элементов И 48 и с выхода элементов НЕ 22. Одноразрядные накопители 23, 24 находятся в режиме записи благодаря сигналу, поступающему на их вход режима с выхода элемента ИЛИ 38. Одновременно на их входы выборки поступают сигналы с выходов коммутаторов 46, 47. Эти сигналы вырабатываются элементами И 37 с помощью счетчика 35 выборки и проходят на входы первых групп коммутаторов 46, 47 выборки через элементы И 44, открытые благодаря высокому уровню на выходах коммутатора 43 запрета, установленному из-за отсутствия сигнала с выходов одновибратора 42. Таким образом производится запись "0" во все одноразрядные накопители 23, 24.

По окончании перебора адресов устанавливается в "1" старший разряд счетчика 36 адреса, сигнал с парафазного выхода которого запрещает работу счетчиков выборки 35 и адреса 36 от генератора 33 и разрешает формирование сигналов режима на выходе элемента ИЛИ 38, работу одновибратора 42, формирование информационных сигналов на выходах элементов И 48, прохождение сигналов выборки с входа 15 и сигнала с первого выхода одновибратора 42 через элемент И-ИЛИ 34. Устройство готово к работе.

В режиме записи производится занесение поступающей информации попеременно в накопители 1, 3 и 2, 4, благодаря чему сокращается цикл записи, так как импульсы выборки на входе 15 могут следовать с частотой, в 2 раза превышающей доопустимую частоту выборки каждого из накопителей. Одновременно с этим осуществляется попеременная запись в одноразрядные накопители 23, 24 нечетных (9, 11) и четных (10, 12) фиксаторов записи. При этом по текущему адресу в одноразрядные накопители 23, 24 одних фиксаторов записи записывается "1" и одновременно по предшествующему адресу (адресу информации, записанной в накопители 1, 3 или 2, 4 в предшествующем такте) в одноразрядные накопители 23, 24 других фиксаторов записи заносится "0". Благодаря этому в фиксаторах 9. . .12 записи фиксируется (но с опозданием на такт) месторасположение "свежей" информации в виде "1" и "устаревшей" в виде "0", записанных в накопителях 23, 24.

Для осуществления записи на вход 14 режима (фиг. 3, момент Т1) подают высокий потенциал, на выходы 17 и 16 - соответственно информационный и адресный коды. На вход 15 поступают импульсы выборки с периодом, меньшим времени записи накопителей 1...4 (но не более чем в 2 раза). На первом выходе счетчика 35 выборки частота этих импульсов уменьшается вдвое, и с выходов элементов И 37, где они стробируются сигналами выборки, импульсы попеременно поступают на входы синхронизации регистров 5 и 6 числа, а через входы первой группы коммутатора 45 выборки на входы выборки накопителей 1, 3 и 2, 4. Производится запись информационного кода в регистры 5 и 6 числа и адресного кода в регистры 19 адреса накопителей 1...4.

В связи с тем, что импульсы выборки должны поступать одновременно на два фиксатора записи (9 и 11, 10 и 12), причем в одноразрядные накопители 23, 24 одного из фиксаторов записывается "0", необходимо в начале цикла записи исключить запись "0" в фиксатор записи, не соответствующий тому из накопителей 1. ..4, в котором происходит запоминание входной информации. При отсутствии подобного запрета записываемый в одноразрядные накопители 23, 24 "0" может исказить признак "свежей" информации ("1"), хранившийся в них с предшествовавшего цикла записи. Поэтому по перепаду на входе 14 режима одновибратор 42 формирует на своем втором выходе импульс (вых. 42.2 на фиг. 3), разрешающий прохождение унитарного кода через коммутатор 43 запрета с выхода дешифратора 39. Этот код определяет номер того из фиксаторов 9...12, в одноразрядные накопители 23, 24 которого не следует записывать "0", и блокирует с помощью элементов И 44 прохождение импульса выборки на соответствующие выходы коммутаторов 46, 47 выборки (момент блокирования импульса выборки отмечен на фиг. 3 знаком *).

По импульсам выборки, поступающим с выходов коммутатора 45 выборки, производится запись одинакового кода в накопители 1 и 3 или 2 и 4 (т.е. запись по "горизонтали"), причем времени между двумя последовательными импульсами выборки, поступающими на накопители 1...4, достаточно для осуществления записи.

В связи с тем, что в накопителях 1, 3 и 2, 4 по одним и тем же адресам может быть записана разная информация: "свежая" и "устаревшая", в фиксаторах 9...12 записи, соответствующих накопителям 1...4, запоминаются признаки "свежей" и "устаревшей" информации в виде записи "1" и "0", формируемых на выходах элементов И 48 с помощью сигналов с выходов счетчика 35 выборки и триггера 50. Поэтому одновременно с записью информации в накопители 1, 3 производится запись "1" по текущему адресу в одноразрядные накопители 23, 24 фиксатора 9 записи и запись "0" в накопители 23, 24 фиксатора 11 записи по предшествующему адресу, зафиксированному в предыдущем такте в регистре 25 адреса одноразрядного накопителя 23 фиксатора 12 записи (момент Т5, фиг. 3). Текущий адрес поступает с входа 16 в регистры 25 адреса накопителей 23, 24 фиксатора 9 записи по третьему направлению коммутации адресного коммутатора 21, которое открыто сигналом режима с выхода элемента ИЛИ 38 и уровнем "1" с первого выхода группы блока 7 управления (вых. 50 (48.1), фиг. 3). Предшествующий адрес поступает из фиксатора 12 записи в регистры 25 адреса накопителей 23, 24 фиксатора 11 записи по четвертому направлению коммутации адресного коммутатора 21, которое открыто теми же сигналами. Таким образом, в одноразрядных накопителях 23, 24 фиксатора 9 записи запоминается (в виде "1") признак того, что в накопителях 1, 3 по текущему адресу записана "свежая" информация, а в одноразрядных накопителях 23, 24 фиксатора 11 записи запоминается (в виде "0") признак того, что информация, записанная в накопителе 4 по предшествующему адресу, "устарела".

По последующему импульсу выборки (момент Т3, фиг. 3), поступающему на накопители 1, 3 (т.е. через один импульс входной последовательности), текущий адрес с входа 16 проходит через адресный коммутатор 21 фиксатора 11 записи, а предшествующий адрес с адресного выхода фиксатора 10 записи - через адресный коммутатор 21 фиксатора 9 записи. Одноразрядные накопители 23, 24 фиксатора 11 записи хранят "1", а одноразрядные накопители 23, 24 фиксатора 9 записи хранят "0", свидетельствующий о том, что информация, записанная в накопителе 2 по предшествующему адресу, "устарела".

Аналогично происходит запись "1" и "0" по текущему и предшествующему адресам в одноразрядные накопители 23, 24 фиксаторов 10, 12 записи (моменты Т2, Т4, фиг. 3).

Сигналы выборки, по которым производится запись в накопители 23, 24 фиксаторов 9. ..12, формируются на выходах коммутаторов 46, 47 выборки (вых. 46.1...46.4, 47.1...47.4 на фиг. 3, моменты записи "1" и "0" показаны стрелками).

Таким образом, для полного соответствия информации, записываемой в накопители 1. ..4, и признаков "свежей" и "устаревшей" информации, записываемых в одноразрядные накопители 23, 24, необходимо иметь по окончании цикла записи дополнительный импульс выборки для фиксации "0" по предшествующему адресу и продлить цикл записи для фиксаторов записи на один такт. При этом, естественно, запись информации в накопители 1...4 и занесение "1" по текущему адресу в соответствующие фиксаторы 9...12 записи производиться не должна.

При переключении сигнала режима на входе 14 одновибратор 42 (фиг. 3, момент Т6, вых. 42.1) вырабатывает сигнал, имитирующий импульс выборки, поступающий на вход управления коммутатора 43 запрета и через элемент И-ИЛИ 34 на счетный вход счетчика 35 выборки. Задний фронт сигнала режима задерживается элементом 40 задержки, обеспечивая продление цикла записи для фиксаторов записи.

Состояние выходов счетчика 35 выборки, определяющее номер накопителя и фиксатора записи, в которые заносится информация и "1" по текущему адресу, дешифруется дешифратором 49 и с помощью коммутатора 43 запрета, на выход которого передаются уровни с входов его первой группы, вырабатывается сигнал, блокирующий обращение к соответствующему фиксатору записи (например, к фиксатору 10 записи, как показано на фиг. 3 знаком *, два знака * соответствуют блокировке выборки двух одноразрядных накопителей 23 и 24). На выходах элементов И 48 (вых. 48.2 и вых. 48.4, момент Т6, фиг. 3) с помощью сигналов с выходов счетчика 35 выборки и триггера 50 формируются уровни "1" и "0", соответствующие признакам "свежей" и "устаревшей" информации. Однако "1" не записывается из-за отсутствия сигнала выборки, а "0" записывается в накопители 23, 24 фиксатора 12 записи. Информационный код в накопители 2, 4 не записывается из-за снятия режима записи. На этом цикл записи заканчивается.

В режиме считывания (фиг. 3, Т7...Т10) на вход 15 выборки подают импульсную последовательность с частотой, превышающей допустимую частоту работы накопителей 1...4 (но не более чем в 2 раза). Импульсы выборки формируются на выходах элементов И 37 и через входы второй группы коммутатора 45 выборки поступают на входы выборки накопителей 1, 2 и 3, 4. Адресный код с шины 16 заносится в регистры 19 адреса накопителей 1, 2 и 3, 4 попеременно. Информационный код считывается одновременно с накопителей 1 и 2 или 3 и 4 (считывание по "вертикали") и поступает на информационные входы коммутатора 8, на управляющие входы которого поступают сигналы с блока 13 приоритета, определяющего в каком из накопителей (1...4) содержится "свежая" информация, т.е. поступившая при записи позже.

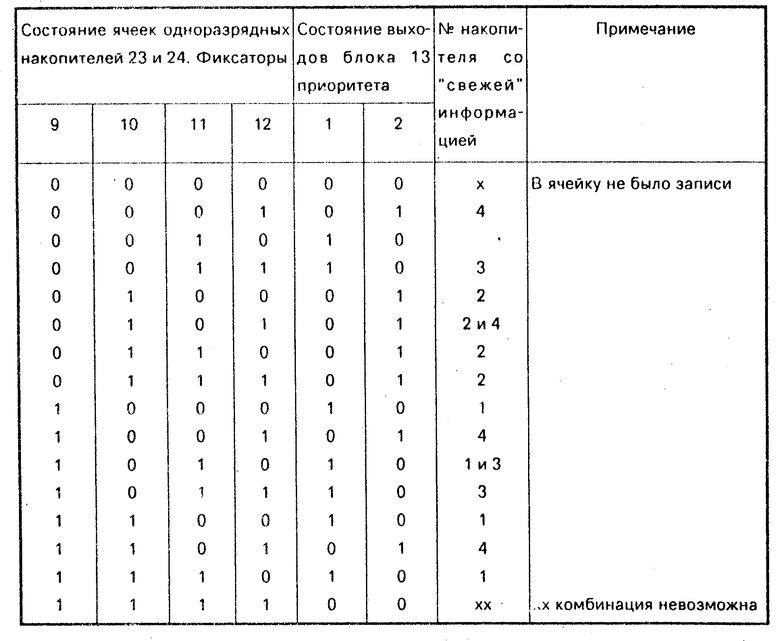

Одновременно с попеременным считыванием информации из накопителей 1, 2 и 3, 4 производится попеременное считывание признаков "свежей" ("1") или "устаревшей" ("0") информации соответственно из всех одноразрядных накопителей 23 или всех накопителей 24 фиксаторов 9...12 записи. Режим считывания фиксаторов записи определяется сигналом режима с выхода элемента ИЛИ 38. Импульсы выборки поступают через входы вторых групп коммутаторов 46, 47 выборки на одноразрядные накопители попеременно, что обеспечивает синхронность считывания с накопителями 1, 2 или 3, 4. Код адреса записывается в регистры 25 адреса, проходя через адресные коммутаторы 21 по второму направлению коммутации, разрешенному сигналом режима с выхода элементов НЕ 22. Возможные (после режима записи) состояния ячеек одноразрядных накопителей 23 или 24 фиксаторов записи 9...12 для текущего момента считывания приведены в таблице.

Считываемая с одноразрядных накопителей 23 или 24 информация (в виде четырехразрядного кода) поступает в блок 13 приоритета с выхода фиксаторов 9. ..12 записи. Уровни сигналов на выходах блока 13 приоритета определяются следующим.

В связи с тем, что при записи занесение "1" в текущем такте в одноразрядные накопители 23, 24 i-го (i=9, 10, 11, 12) фиксатора записи вызывает (благодаря связи адресный выход фиксатора - второй адресный вход) занесение "0" в следующем такте в одноразрядные накопители 23, 24 (i-1)-го фиксатора записи (i-1=12, 9, 10, 11) по тому же адресу, то в комбинациях выходных состояний фиксаторов записи, имеющих только две рядом расположенные "1" (0011, 0110, 1001, 1100) приоритет отдается фиксатору записи, имеющему меньший номер (т. е. 9<10, 10<11, 11<12, по 12<9) и указанной выше группе комбинаций соответствуют номера фиксаторов 11, 10, 12, 9. Именно эти фиксаторы при принятой системе связей между фиксаторами 9...12 записи соответствуют накопителям со "свежей", т.е. позже запомненной, информацией, а именно накопителям с номерами 3, 2, 4, 1, т.е. например, комбинация 0011 свидетельствует о том, что более поздняя информация поступила в накопитель 3, а не в накопитель 4 (если бы было наоборот, то комбинация была бы 00 1, знак * означает изменение содержимого одноразрядных накопителей фиксатора записи с меньшим номером (11) под воздействием "1" фиксатора записи с большим номером (12)). Следовательно, на выходах блока 13 приоритета вышеуказанным входным комбинациям соответствует набор 10, 01, 01, 10, подаваемый на управляющие входы коммутатора 8 и позволяющий пропустить на выход 18 информационный код с накопителей 3, 2, 4, 1 соответственно.

1, знак * означает изменение содержимого одноразрядных накопителей фиксатора записи с меньшим номером (11) под воздействием "1" фиксатора записи с большим номером (12)). Следовательно, на выходах блока 13 приоритета вышеуказанным входным комбинациям соответствует набор 10, 01, 01, 10, подаваемый на управляющие входы коммутатора 8 и позволяющий пропустить на выход 18 информационный код с накопителей 3, 2, 4, 1 соответственно.

Группе комбинаций выходных состояний 0111, 1011, 1101, 1110 соответствуют номера фиксаторов 10, 11, 12, 9 записи, т.е. приоритет отдается накопителям 2, 3, 4, 1. Так, например, комбинация 1101 свидетельствует о том, что более поздняя информация поступила в накопитель 4 (если бы более поздней была информация в накопителе 1 или 2, то комбинация выглядела бы как 110 или

или  101). Кодовый набор на выходах блока 13 приоритета будет 01, 10, 01, 10.

101). Кодовый набор на выходах блока 13 приоритета будет 01, 10, 01, 10.

Группе комбинаций выходных состояний 0001, 0010, 0100, 1000 соответствуют номера фиксаторов 12, 11, 10, 9 записи, т.е. приоритет отдается накопителям 4, 3, 2, 1. Кодовый набор на выходах блока 13 приоритета будет 01, 10, 01, 10.

Группе комбинаций 0101, 1010 соответствуют номера фиксаторов 12 и 10, 11 и 9 записи, т.е. приоритет отдается накопителям 4 и 2, 3 и 1, но так как в этих парах запомнена одинаковая информация, то кодовый набор на выходах блока 13 приоритета должен быть 01, 10.

Кодовая комбинация 0000 свидетельствует об отсутствии обращений в данную ячейку накопителей 1...4 и одноразрядных накопителей 23, 24 фиксаторов 9... 12 записи.

Кодовая комбинация 1111 невозможна, так как запись "1" в текущем такте вызывает запись "0" в последующем такте.

В последних двух случаях целесообразно на выходах блока 13 приоритета устанавливать комбинацию 00, которая минимизирует его логическую структуру и запрещает выдачу информации коммутатора 8. Вышеприведенные рассуждения сведены в таблицу (графы 5...8), на основании которой как таблицы истинности построен блок 13 приоритета.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1990 |

|

SU1785034A1 |

| Устройство сопряжения | 1979 |

|

SU857967A1 |

| Запоминающее устройство | 1977 |

|

SU733021A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Устройство для записи информации в матричный накопитель | 1984 |

|

SU1191941A1 |

Изобретение относится к запоминающим устройствам (ЗУ) и решает задачу повышения быстродействия ЗУ с сохранения произвольности доступа к ячейкам памяти. ЗУ содержит накопитель, регистр числа, блок управления, коммутатор. В него введены накопители, второй регистр числа, фиксаторы записи, блок приоритета с соответствующими связями. 4 з.п. ф-лы, 1 табл., 3 ил.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Запоминающее устройство | 1987 |

|

SU1529287A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-07-30—Публикация

1991-06-10—Подача