Изобретение относится к запоминающим устройствам (ЗУ) и может быть использовано для построения высоконадлежащих систем памяти большой емкости и различной конфигурации, имеющих возможность работать одновременно с разными типами ЭВМ.

Известно ЗУ с исправлением ошибок, содержащее накопительные блоки, каждый из которых соединен с блоком обнаружения и коррекции ошибок. В процессе работы в каждый накопительный блок записывается группа разрядов кодового-слова. Число информационных разрядов в этой группе может быть равно 2, 4, 5, 8, 10 и т.д., кроме того в группу входит один контрольный разряд. При таком способе построения ЗУ возможна коррекция любого количества разрядов, содержащихся в одной группе, что дает возможность продолжить работу при отказе не более чем в одном накопительном блоке 1.

Недостатком данного устройства является ограничение выбора числа информационных разрядов в кодовом слове, которое выбирается из ряда 14, 44, 65, 152, 230 и т.д. Это условие далеко не всегда.является приемлемым, в частности нельзя выбрать длину информационного слова, равной целой степени двойки.

Из известных устройств наиболее близким техническим решением к предлагаемому является запоминающее устройство с коррекцией ошибок, содержащее схему управления, дешифратор адреса буферный к-разрядный регистр данных (k - число разрядов в :одовом слове и k накопител.ных блоков, причем входы схемы управления соединены с входными шинами устройства, выходы дешифратора адреса соединены со всеми накопительными блоками и с буферным регистром данных, первые k входов буферного регистра данных соединены с входными шинами устройства, вторые k входов соединены с соответствующиг га выходами накопительных блоков, первые k выходов буферного регистра данных соединены с выходными шинами устройства, а вторые k выходов - с соответствующими входами накопительных блоков 2.

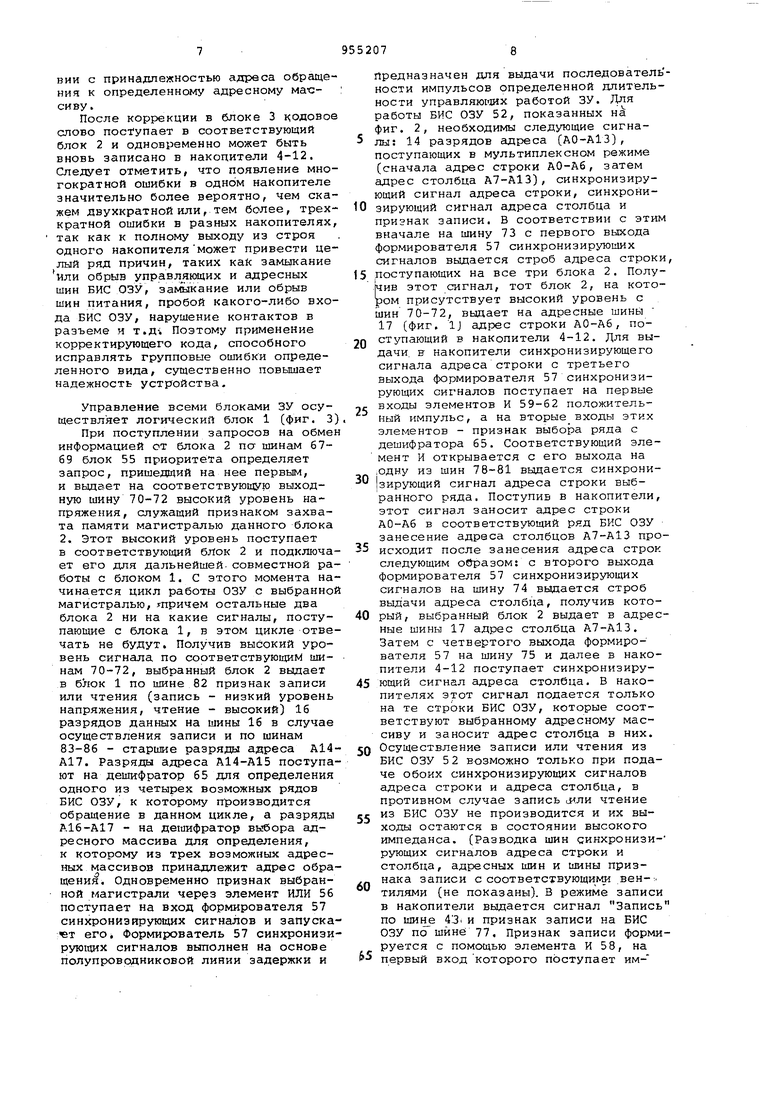

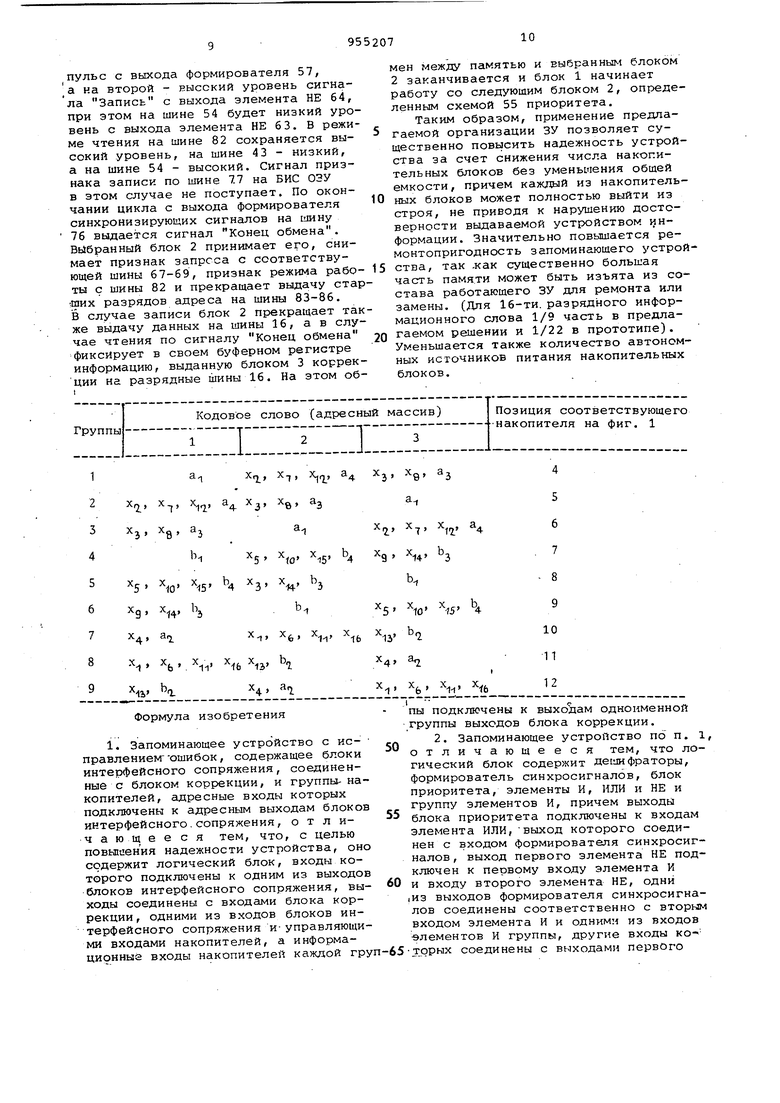

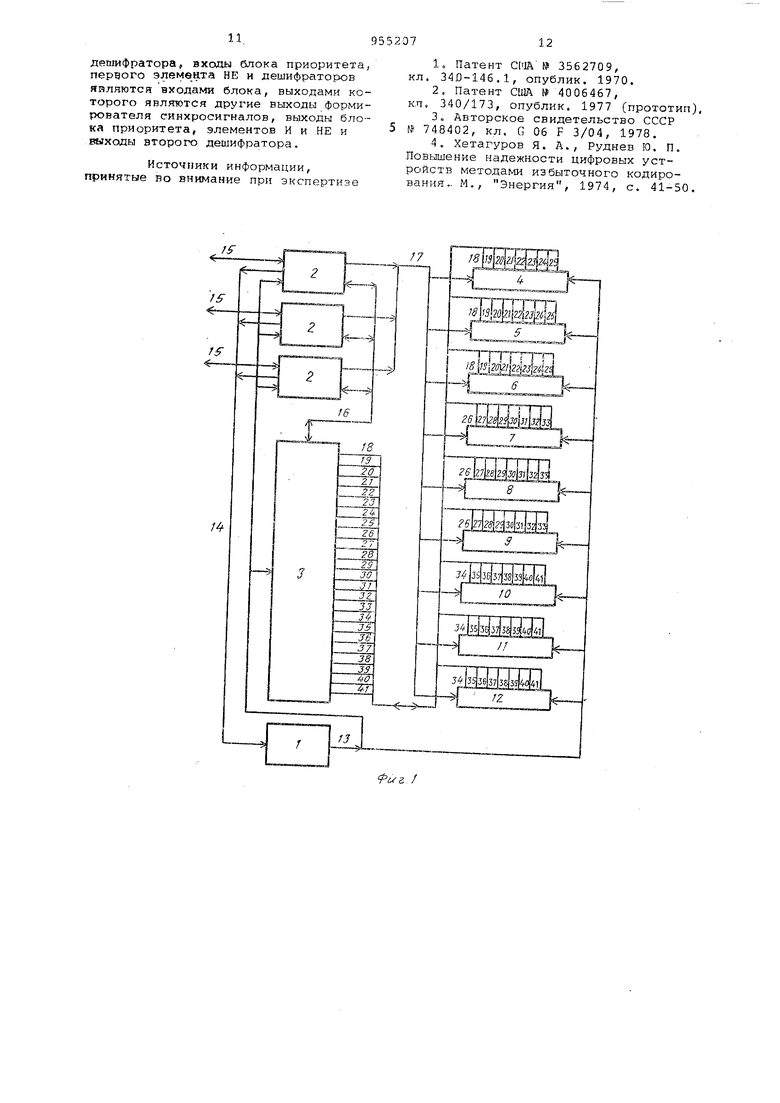

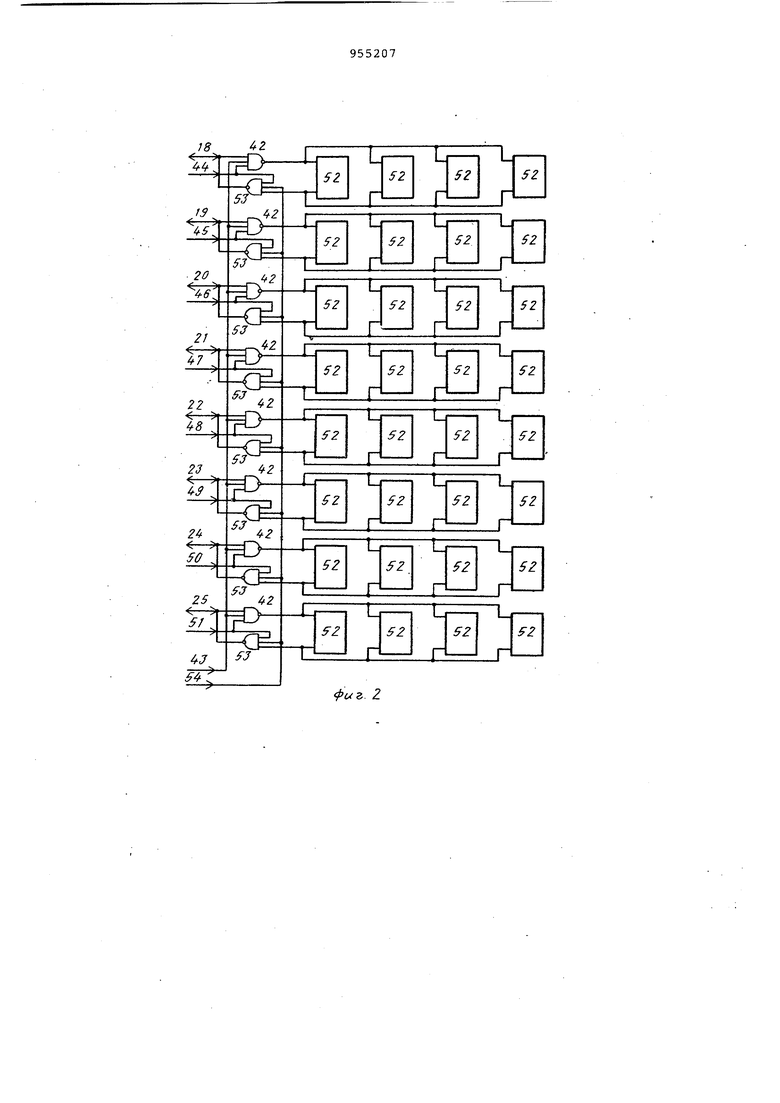

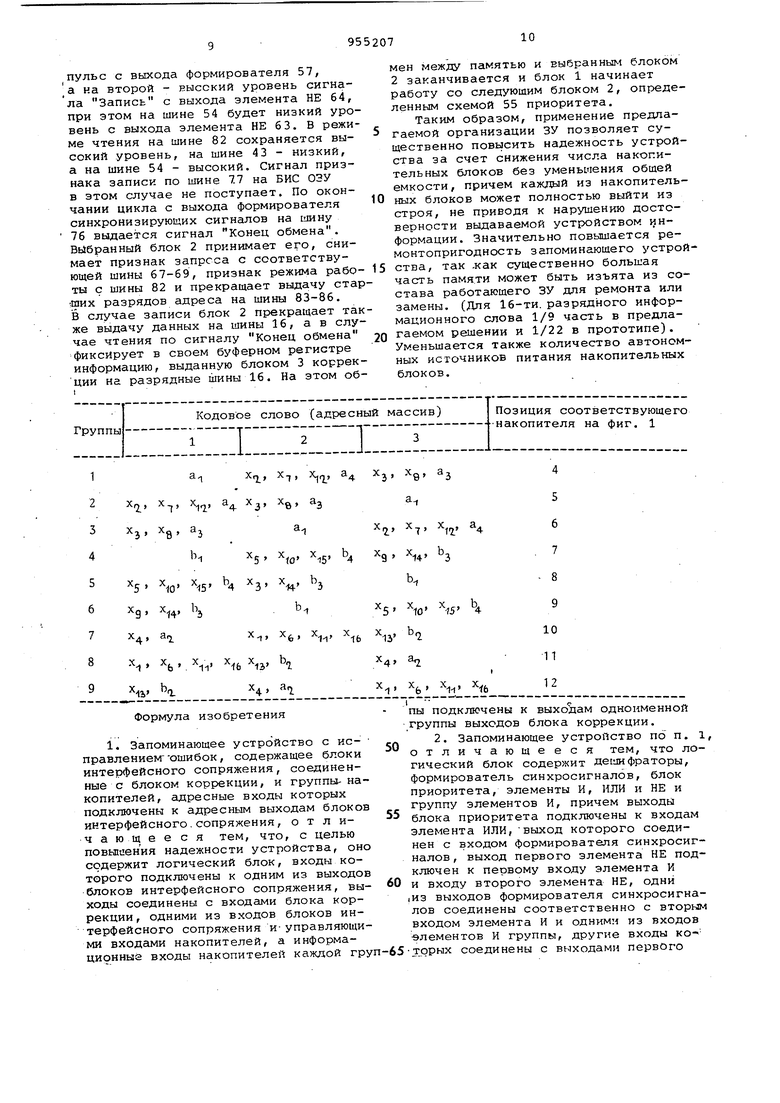

Недостатком этого ЗУ является невысокая надежность из-за большого числа накопительных блоков. С увеличением их числа вероятность появления некорректируемой ошибки возрастает (например, в простейшем случае. вследствие возрастания вероятности нарушения контактов в разъемах сраз у двух накопительных блоков, кроме того, уменьшается объем части памят имоощей право на отказ, равный при 1 данной структуре . Из-за большого числа накопительных блоков увеличивается также громоздкость устройства. Цель изобретения - повышение надежности устройства. Указанная цель достигается тем, что в запоминающее устройство с исправлением ошибок, содержащее блоки интерфейсного сопряжения, соединенн с блоком коррекции, и группы накопи телей, адресные входы которых подкл чены к адресным выходам блоков инте фейсного сопряжения, введен кий блок, входы которого подключены к одним из выходов блоков интерфейсного сопряжения, выходы соединены с входами блока коррекции, одними из входов блоков интерфейсного сопр жения и управлнющими входами накопи телей, а информационные входы накопителей каждой группы подключены к выходам одноименной группы выходов блока корреции. Логический i блок содержит дешифра торы, формирователь синхросигналов, блок приоритета, элементы И, ИЛИ и НЕ и группу элементов И, причем выходы блока приоритета подключены к входам элемента ИЛИ, выход которо го соединен с входом формирователя синхросиг.налов, выход первого элемента НЕ подключен к первому входу элемента И и входу второго элемента НЕ, одни из выходов формирователя синхросигналов соединены соответственно с вторым входом элемента-И и одними из входов элементов И группы другие входы которых соединены с выходами первого дешифратора, входы блока приоритета, первого элемента НЕ и дешифраторов являются входами блока, ВЕЛходами которого являются другие выходы формирователя синхросигналов, выходы блока приоритета, элементов И и НЕ и выходы второго дешифратора. На фиг. 1 изображена структурная схема запоминающего устройства с коррекцией ошибок; на фиг. 2 - стру турная схема одного из вариантов накопителя; на фиг. 3 - структурная схема одного из вариантов логическо го . Устройство (фиг, 1) содержит логический блок 1, блоки 2 интерфейсн го Сопряжения СЗЗ, блок 3 коррекции первую группу накопителей 4-6, вторую группу накопителей 7-9, третью группу накопителей 10-12. Блок 1 соединен посредством выходных- управляю1цих ишн 13 с входами всех блоков устройства и посредством входных управляющих шин 14 с выходами каждого блока 2.. Каждый блок 2 соединен с шинами соответствующей внешней магистрали 15, с блоком 3 посредством шин-16 и с накопителями 4-12 посредством адресных шин 17, Блок 3 соединен посредством шин 18-25 с накопителями 4-6, посредством шин 26-33 с накопителями 7-9 и посредством шин 34-41 с накопителями 10-12. Накопитель(на фиг. 2 изображен, например, накопитель 4) содержит элементы И-НЕ 42, управляющие шины 43-51, большие интегральные схемы оперативного запоминающего устройства (БИС, ОЗУ) 52, элементы И-НЕ 53, управляющую шину 54. Логический блок 1 (фиг. 3 содержит блок 55 приоритета, элемент ИЛИ 56, формирователь 57 синхросигналов, элемент И 58, группу элементов И 59-62, первый 63 и второй 64 элементы НЕ, дешифраторы 65 и 66. Блок 1 имеет входные 67-69, выходные шины -70-81, входные шины 82-86, выходные шины 87-89. Устройство работает следующим образом. При обращении к ЗУ по одной из внешних магистралей 15 соответствующий блок 2 преобразует сигналы интерфейса данной магистрали к некоторому общему виду, пригодному для дальнейшего использования в настоящем устройстве. От блока 2 запрос по управляющим шинам 14 поступает в блок 1, который определяет приоритет поступивших запросов и выдает последовательность сигналов, управляющих работой всех блоков ЗУ. По команде из блока 1 адрес выбранной ячейки памяти поступает по адресным шинам 17 из соответствующего блока 2 в накопители 4-12, а разряды информации (например-, 16 разрядов), по шинам 16 в блок 3, где формируется кодовое слово двумерного итеративного, кода 4 Данный код способен исправлять групповые ошибки, находящиеся в одной диагонали матрицы кодового слова, которая для 16-ти разрядов информации имеет следующий вид: XJ X,2 XJ х а 5 6 7 а 1 9 -10 1-1 -13 15 f-16 4 bi b bj b4 где x - x - разряды информации; N- . Dx|- 04 - контрольные разряды. В настоящем ЗУ разряды.каждой из девяти диагоналей этой матрицы записываются в отдельный накопитель, поэтому возможно исправление как одиночной, так и групповой ошибки любого из накопителей (при условии исправной работы остальных). Например, разряд а можно записать в накопитель 4, разряды х , а в накопитель 5, разряды з з в накопитель б и т.д. Однако в этом случае из-за различного числа разрядов, хранимых в каждом накопителе, взаимозаменяемость последних будет исключена. Для получения возмо чвости использования в ЗУ одинаковых накопи телей производится следующее. Подгру пы разрядов, находящихся в диагоналя нескольких кодовых слов, объединяются в группы таким образом, чтобы общее количество разрядов в группе было одинаковым. При этом, из каждого кодового слова либо совсем не выбирается, либо выбирается только одна подгруппа разрядов (диагональ),число же кодовых слов может быть произволь ным. Для рассматриваемого примера чи ло кодовых слов принято равным трем, и одно из возможных распределений ра рядов по группам пpивeдe o в таблице Объединив в групппу три кодовых слова, мы получили 9 групп по 8 разрядов в каждой. Составив группы из двух и одного кодового слова, мы мог ли бы получить 18 групп по 4 разряда Однако, так как каждая группа разрядов записывается в отдельный накопитель, то это привело бы к увеличению их числа и снижению надежности ЗУ. Таким образом, в данном примере в каждый накопитель может быть записано восемь разрядов, а какая подгруппа разрядов будет записана в какой накопитель в данном цикле обращения к ЗУ, зависит от номера кодового ело ва. Например, разряды х, х-,, х,, а второго кодового слова зппишутся в накопитель 4, разряды Xj, Xg, а в накопитель 5, разрядка - в накопи тель б и так все 24 разряда второго кодового слова. Так как емкость ЗУ составляет 196608 слов, то все адресное пространство необходимо разби на три равные массива по 65536 слов в каждом, при этом номер массива будет служить признаком подгруппы разрядов записываемой в данном цикле в тот или иной накопитель. Разбивку адресного пространства на три части можно Провести любым способом, в дан ном ЗУ номер адресного массива определяется с помощью двух старших разрядов адреса А1б и А17. Если А1б А17 О - первый адрес ный массив, если А16 1; А17 О второй адресньй массив, а если А16 0; А17 1 - третий адресный массив. Комбинация А16 А17 1 не используется, так как превьпиает объем адресного пространства ЗУ - 196608 слов. Определение номера адресного массива производится в блоке 1, а оставшиеся 16 разрядов адреса АО-А15 используются следующим образом: АОА13 - локализация адреса внутри БИС ОЗУ, А14-А15 - выбор ряда из восьми БИС ОЗУ внутри накопителей 4-12. В качестве npuNiepa рассмотрим запись информации в первый накопитель 4 (фиг. 2). По команде из блока 1 по шинам 18-25 в накопитель 4 из блока коррекции 3 поступают разряди а, х, X-J, х, а, Xj, х,, а, которые далее пооходят на первые входы элементов. И-НЕ 42. На вторые входы этих элементов по управляющей шине 4J из блока 1 поступает признак записи, а на третьи (также из блока 1) по управляющим шинам 44-51 - признак номера адресного массива, причем, так как, данный накопитель является первым, а адрес обращения относится, например, к третьему адресному массиву, то разрешающий запись сигнал придет только по шинам 49-51 (таблица 1). Если адрес обращения относится к второму адресному массиву, то разрешающий сигнал придет по шинам 45-48, а если к первому, то по шине 44. Таким образом, соответствующие элементы И-НЕ 42 откроются и необходимая подгруппа разрядов запишется в выбранный ряд БИС ОЗУ 52. (Управляющие и адресные шины БИС ОЗУ с соответствующими вентилями не показаны). Из сказанного становится ясной коммутация управляющих шин 44-51, а именно, шина 44 накопителя 4 объединяется с шинами 45-48 накопителя 5, с шинами 49-51 накопителя 6, с шиной 44 накопителя 7 и т.д. в соответствии с таблицей для первого адресного массива. 1Чины 45-48 накопителя 4 объединяются с шинами 49-51 накопителя 5, с шиной 44 накопителя 6 и т.д. для второго адресного массива. 1аины 49-51 накопителя 4 объединяются с шиной 44 накоп{йеля 5,; с шинами 45-48 накопн-теля 6 и т.д. для третьего адресного массива. Таким образом, при подобной коммутации, выполненной -с внешней стороны разъемов Накопителей, приход разрешающего сигнала по одной из этих трех объединенных шин определит номер адресного массива, т.е. необходимую подгруппу разрядов, записываемую в конкретный накопитель. При чтении, информация из выбраного ряда БИС ОЗУ 52 через элементы И-НЕ 53 поступает на мины 18-25 и алее в блок 3 коррекции, причем в этом случае на вторые входы элеентов И-НЕ 53 по управляющей шине 54 поступает признак чтения. Подача сигналов на управляющие 44-51 производится аналогично в соответстВИИ с принадлежностью адреса обращения к определенному адресному мах;сиву.

После коррекции в блоке 3 кодовое слово поступает в соответствующий блок 2 и одновременно может быть вновь записано в накопители 4-12. Следует отметить, что появление многократной ошибки в одном накопителе значительно более вероятно, чем скажем двухкратной или, тем более, трехкратной ошибки в разных накопителях, так как к полному выходу из строя одного накопителяможет привести целый ряд причин, таких ка{ замыкание или обрыв управл яющих и адресных шин БИС ОЗУ, замыкание или обрыв шин питания, пробой какого-либо входа БИС ОЗУ, нарушение контактов в разъеме и т.д Поэтому применение корректирующего кода, способного исправлять групповые ошибки определенного вида, существенно повышает надежность устройства.

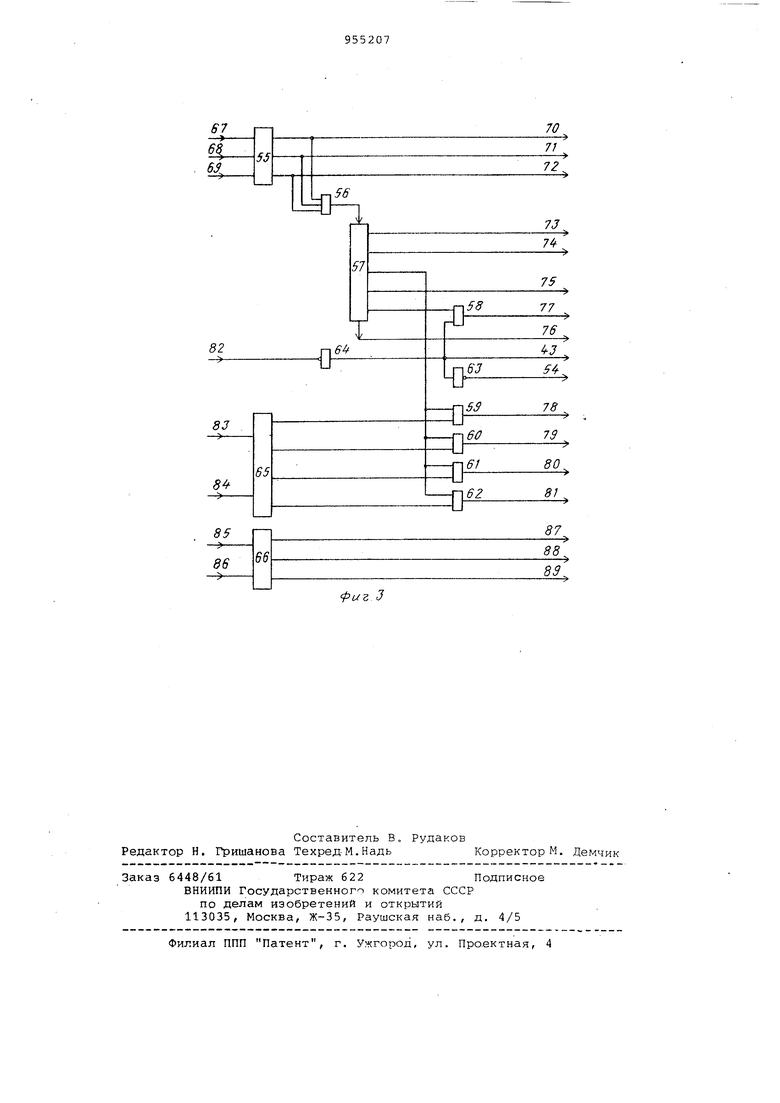

Управление всеми блоками ЗУ осуществляет логический блок 1 (фиг. 3)

При поступлении запросов на обмен информацией от блока 2 па шинам 6769 блок 55 приоритета определяет запрос, пришедщий на нее первым, и выдает на соответствующую выходную шину 70-72 высокий уровень напряжения, служащий признаком захвата памяти магистралью данного блока 2, Этот ВЫСОКИЙ уровень поступает в соответствующий блок 2 и подключает его для дальнейшей.совместной работы с блоком 1. С этого момента начинается цикл работы ОЗУ с выбранной магистралью, тричем остальные два блока 2 ни на какие сигналы, поступающие с блока 1, в этом цикле отвечать не будут. Получив высокий уровень сигнала по соответствующим шинам 70-72, выбранный блок 2 выдает в блок 1 по шине 82 признак записи или чтения (запись - низкий уровень напряжения, чтение - высокий) 16 разрядов данных на шины 16 в случае осуществления записи и по шинам 83-86 - старшие разряды адреса А14А17. Разряды адреса А14-А15 поступают на дешифратор 65 для определения одного из четырех возможных рядов ВИС ОЗУ, к которому производится обращение в данном цикле, а разряды А16-А17 - на дешифратор выбора адресного массива для определения, к которому из трех возможных адресных массивов принадлежит адрес обращения. Одновременно признак выбранной магистрали элемент ИЛИ 56 поступает на вход формирователя 57 синхронизирующих сигналов и запускает eroi Формирователь 57 синхронизирующих сигналов выполнен на основе полупроводниковой линии задержки и

Предназначен для выдачи последовательности импульсов определенной длительности управляющих работой ЗУ. Для работы БИС ОЗУ 52, показанных на фиг. 2, необходимы следующие сигналыг 14 разрядов адреса (АО-А13}, поступающих в мультиплексном режиме (сначала адрес строки АО-А6, затем адрес столбца А7-А13), синхронизирующий сигнал адреса строки, синхронизирующий сигнал адреса столбца и

признак записи. В соответствии с этим вначале на шину 73 с первого выхода формирователя 57 синхронизирующих сигналов выдается строб адреса строки,

5 поступающих на все три блока 2. Полу|чив этот сигнал, тот блок 2, на котором присутствует высокий уровень с шин 70-72, выдает на адресные шины 17 (фиг, 1J адрес строки АО-А6, поQ ступающий в накопители 4-12. Для выдачи, н накопители синхронизирующего сигнала адреса строки с третьего выхода формирователя 57 синхронизирующих сигналов поступает на первые

г входы элементов И 59-62 положительный импульс, а на вторые входы этих элементов - признак выбора ряда с дешифратора 65. Соответствующий элемент И открывается с его выхода на юдну из шин 78-81 выдается синхронизирующий сигнал адреса строки выбранного ряда. Поступив в накопители, этот сигнал заносит адрес строки АО-А6 в соответствующий ряд БИС ОЗУ занесение адреса столбцов А7-А13 происходит после занесения адреса строк следующим о&разом: с второго выхода формирователя 57 синхронизирующих сигналов на шину 74 выдается строб выдачи адреса столбца, получив который, выбранный блок 2 выдает в адресные шины 17 адрес столбца А7-А13. Затем с четвертого выхода формирователя 57 на шину 75 и далее в накопители 4-12 поступает синхронизирующий сигнал адреса столбца. В накопителях этот сигнал подается только на те строки БИС ОЗУ, которые соответствуют выбранному адресному массиву и заносит адрес столбца в них.

Q Осуществление записи или чтения из БИС ОЗУ 5 2 возможно только при подаче обоих синхронизирующих сигналов адреса строки и адреса столбца, в противном случае запись яли чтение

5 из БИС ОЗУ не производится и их выходы остаются в состоянии высокого импеданса. (Разводка шин синхронизирующих сигналов адреса строки и столбца, адресных шин и шины признака записи с соответствующие вен-,. тилями (не показаны). В режиме записи в накопители выдается сигнал Запись по 43. и признак записи на БИС ОЗУ по шине 77. Признак записи формируется с помощью элемента И 58, на

5 первый вход которого поступает им-

пульс с выхода формирователя 57, а ка второй - высокий уровень сигнала Запись с выхода элемента НЕ 64, при этом на шкне 54 будет низкий уровень с выхода элемента НЕ 63. В режиме чтения на шине 82 сохраняется высокий уровень, на шине 43 - низкий, а на шине 54 - высокий. Сигнал признака записи по шине 77 на БИС ОЗУ в этом случае не поступает. По окончании цикла с выхода формирователя синхронизирующих сигналов на шину 76 выдается сигнал Конец обмена, выбранный блок 2 принимает его, снимает признак запроса с соответствующей шины 67-69, признак режима работы с шины 82 и прекращает выдачу старших разрядов адреса на шины 83-86. is случае записи блок 2 прекращает также выдачу данных на шины 16, а в случае чтения по сигналу Конец обмена фиксирует в своем буферном регистре информацию, выданную блоком 3 коррекции на разрядные шины 16. На этом обмен между памятью и выбранным блоком 2 заканчивается и блок 1 начинает работу со следующим блоком 2, определенным схемой 55 приоритета.

Таким образом, применение предлагаемой организации ЗУ позволяет существенно повысить надежность устройства за счет снижения числа накопительных блоков без уменьшения общей емкости, причем каждый из накопительных блоков может полностью выйти из строя, не приводя к нарушению достоверности выдаваемой устройством информации. Значительно повышается ремонтопригодность запоминающего устройства, так .как существенно большая

часть памяти может быть изъята из состава работающего ЗУ для ремонта или замены. (Для 16-ти, разрядного информационного слова 1/9 часть в предлагаемом решении и 1/22 в прототипе). Уменьшается также количество автономных источников питания накопительных блоков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1061176A1 |

| Цифровая адаптивная антенная система | 1990 |

|

SU1810943A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1406637A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Устройство адресации к динамической памяти | 1987 |

|

SU1444785A1 |

Формула изобретения 1. Запоминающее устройство с исправлением ошибок, содержащее блоки интерфейсного сопряжения, соединенные с блоком коррекции, и группы-накопителей, адресные входы которых подключены к адресным выходам блоков интерфейсного.сопряжения, отличающееся тем, что, с целью повыиения надежности устройства, оно содержит логический блок, входы которого подключены к одним из выходов блоков интерфейсного сопряжения, выходы соединены с входами блока коррекции, одними из входов блоков интерфейсного сопряжения и-управляющими входами накопителей, а информационные входы накопителей каждой гру пы подключены к выходам одноименной .группы выходов блока коррекции. 2. Запоминающее устройство по п. 1, отличающе еся тем, что логический блок содержит Де1-ифраторы, формирователь синхросигналов, блок приоритета, элементы И, ИЛИ и НЕ и группу элементов И, причем выходы блока приоритета подключены к входам элемента ИЛИ,выход которого соединен с входом формирователя синхросигналов , выход первого элемента НЕ подключен к первому входу элемента И и входу второго элемента НЕ, одни Из выходов формирователя синхросигналов соединены соответственно с вторым входом элемента И и одними из входов элементов И группы, другие входы которых соединены с выходами первого

дешифратора, входы блока приоритета) первого элемента НЕ и дешифраторов являются входами блока, выходами которого являются другие выхоли формирователя синхросигналов, выходы блока приоритета, элементов И и НЕ и выходы второго дешифратора.

Источники информации, принятые во внимание при экспертизе

/

1,Патент № 3562709,

, 34D-146,1, опублик. 1970.

кл,

340/173, опублик. 1977(прототип),

4,Хетагуров Я. А., Руднев Ю. П. Пов1лшение надежности цифровых устройств методами избыточного кодирования- М., Энергия, 1974, с. 41-50.

фиг. Z

фиг. 3

Авторы

Даты

1982-08-30—Публикация

1980-09-29—Подача