Изобретение относится к логическим элементам автоматики и вычислительной техники.

Известный пороговый логический элемент, состоящий из входных токовых переключателей, источника опорного и фиксирующих напряжений и выходного переключателя, содержит большое количество транзисторов, что увеличивает стоимость и снижает надежность его работы.

Целью изобретения является упрощение логического элемента. Это достигается тем, что в нем во входных переключателях и в источнике, опорного и фиксирующих напряжений включены многоэмиттерные транзисторы, причем база многоэмиттерного транзистора входных переключателей соединена с первым эмиттером транзистора источника опорного и фиксирующих напряжений, два других эмиттера которого соединены со входами выходного переключателя, к одному из которых подключен также коллектор миогоэмиттерного транзистора входных переключателей, а каждый эмиттер последнего соединения с эмиттером одного из входных транзисторов.

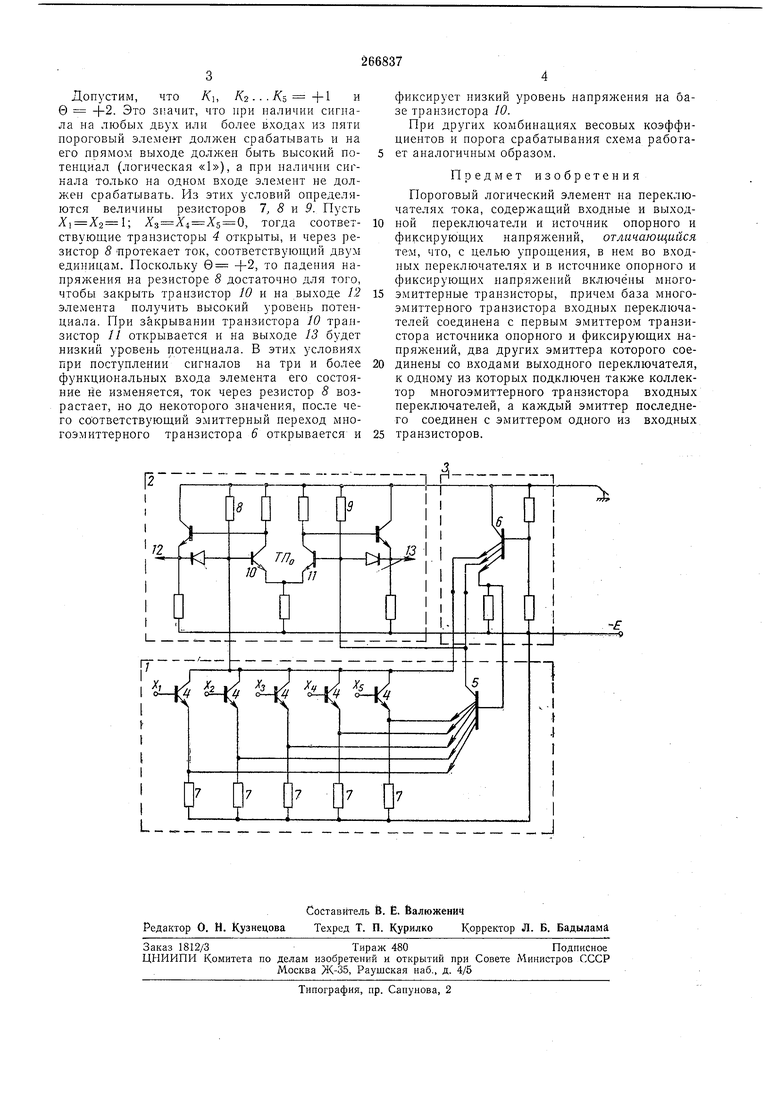

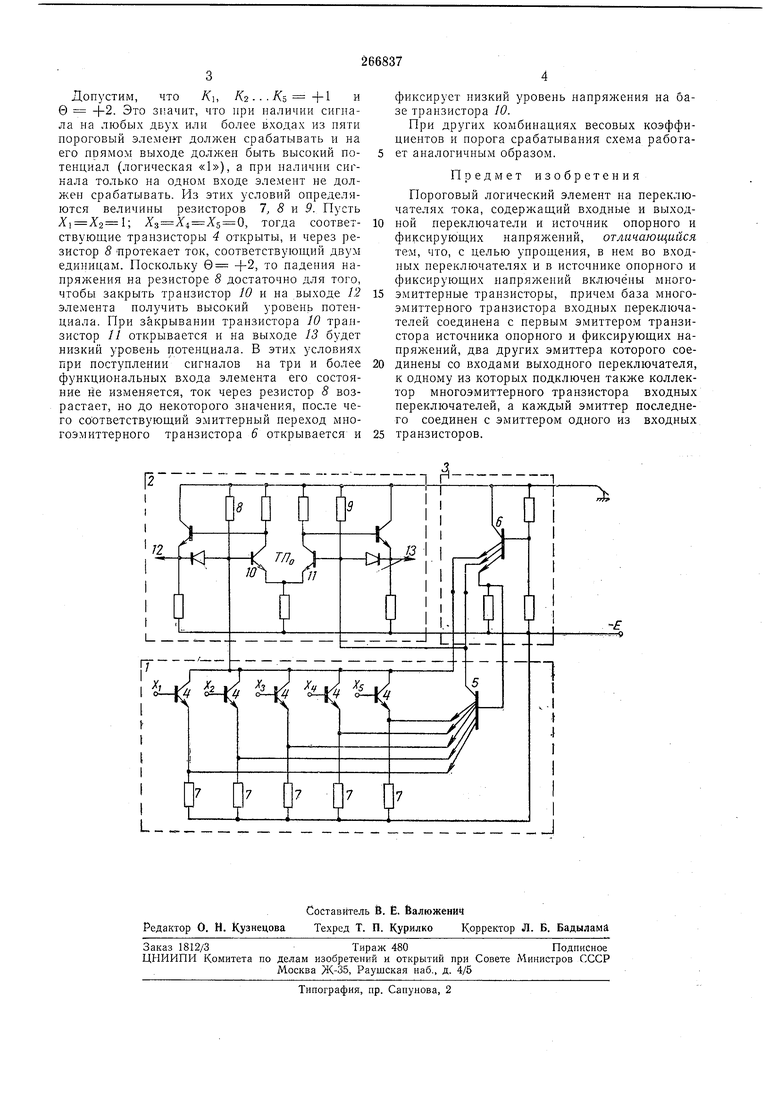

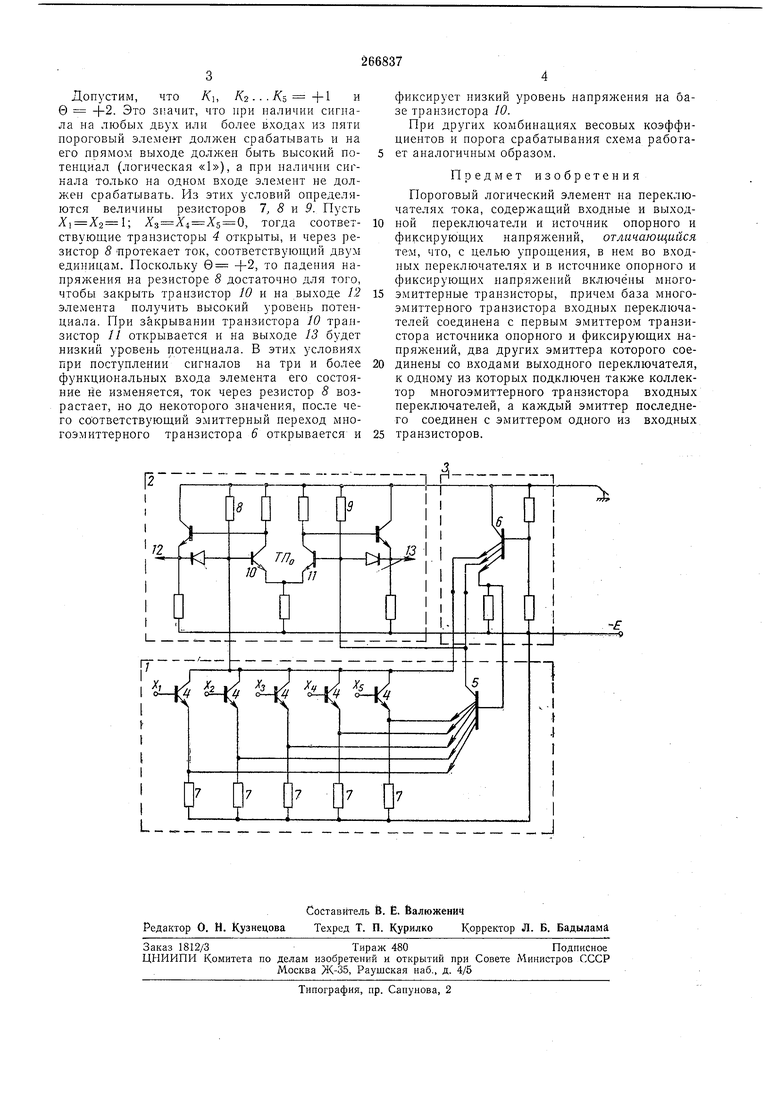

На чертеже изображена схема порогового элемента.

на входных транзисторах 4, на базы которых подаются сигналы Х;, па многоэмиттериом транзисторе 5, каждый эмиттер которого соединен с эмиттером каждого транзистора 4,

образуя с ним входной переключатель тока, а коллектор и база транзистора 5 подсоединены к двум эмиттерам транзистора 6, третий эмиттер которого подключен к точке соединения коллекторов транзисторов 4. В эмиттеры транзисторов 4 включены резисторы 7, задающие величины весовых коэффициентов АГ/. Порог срабатывания в элемента определяется величинами резисторов 8 и 9, подключенных между источником и соответствующими базами транзисторов 10, 11 выходного переключателя, прямой и инверсный выходы которого соответственно 12 и 13. При этом эмиттер транзистора 6, соединенный с базой транзистора 5, является выходом опорного напряжения, а два других его эмиттера--выходами фиксирующих напряжений.

При отсутствии входных сигналов, т. е. при -Y|, 2 - 5 О, транзисторы 4 закрыты,

поэтому транзистор 10 открыт, и на прямом выходе 12 порогового элемента имеется низкий потенциал (логический «О). В это время все эмиттеры мпогоэмиттерного транзистора 5 проводят ток, транзистор 11 закрыт, и на выДопустим, что /С, К.2 Ко и в -J-2. Это значит, что при паличии сигнала на любых двух или более входах из пяти пороговый элемент должен срабатывать и на его прямом выходе быть высокий потенциал (логическая «1), а при паличии сигнала только на одном входе элемент не должен срабатывать. Из этих условий определяются величины резисторов 7, 8 и 9. Пусть 0, тогда соответствующие транзисторы 4 открыты, и через резистор 8 протекает ток, соответствующий двум единицам. Поскольку в +2, то падения напряжения на резисторе 8 достаточно для того, чтобы закрыть транзистор 10 и на выходе 12 элемента получить высокий уровень потенциала. При закрывании транзистора W транзистор 11 открывается и на выходе 13 будет низкий уровень потенциала. В этих условиях при поступлении сигналов на три и более функциональных входа элемента его состояние не изменяется, ток через резистор 8 возрастает, но до некоторото значения, после чего соответствующий эмиттерный переход многоэмиттерного транзистора 6 открывается и

фиксирует низкий уровень напряжения на базе транзистора 10.

При других комбинациях весовых коэффициентов и порога срабатывания схема работает аналогичным образом.

Предмет изобретения

Пороговый логический элемент на переключателях тока, содержащий входные и выходной переключатели и источник опорного и фиксирующих напряжений, отличающийся те.м, что, с целью упрощения, в нем во входных переключателях и в источнике опорного и фиксирующих напряжений включены многоэмиттерные транзисторы, причем база многоэмиттерного транзистора входных переключателей соединена с первым эмиттером транзистора источника опорного и фиксирующих напряжений, два других эмиттера которого соединены со входами выходного переключателя, к одному из которых подключен также коллектор многоэмиттерного транзистора входных переключателей, а каждый эмиттер последнего соединен с эмиттером одного из входных

транзисторов. -1

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный пороговый модуль | 1973 |

|

SU493030A1 |

| Пороговый логический элемент | 1973 |

|

SU473293A1 |

| БИБЛКО|г;:А | 1973 |

|

SU373880A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| ФОРМАЛЬНЫЙ НЕЙРОН | 1973 |

|

SU375792A1 |

| УНИВЕРСАЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU364079A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многопороговый логический элемент | 1975 |

|

SU573883A1 |

| Пороговый логический элемент | 1975 |

|

SU600711A1 |

| Многопороговый логический элемент | 1972 |

|

SU481136A1 |

Даты

1970-01-01—Публикация