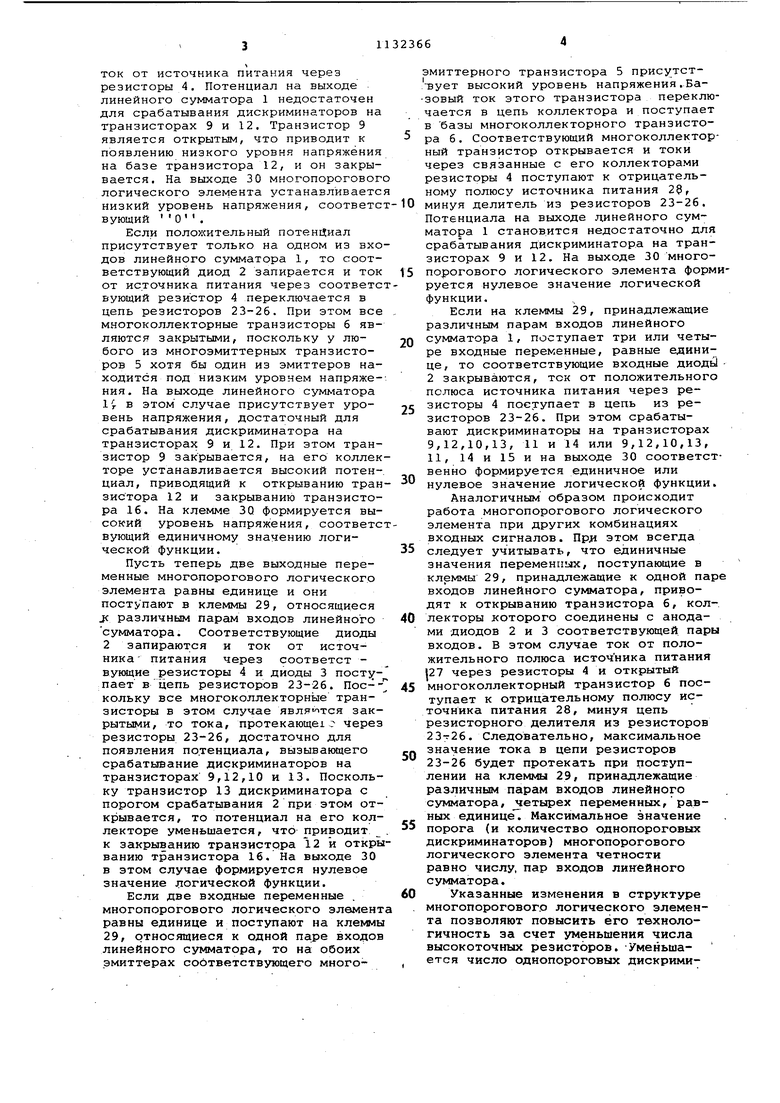

Изобретение относится к автоматике и вычислительной технике, в частности к пороговым логическим элементам. По основному авт.СВ. № 319077 известен многопороговый логический элемент, содержащий линейный суммаTopf ВЕЛполненный на. резисторах и управляемый с входными диодами, через смещающие диоды с объединенными катодами подключенный к последовательно соединенным суммирующи резисторам и многопороговому дискриминатору, выполненным в виде нескольких параллельно соединенных однопороговых дискриминаторов на транзисторе, с заземленным эмиттером база которого объединена с коллектором другого транзистора, эмиттер которого подключен к соответствующему сутлмирующему резистору, а кол лектор присоединен к базе аналогич ного транзистора в предыдущем дискриминаторе f . Недостатком многопорогового логическо1о элемента является то, чт при реализации функции четности количе ство высокоточных резисторов в таком элементе должно в два раза превосходить число логических входов Максимальное значение порога в подобном элементе не должно шревосходить 8 (исходя из требований помехоустойчивости). Это означает, что максимальное число переменных, от которых реализуется фун ция четности, также не должно превосходить 8. Это уменьшает функ циональные возможности. Цель изобретения - расширение функциональных возможностей за сче увеличения количества входов. Поставленная цель достигается т что в многопороговый логический эл мент введены для Каждой пары входов линейного сумматора многоколлекторный и многоэмиттерный транзисторы и дополнительный резистор, включенный между положительным полюсом , источника питания и базой много эмиттерного транзистора, один эмитт которого соединен с первым входом, а другой - со вторым входом соответствующей пары входов линейного сумматора, коллектор многоэмиттерно го транзистора подключен к базе многоколлекторного транзистора, эми тер которого соединен с отрицательным полюсом источника питания, один коллектор подключен к анодам диодов первого входа, второй коллектор сое динен с анодами диодов второго вход соответствующей пары входов линейно го сумматора. На чертеже представлена принципиальная схема многопорогового логического элемента. Многопорогойый логический элемент четности содержит линейный сумматор 1, состоящий из входных диодов 2, смещающих диодов 3, резисторов. 4, образующих резисторную матрицу, многоэ1 ттерных 7ранзист.оров 5, много-, коллекторных транзисторов 6 и допол-. нительных резисторов 7 ,многопороговый д: ;искриминатор 8, состоящий из однопороговых дискриминаторов на транзисторах 9-16, резисторов 17-22 и резистивный делитель из суммирующих резисторов 23-26. Каждая пара диодов 2 и 3 линейного сумматора в точках, объединяющих их аноды .через резисторы, определяющие вес входов,подключена к положительному полюсу источника питания 27. Катоды диодов 3 объединены и подсоединены ко входу резисторного делителя из резисторов 23-26, выходы которого соединены со входами однопороговых дискриминаторов на транзисто.рах 9,12,10,13,11, .14 и 15. . Катоды диодов 2 каждой пары входов 29 линейного сумматора 1 соединены с э-миттерами мцогоэмиттерного транзистора 5, база которого через резистор 7 подсоединена к положительному полюсу источника питания 27, а коллектор подключен к базе многоколлекторного транзистора 6. Эмиттер многоколлекторного транзистора 6 подсоединен к отрицательному полюсу 28 источника питания, а коллекторы соединены соответственно с точками объединения анодов дио;дов 2 и 3 первого и втсрого входов соответствующей пары входов линейного сумматора. База транзистора 16 подключена к коллектору транзистора 12, принадлежащего однопороговому дискрилшнатору с наименьшим порогом срабатывания. Коллектор транзис.тора 16 подключен к выходной клемме 30 многопорогового элемента. Транзисторы 9-11 развязывают между собой дискриминаторы с последовательными порогами срабатывания. Базы транзисторов 9-11 и 16 через резисторы 17-20 подключены к положительному полюсу источника питания 27. Коллектор транзистора 16 через резистор 21 также подключен к положительному полюсу источника питания 27, Работает многопороговый логический элемент следующим образом. Пусть элемент имеет восемь входов. Значения весовых коэффициентов входов линейного сумматора равны единице. Пороги срабатывания дискриминаторов на транзисторах 9,12,10, 13,11,14 и 15 соответственно равны 1-4. В исходном состоянии (все входные переменные равны нулю) диоды 2, связанные со входами 29, проводятток от источника питания через резисторы 4. Потенциал на выходе линейного сумматора 1 недостаточен для срабатывания дискриминаторов на транзисторах 9 и 12. Транзистор 9 является открытым, что приводит к появлению низкого уровня напряжения на базе транзистора 12, и он закрывается. На выходе 30 многопороговог логического элемента устанавливаетс низкий уровень напряжения, соответсвующий О .

Если положительный потен1Диал присутствует только на одном из входов линейного сумматора 1, то соответствующий диод 2 запирается и ток от источника питания через соответс вующий резистор 4 переключается в цепь резисторов 23-26. При этом все многоколлекторные транзисторы 6 являются закрытыми, поскольку у любого из многоэмиттерных транзисторов 5 хотя бы один из эмиттеров находится под низким уровнем напряжения. На выходе линейного сумматора 15- в этом случае присутствует уровень напряжения, достаточный для срабатывания дискриминатора на транзисторах 9 и 12. При этом транзистор 9 закрывается, на его коллекторе устанавливается высокий потенциал, приводящий к открыванию транзистора 12 и закрыванию транзистора 16. На клемме 3Q формируется высокий уровень напряжения, соответс вующий единичному значению логической функции.

Пусть теперь две выходные переменные многопорогового логического элемента равны единице и они поступают в клеммы 29, относящиеся JC различным парам входов линейного сумматора. Соответствующие диоды 2 запираются и ток от источника питания через соответст вующие резисторы 4 и диоды 3 пост пает в цепь резисторов 23-26. Пос-КОЛЬКУ все многоколлекторные транзисторы в этом случае явля тся закрытыми, то тока, протекающв г через резисторы 23-26, достаточно для появления потенциала, вызываняцего срабатывание дискриминаторов на транзисторах 9,12,10 и 13. Поскольку транзистор 13 дискриминатора с порогом срабатывания 2 при этом открывается, то потенциал на его коллекторе уменьшается, что приводит к закрыванию транзистора 12 и открыванию транзистора 16. На выходе 30 в этом случае формируется нулевое значение логической функции.

Если две входные переменные . многопорогового логического элемент равны единице и поступают на клеммы 29, относящиеся к одной паре входов линейного сумматора, то на обоих эмиттерах соответствующего многоэмиттерного транзистора 5 присутст вует высокий уровень напряжения .Базовый ток этого транзистора переключается в цепь коллектора и поступает в базы многоколлекторного транзисто5 ра 6. Соответствующий многоколлекторный транзистор открывается и токи через связанные с его коллекторами резисторы 4 поступают к отрицательному полюсу источника питания 29 г 10 минуя делитель из резисторов 23-26. Потенциала на выходе линейного сумматора 1 становится недостаточно для срабатывания дискриминатора на транзисторах 9 и 12. На выходе 30 много5 порогового логического элемента формируется нулевое значение логической функции.

Если на клеммы 29, принадлежащие различным парам входов линейного

0 сумматора 1, поступает три или четыре входные переменные, равные единице, то соответствующие входные диодй 2 закрываются, ток от положительного полюса источника питания через ре5 зисторы 4 поступает в цепь из резисторов 23-26. При этом срабатывают дискриминаторы на транзисторах 9,12,10,13, 11 и 14 или 9,12,10,13, 11, 14 и 15 и на выходе 30 соответственно формируется единичное или

нулевое значение логической функции.

Аналогичным образом происходит работа многопорогового логического элемента при других комбинациях входных сигналов. Opji этом всегда

5 следует учитывать, что единичные значения переменных, поступающие в клеммы 29, принадлежащие к одной паре входов линейного сумматора, приводят к открыванию транзистора 6, кол0 лекторы которого соединены с анодами диодов 2 и 3 соответствующей пары входов. В этом случае ток от положительного полюса источника питания 127 через резисторы 4 и открытый

5 многоколлекторный транзистор 6 поступает к отрицательному полюсу источника питания 28, минуя цепь резисторного делителя из резисторов 23-г26. Следовательно, максимальное

Q значение тока в цепи резисторов 23-26 будет протекать при поступлении на клеммы 29, принадлежащие различным парам входов линейного сумматора, четырех переменных, равных единице Максимальное значение

5 порога (и количество однопороговых дискриминаторов) многопорогового логического элемента четности равно числу, пар входов ликейного сумматора.

0 Указанные изменения в структуре . многопороговог.о логического элемента позволяют повысить его технологичность за счет уменьшения числа высокоточных резисторов. Уменьшается число однопороговых дискрими$11323666

наторов (при заданном числе входов),элемента, поскольку при максимальчто приводит к .уменьшению временином значении порога, равном

задержки сигнала.восьми, он позволяет реалиэоКроме того, расширяются функцио--вать функцию четности от аргунальные возможности предложенногоментов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Многопороговый логический элемент | 1982 |

|

SU1042183A1 |

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

| Многопороговый логический элемент | 1975 |

|

SU573883A1 |

| Многопороговый логический элемент | 1979 |

|

SU790341A1 |

| Многопороговый логический элемент | 1984 |

|

SU1223359A1 |

| Многопороговый логический элемент четности | 1977 |

|

SU660261A2 |

| Многопороговый логический элемент | 1979 |

|

SU788384A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1971 |

|

SU319077A1 |

| Многопороговый логический элемент четности | 1976 |

|

SU608266A1 |

МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ по авт.св. 319077, отличаю щийс я тем, что, с целью расширения функциональных возможностей за счет увеличения количества входив, в него введены для каждой пары входов линейного сумматора многоколлекторный и многоэмит27 25о терный транзисторы и дополнительный резистор, включенный между положительным полюсом источника питания и базой многоэмиттерного транзистора, один эмиттер которого соединен с первым входом, а другой - со вторым входом соответствующей пары входов линейного сумматора, коллектор многоэмиттерного транзистора подключен к базе многоколлекторногр транзистора, эмиттер которого соединен с отрицательным полюсом источника питания, один коллектор подключен к анодс1М диодов первого входа, второй коллектор соединен с анодами диодов второго входа соответствующей пары входов линейного сумматора. :о о :о 35 з:

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-12-30—Публикация

1983-05-20—Подача