и -i 3 - соответствующие пороги многопорогового логического элемента, конечные вещественные числа.

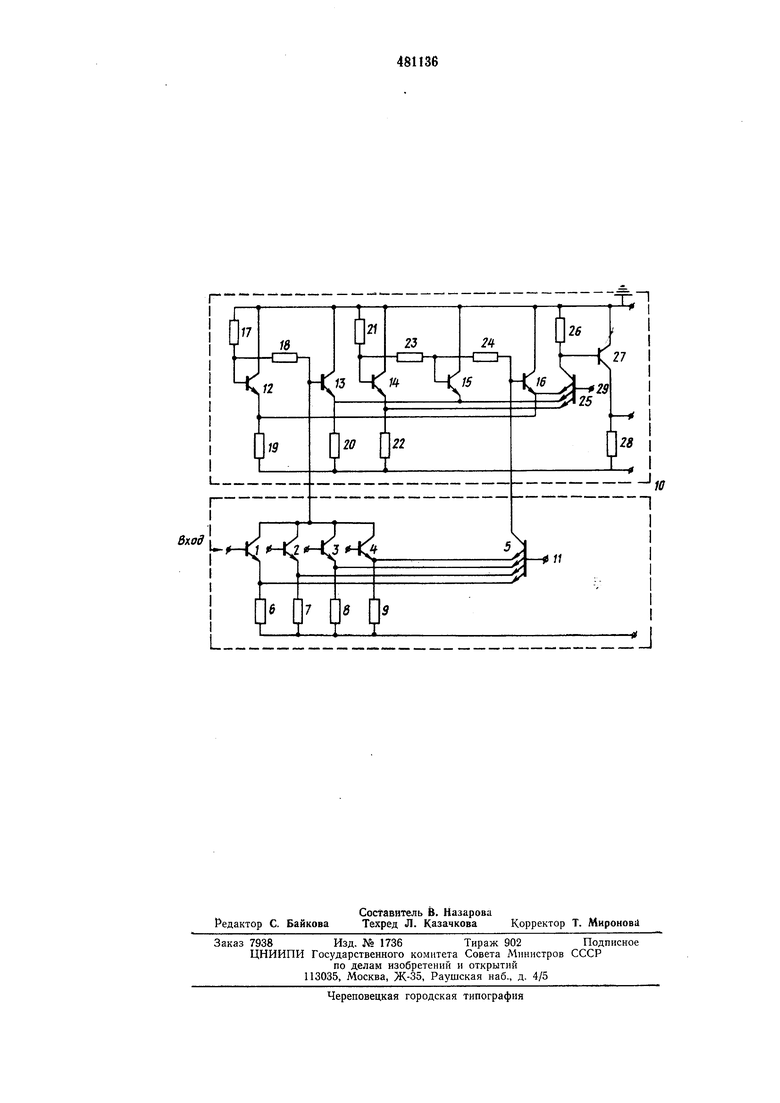

Многопороговый логический элемент состоит из линейного сумматора, выполненного на четырех входных транзисторах 1-4, опорном четырех эмиттерном транзисторе 5, «весовых резисторах 6-9, источниках напряжения 10 и 11, и многопорогового дискриминатора, выполненного на переключателях тока на пяти транзисторах 12-16, включенных по схеме с общим коллектором, и резисторах 17-24, схеме совпадения на многоэмиттерном транзисторе 25 и резисторе 26, выходного э иттерного повторителя па транзисторе 27, резисторе 28, и источпика напряжения 29.

Многонороговый логический элемент работает следующим образом.

В исходном состоянии транзисторы 1, 2, 3, 4, 14, 15, 16 выключены, а транзисторы 12 и 13 и многоэмиттерные транзисторы 5 и 25 включены. На выходе элемента - уровень логического нуля.

Рассмотрим для примера работу пятипорогового логического элемента с «весами входов (1, 1, 2, 2) и «порогами 1, 3, 4, 5, 6. Относительный «вес входа 2 означает, что сопротивление соответствующего резистора в два раза меньще сопротивления резистора на входе с «весом 1.

У выходного транзистора 25 схемы совпадения проводит только эмиттер, связанный с эмиттером транзистора 14, срабатывающего па минимальный «порог 2. Входные двоичные сигналы, поступая на базы входных транзисторов 1, 2, 3, 4 изменяют потенциалы на базах транзисторов 12, 13, 14, 15, 16 в многопороговом дискриминаторе. Если «весовая

ип

сумма включенных входов 2 , 1- 3, то транзистор 14 включается, выключая транзистор 25 схемы совпадения п устанавливая lia выходе элемента .чогическук) единицу п

Если 3-С У аУ;-у; 4, то транзистор 14 включается, а транзистор 13 выключается п па выходе - -- уровень логического нуля.

II

Если 4 , то транзистор 14 включается, транзистор 13 выключается, по включается транзистор 15 и па выходе - уровень логической едппицы. II

Если ,, то транзисторы 14 п 15 включаются, транзистор 12 п 13 выключаются, на выходе - логический «О.

Если X i У 6, то трапзисторы 14, 15, 16 включаются, транзисторы 12 и 13 выключаются, транзистор 25 схемы совпадения выключен и на выходе - логическая единица.

Таким образом элемент вьшолняет пятипороговую логическую фупкцию. Использование многопороговых логических элементов при построении логических устройств позволяет в несколько раз повыспть быстродействие всего логического устройства и сократить оборудование по сравнению с аналогичными логическими устройствам) на однопороговых логических элементах.

Схема содержит компонеиты, легко реализуемые монолитной интегральной технологией и не требует жестких допусков к напряжению питания и параметрам компонентов. В интегральных схемах заданные отнощения резисторов легко выдержать с точностью ±2% и даже лучщей, при таких допусках нетрудно получить четырех и пятипороговые логические элемепты. Схема обладает наибольщим быстродействием по сравнению с известными в виду возможности работы транзисторов в ненасыщенном режиме.

Предмет изобретения

Многопороговый логический элемент, содержащий линейный сумматор с парафазным выходом и многопороговый дискриминатор, отличающийся тем, что, с целью повыщения быстродействия, многопороговый дискриминатор состоит из переключателей тока на пяти транзисторах, включенных по схеме с общим коллектором, и схемы совпадения на многоэмиттерном транзисторе, к одному из эмиттеров которого подсоединен эмиттер третьего транзистора переключателя тока, а к остальным его эмиттерам подсоединены попарно соединенные эмиттеры первого и пятого, второго и четвертого транзисторов переключателей тока, причем базы первого п второго транзисторов подсоединены к прямому выходу вышеупомянутого лннейиого сумматора, состояП1,его нз четырех входных транзисторов, эмиттеры которых соединены соответственно с эмиттерамн четырехэмиттерного транзистора с резистпвным делителем напряжения в качестве его коллекторной нагрузки, средние выводы которого соединены соответственно с базами третьего, четвертого и пятого транзисторов многопорогового дискриминатора, коллектор мпогоэмнттерного транзистора которого соединен с базой выходного эмиттерного повторителя.

ймд

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многопороговый логический элемент | 1982 |

|

SU1042183A1 |

| Многопороговый логический элемент | 1975 |

|

SU573883A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1971 |

|

SU319077A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| ТТЛ-элемент | 1985 |

|

SU1277382A1 |

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1970 |

|

SU266837A1 |

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

| Логический элемент | 1983 |

|

SU1166296A1 |

| Многопороговый логический элемент | 1979 |

|

SU790341A1 |

Авторы

Даты

1975-08-15—Публикация

1972-10-04—Подача