i

Изобретение относится к логическим устройствам, применяемым в вычислительной технике и автоматике.

Известны универсальные триггеры, содержащие входной и выходной вентили «И-НЕ по схеме многоэмиттерной транзисторнотранзисторной логики.

Предлагаемый триггер отличается от известных тем, что в него введен пороговый логический элемент, содержащий дискриминатор и диодно-резистивный линейный сумматор, в котором вывод каждого весового резистора через диод подключен к выводу суммирующего резистора и ко входу дискриминатора, соединенного своим выходом со входом выходного вентиля «И-НЕ и через диод - с выводом первого весового резистора и выходом входного вентиля «И-НЕ, у которого два эмиттера многоэмиттерного транзистора подключены через диоды к выводу второго весового резистора и соответственно к первой информационной шине и шине синхронизации, при этом вторая информационная шина соединена через диод с выводом третьего весового резистора.

Эти отличия позволяют повысить надежность и увеличить быстродействие устройства.

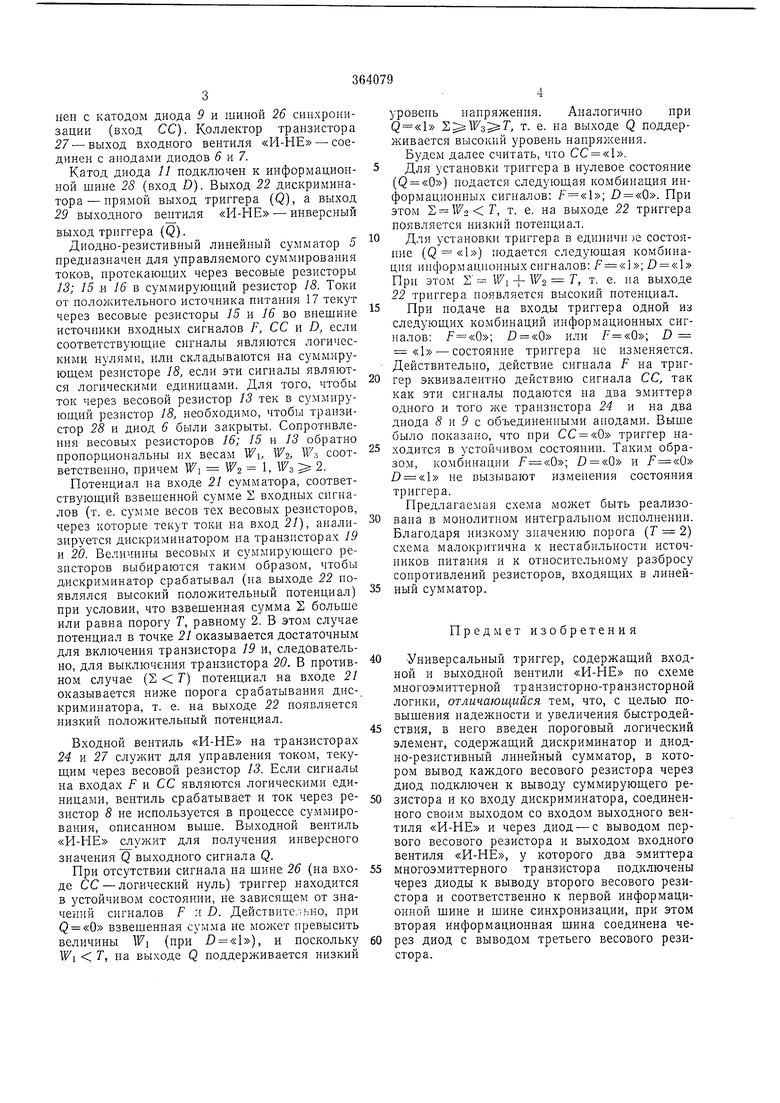

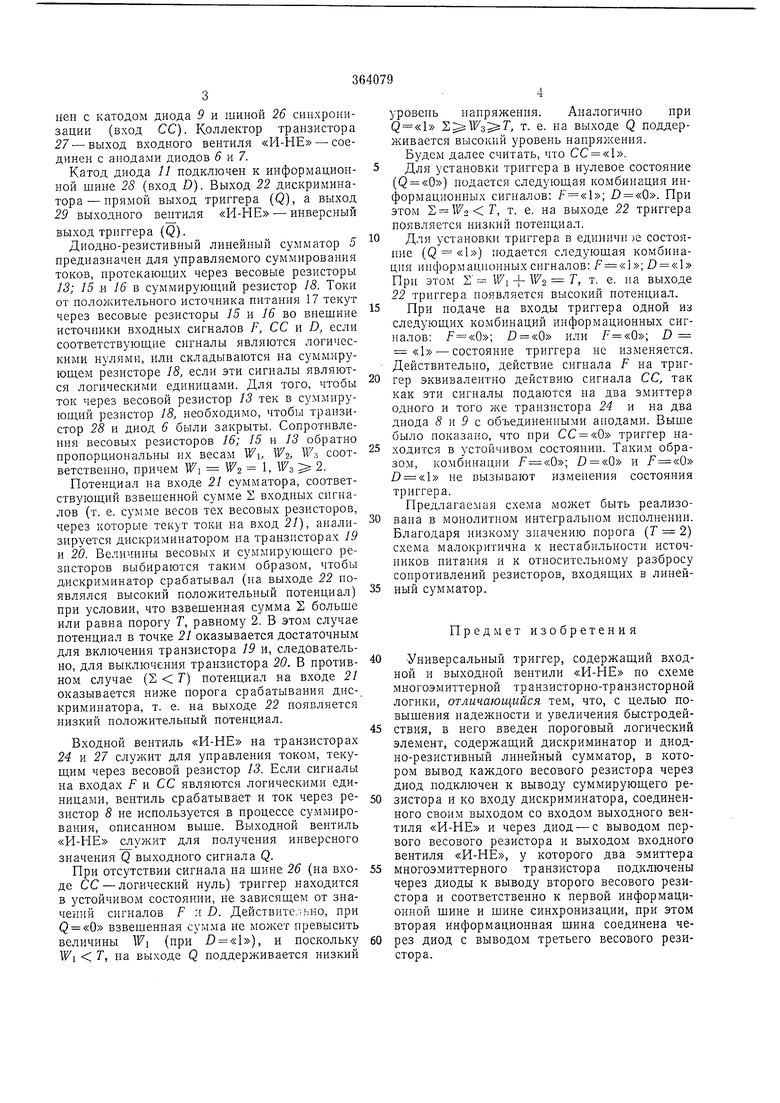

На чертеже изображена схема предлагаемого универсального триггера.

Универсальный триггер содерлсит входной вентиль «И-НЕ /, выходной вентиль «И-НЕ 2, пороговый логический элемент 3, состоящий из дискриминатора 4 и диодно-резистивного линейного сумматора 5.

Диодно-резистивный линейный сумматор 5 содержит три группы диодов 6 и 7; 8, 9 п 10; 11 и 12 с объединенными анодами. Точка соединения анодов диодов 6 н 7 соединена через

весовой резистор 13 с положительным источником питания 14. Точки объединения анодов диодов 8; 9 и 10; 11 и 12 соединены через соответствующие весовые резисторы 15 и 16 с положительным источником питания 17.

Катоды диодов 7; 10 и 12 объединены и через сзммирующий резистор 18 соединены с «земляной шиной.

Дискриминатор 4 выполнен на двух последовательно включенных транзисторах 19; 20

с общим эмиттером. База первого транзистора 19 подключена ко входу 21 дискриминатора. Коллектор транзистора 20 соединен с выходом 22 дискриминатора, катодом диода 6, входом 23 выходного вентиля «И-НЕ 2.

Входной вентиль «И-НЕ / выполнен по схеме .многоэмиттерной транзисторно-транзисторной логики. Первый эмиттер многоэмиттерного транзистора 24 соединен с катодом диода 8 и информационной шиной 25 (вход

Р, второй эмиттер этого транзистора соедииен с катодом диода 9 и шиной 26 синхронизации (вход СС). Коллектор транзистора 27 - выход входного вентиля «И-НЕ - соединен с анодами диодов 6 и 7. Катод диода 11 подключен к информационной шине 28 (вход D). Выход 22 дискриминатора- прямой выход триггера (Q), а выход 29 выходного вентиля «И-НЕ - инверсный выход триггера (Q). Диодно-резистивный линейный сумматор 5 предназначен для управляемого суммирования токов, протекаюш,их через весовые резисторы 13; 15 и 16 в суммирующий резистор 18. Токи от положительного источника питания 17 текут через весовые резисторы 15 и 16 во внешние источники входных сигналов F, СС и Д если соответствуюш.ие сигналы являются логическими нулями, или складываются на суммируюш,ем резисторе 18, если эти сигналы являются логическими единицами. Для того, чтобы ток через весовой резистор /5 тек в суммирующий резистор 18, необходимо, чтобы транзистор 28 и диод 6 были закрыты. Сопротивления весовых резисторов 16; 15 и 13 обратно пропорциональны их весам Wi, W, W COOTветственно, причем Wi W2 - 1, Wz 2. Потенциал на входе 21 сумматора, соответствующий взвешенной сумме S входных сигналов (т. е. сумме весов тех весовых резисторов, через которые текут токи на вход 21), анализируется диcкpигvIинaтopoм на транзисторах 19 и 20. Величины весовых и суммирующего резисторов выбираются таким образом, чтобы дискриминатор срабатывал (на выходе 22 появлялся высокий положительный потенциал) при условии, что взвешенная сумма Б больше или равна порогу Т, равному 2. В этом случае потенциал в точке 21 оказывается достаточным для включения транзистора 19 и, следовательно, для выключения транзистора 20. В противном случае (Е Т) потенциал на входе 21 оказывается ниже порога срабатывания дискриминатора, т. е. на выходе 22 появляется низкий положительный потенциал. Входной вентиль «И-НЕ на транзисторах 24 и 27 служит для управления током, текущим через весовой резистор 13. Если сигналы на входах F и СС являются логическими единицами, вентиль срабатывает и ток через резистор 8 не используется в процессе суммирования, описанном выше. Выходной вентиль «И-НЕ служит для получения инверсного значения Q выходного сигнала Q. Ири отсутствии сигнала на шине 26 (на входе СС - логический нуль) триггер находится в устойчивом состоянии, не зависящем от значений сигналов F м D. Действительно, при Q «0 взвешенная сумма не может превысить величины Wi (при «1), и поскольку Wi Т, на выходе Q поддерживается низкий уровень напряжения. Аналогично при Q «l I., т. е. на выходе Q поддерживается высокий уровень напряжения. Будем далее считать, что СС «1. Для установки триггера в нулевое состояние (Q «0) подается следующая комбинация информационных сигналов: D «0. При этом Е , т. е. на выходе 22 триггера ноявляется низкий поте1щиал. Для установки триггера в единичн зе состояние (Q «l) подается следующая комбинация информационных сигналов: F D « При этом S-- Wi-}-W2 T, т. е. на выходе 22 триггера появляется высокий потенциал. При подаче на входы триггера одной из следующих комбинаций информационных сигналов: D «0 или F «Q D «1 - состояние триггера не изменяется. Действительно, действие сигнала F на триггер эквивалентно действию сигнала СС, так как эти сигналы подаются на два эмиттера одного и того же траизистора 24 и на два диода 8 и 9 с объединенными анодами. Выше было показано, что при СС «0 триггер находится в устойчивом состоянии. Таким образом, комбинации D «0 и D « не вызывают изменения состояния триггера. Предлагаемая схема может быть реализована в монолитном интегрально.м исполнении. Благодаря низкому значению порога (Т 2) схема малокритична к нестабильности источников питания и к относительному разбросу сопротивлений резисторов, входящих в линейный сумматор. Предмет изобретения Универсальный триггер, содержащий входной и выходной вентили «И-НЕ по схеме многоэмиттерной транзисторно-транзисторной логики, отличающийся тем, что, с целью повышения надежности и увеличения быстродействия, в него введен пороговый логический элемент, содержащий дискриминатор и диодно-резистнвный линейный сумматор, в котором вывод каждого весового резистора через днод подключен к выводу суммирующего резистора и ко входу дискриминатора, соединенного своим выходом со входом выходного вентиля «И-НЕ и через диод--с выводом первого весового резистора и выходом входного вентиля «И-НЕ, у которого два эмиттера многоэмиттерного транзистора подключены через диоды к выводу второго весового резистора и соответственно к первой информационной щнне и щине синхронизации, при этом вторая информационная щина соединена через диод с выводом третьего весового резистора.

СС о

2в1

Авторы

Даты

1973-01-01—Публикация