Известны устройства для генерацип кода постоянного веса, содержащие регистры и логические схемы.

Предлагаемое устройство отличается тем, что в нем установлены блок выделения граничного разряда иреобразуемой части кодовой комбинации и блок преобразования правой части кодовой комбииапии, выходы которого подключены к счетным входам триггеров запоминающего регистра, нулевые и единичные выходы триггеров запоминающего регистра подсоединепы к одной группе входов блока преобразования правой частп кодовой комбинации и ко входам блока выделения граничного разряда преобразуемой части кодовой комбинации, выходы которого соединены с другой группой входов блока преобразования правой части кодовой комбииацпи. Это позволяет сократить оборудование устройства.

Кроме того, для уирощения блока выделения грапичного разряда преобразуемой части кодовой комбинапии выходы триггеров г-го и (t-|-l)-ro разрядов заиоминающего регистра подсоединены к первым и вторым входам логических узлов г-го разряда блока выделения граничного разряда преобразуемой части кодовой комбинации, а выход логического узла i-ro разряда блока выделения граничного разряда преобразуемой части кодовой комбинации подключен к третьему входу логического узла (/-1)-го разряда блока выделения граничного разряда преобразуемой части кодовой комбинацни.

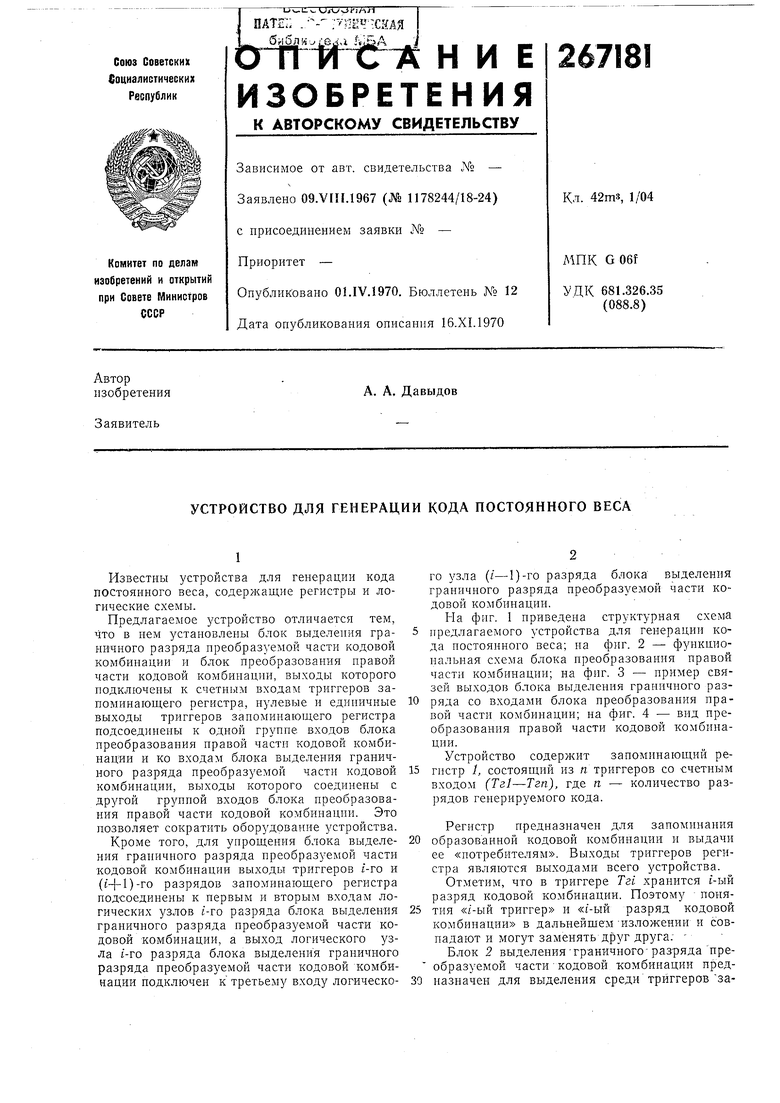

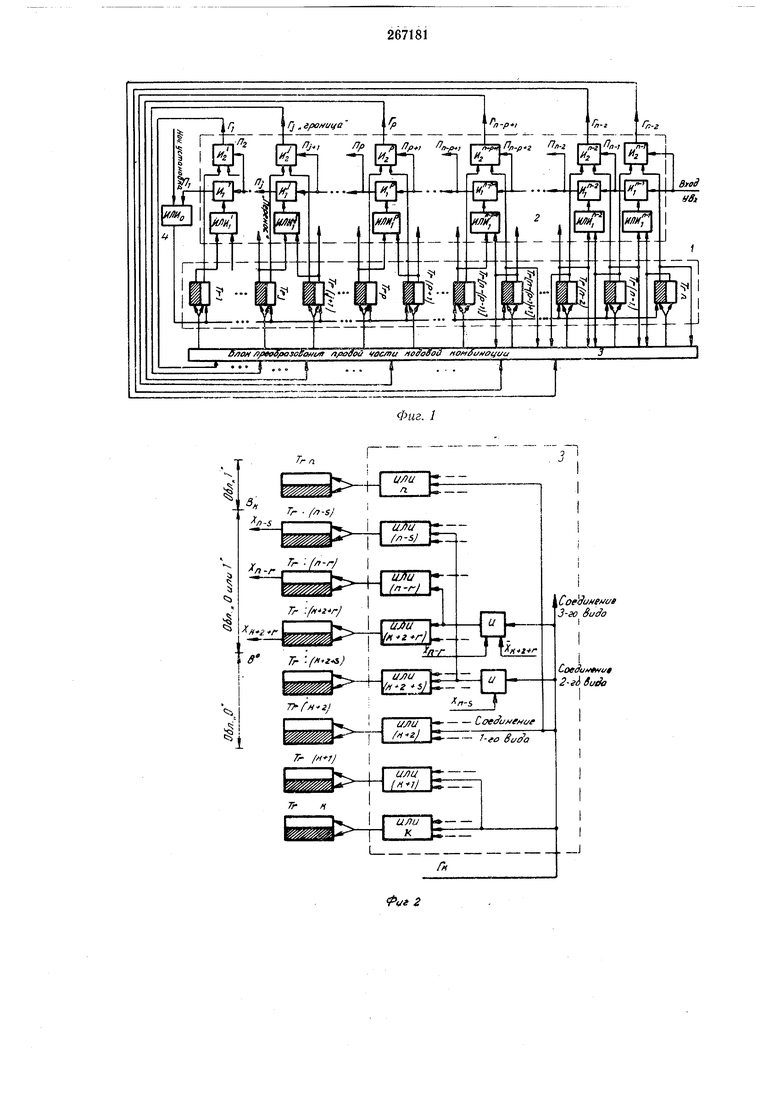

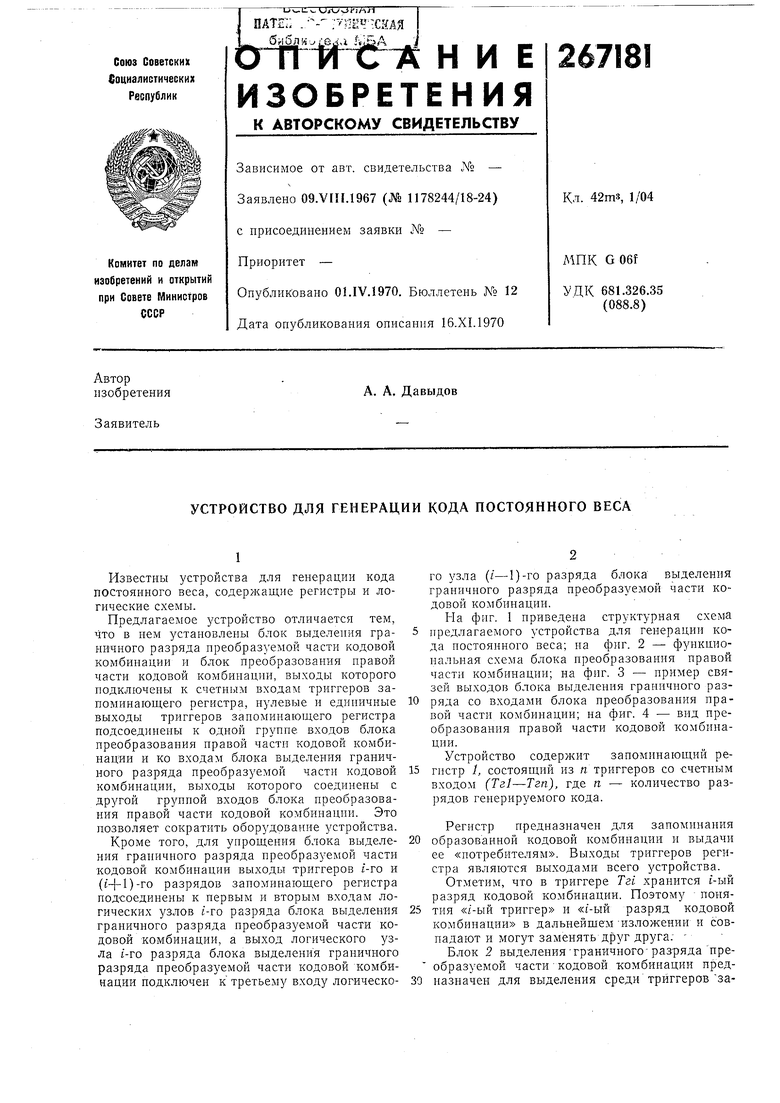

На фиг. 1 приведена структурная схема

предлагаемого устройства для генерации кода постоянного веса; па фиг. 2 - функпиопальпая схема блока преобразования правой части комбинации; на фиг. 3 - пример связей выходов блока выделения граничного разряда со входами блока иреобразования правой части комбинации; на фиг. 4 - вид преобразовання правой частп кодовой комбипации. Устройство содержит запоминающий регпстр /, состоящий из п триггеров со счетным входом (Тг1-Тгп), где п - количество разрядов геиерируемого кода.

Регистр предназпачеп для запомипапия образованной кодовой комбинации и выдачи ее «потребителям. Выходы триггеров регистра являются выходами всего устройства.

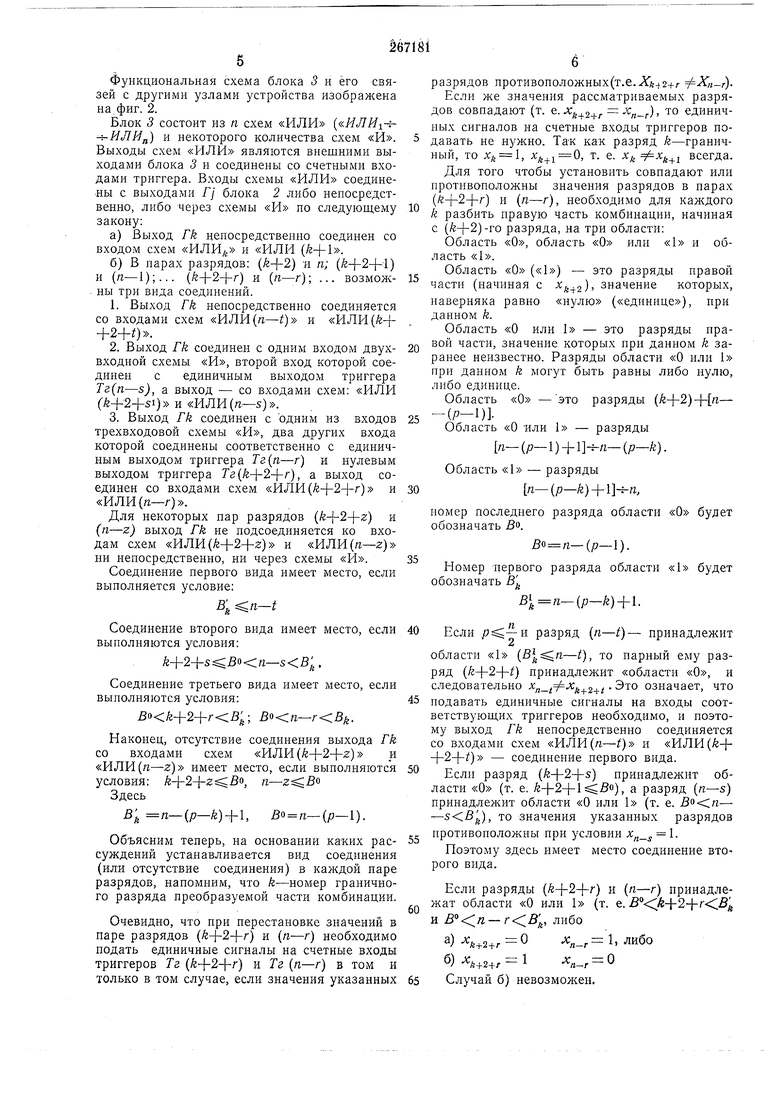

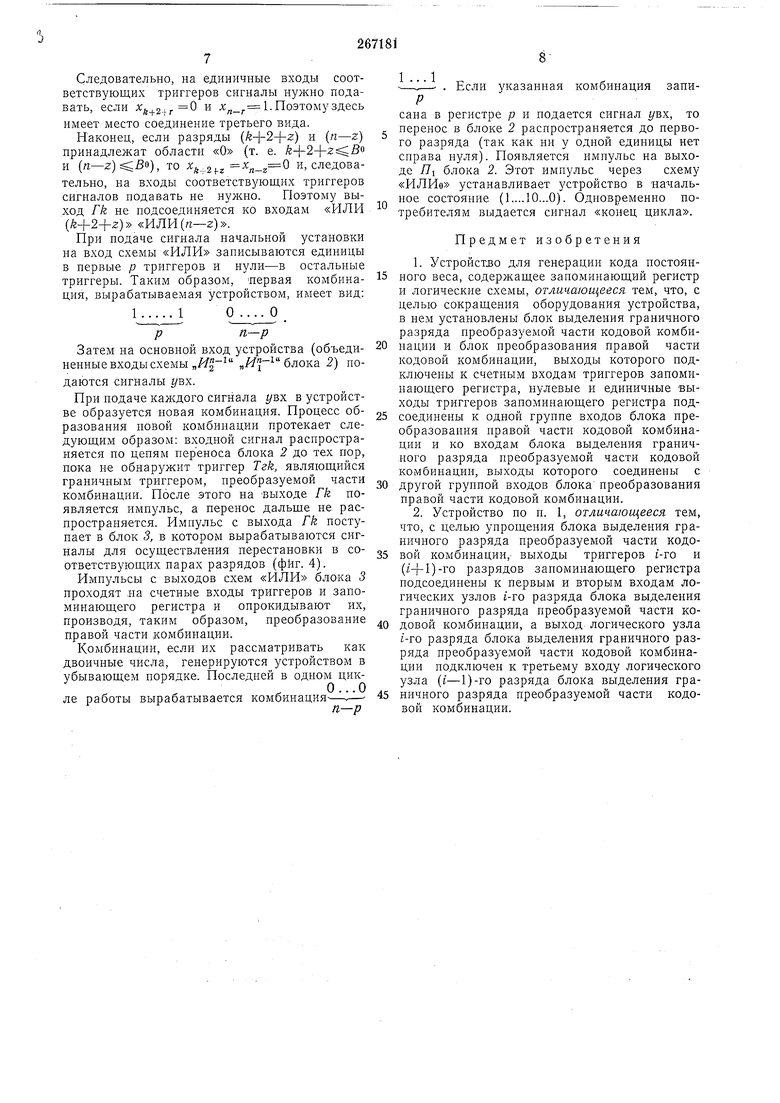

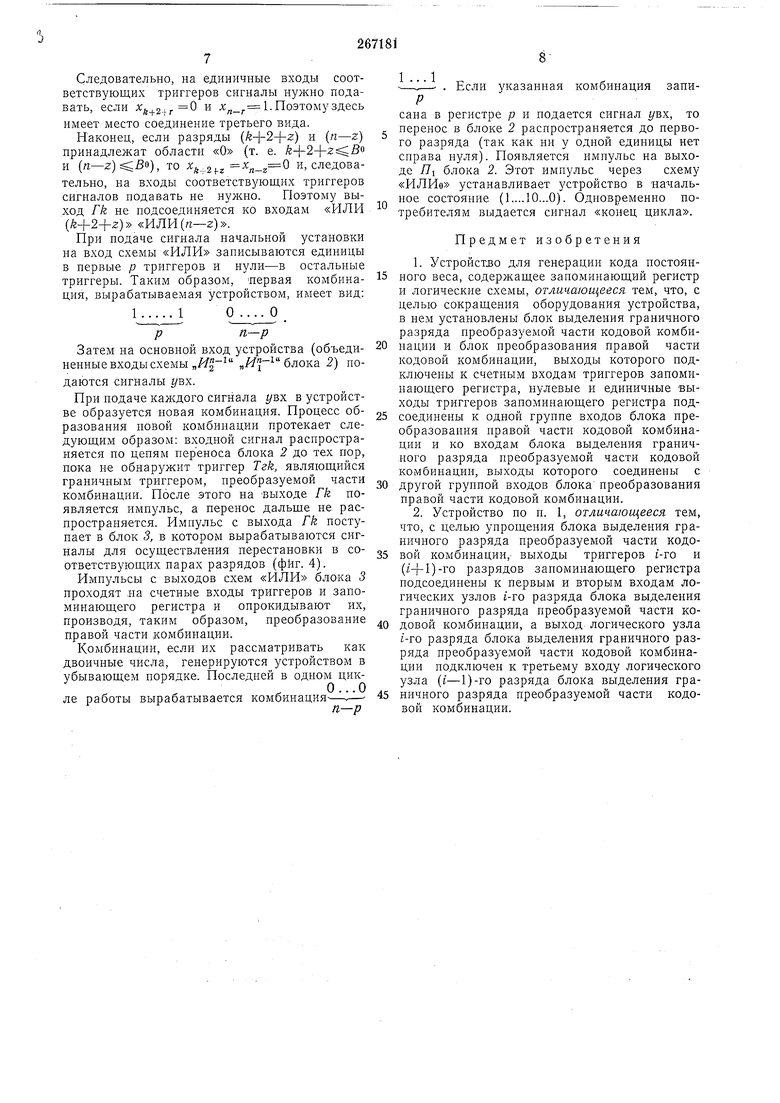

Отметим, что в триггере Tei хранится t-ый разряд кодовой комбинации. Поэтому понятия «/-ый триггер и «t-ый разряд кодовой комбинации в дальнейщем -изложении и совпадают и могут заменять друг друга: поминающего регистра такого триггера ТгН, который удовлетворяет условиям: а)триггер Tak находится в состоянии «один, б)триггер Тг (k-{-) находится в состоянии «ноль, в)среди триггеров T3((n) нет ни одной пары триггеров, удовлетворяющих первым двум условиям. Так как нумерация разрядов установлена слева направо, то триггер Тгп, удовлетворяющий всем условиям, будем называть «триггером, содержащим самую правую «единицу, справа от которой есть «ноль. Этот триггер разделяет комбинацию на две части. Левую (разряды l-f-й-1) и правую (разряды ). При этом правая часть преобразуется при переходе к следующей комбинации, а левая часть не преобразуется. Поэтому триггер Tzk, удовлетворяющий всем условиям, будем называть также «граничным триггером преобразуемой части комбинации. Блок 2 состоит из логических схем «И, «ИЛИ и имеет п выходов, обозначенных . Блок 3 иреобразования правой части комбинации предназиачен для вырабатывания сигналов, производящих изменения состояния триггеров по следующему закону. При переходе к следующей комбинации переставляются состояния в иарах триггеров: а)Tzk и Гг(+1); б)Тг() и Тгп; Тг (й+2+1) и Тг(п- ГгГй+2+г) и Тг(п-г} (см. фиг. 4). Здесь k-номер граничного триггера преобразуемой части комбинации. Под термином перестановка состояний в паре триггеров Тг1 и Тгх ионимается следующее: после преобразования триггер Тг1 устанавливается в то состояние, в котором до преобразования был триггер Тгг; в свою очередь, триггер Тгг устанавливается в то состояиие, в котором до преобразования был триггер Тг1. Аналогично ионимается термин «перестановка значений в паре разрядов. Блок 3 состоит из логических схем «И, «ИЛИ и имеет п выходов. Логическая схема 4 предназначена для установки триггеров регистра в начальное состояние. Выходы Г)-7-Г„ г блока 2 соединены со входами блока 3, а выход П блока 2 соединен со входом схемы 4 , второй вход которой является входом установки устройства в начальное состояние. Основной вход устройства, на который подается сигнал z/Bx: «образовать новую комбинацию, является одним из входов блока 2. Выходы триггеров регистра соединены со входами блоков 2 и 3, а выходы блока -3 - со входами триггеров. Как видно из фиг. 1, выходы всех триггеров регистра соедииены со входами блока 2, а выходы последних триггеров ( соединены со входами блока 3. (р-вес кода, равный количеству единиц в кодовой комбинации). Выходы блока 5 соединены со счетными входами триггеров. Выход схемы 4 «ИЛИп соединен со входами установки единицы первых р триггеров Тг1-г-Тгр и со входами установки нуля осальных триггеров Тг()7-Тгп. Как видно из фиг. 1 блок 2 построен по принципу сквозного переноса и состоит из (п-1) разрядов. Каждый разряд блока 2 представляет собой логическую схему с двумя выходами состоит из двух схем «И (Я/, //|) и одиой схемы «ИЛИ (ИЛИ{, где /-номер разряда. Один выход /-ГО разряда обозначенный Гj, является внещним выходом блока 2 («внещним в том смысле, что он соединеи с другими узлами устройства). Второй выход /-ГО разряда, обозначенный Hj при является внутренним выходом переноса в (/-1)-ый разряд. Если , то /7i является внещним выходом блока 2, на котором образуется сигнал «конец цикла, означающий, что все комбинации кода прогенерированы. Опищем связи в блоке 2. Если , то входы трехвходовой схемы //I соедииены с единичным выходом триггера Те , нулевым выходом триггера Гг(/-|-1) и выходом переиоса (/-|-1)-го разряда блока 2/7/-(-1. Выход схемы «И является выходом Г/. Входы схемы «ИЛИ{у соединены с нулевым выходом триггера Tej и единичным выходом триггера Te(), а выход этой схемы соединен со входом схемы «И. Второй вход схемы «Я/ соединен с выходом переноса (/+1)-го разряда (Я/4-1). Выход схемы Я/ является выходом Я/. Если , то роль переноса из старщего разряда играет входной снгиал устройства г/вх. Входы схемы «Щ , объединены и являются входом всего устройства. Появление единицы на выходе Г/г означает, что триггер Tek является граничн1 1м триггером преобраз емой части комбинации. Поэтому выходы Г/-названы «граница. В целом блок 2 представляет собой логическую схему с п выходами: П Г - Гп-гЕсли i/Bx l и граничный разояд имеет номер k, то rk. , Г1 Г2 ...rk- ....

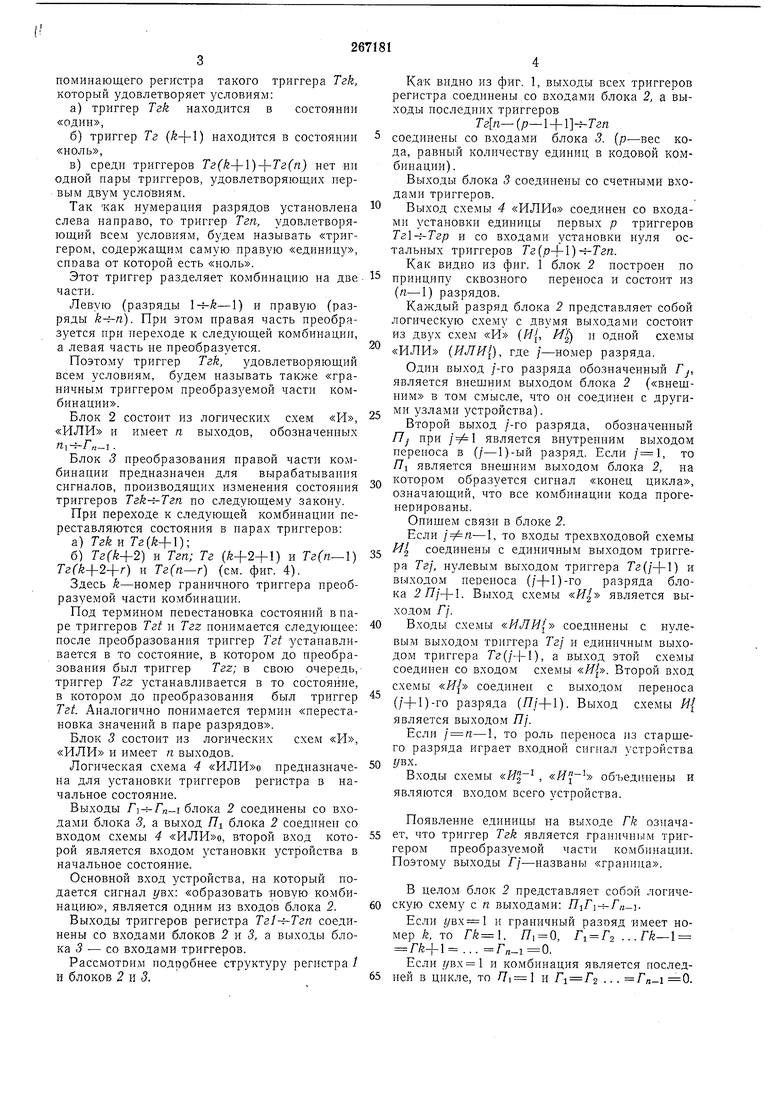

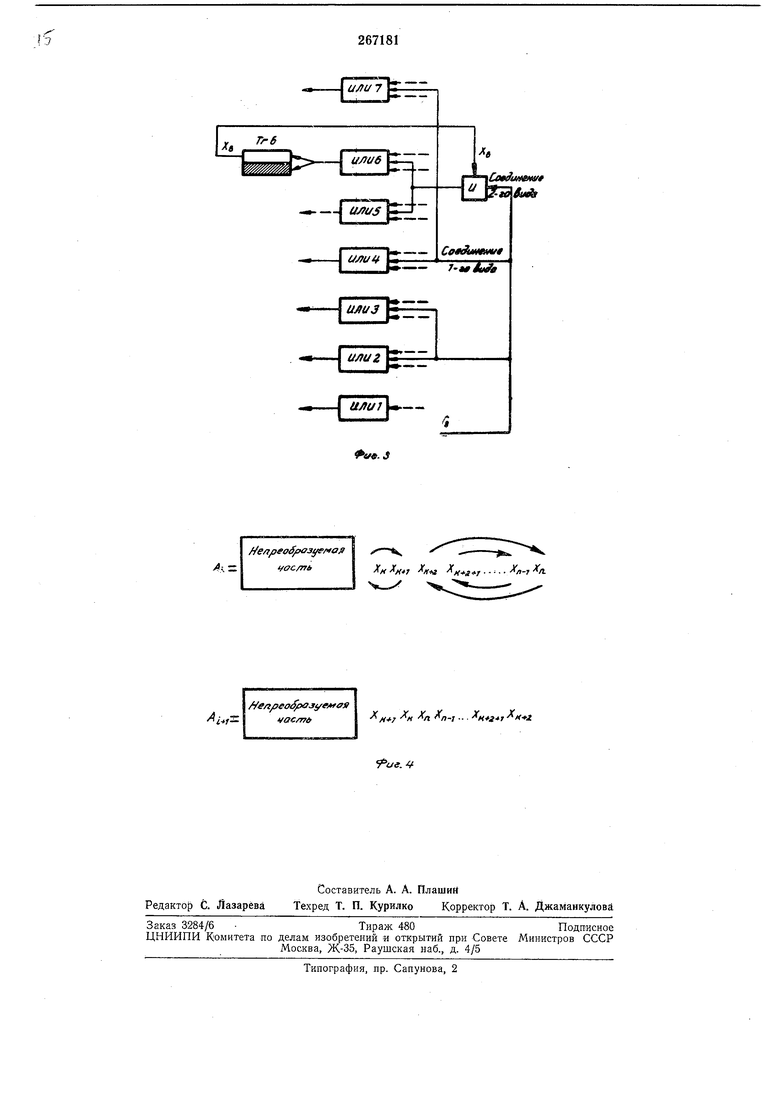

Функциональная схема блока 5 и его связей с другими узлами устройства изобрал ена на фиг. 2.

БлоК 5 состоит из п схем «ИЛИ («ИЛИ -г- -ИЛИ„) и некоторого количества схем «И. Выходы схем «ИЛИ являются внешними выходами блока 3 и соединены со счетными входами триггера. Входы схемы «ИЛИ соединены с выходами Г/ блока 2 либо непосредственно, либо через схемы «И по следующему закону:

а)Выход fk непосредственно соединен со входом схем «ИЛИ. и «ИЛИ (.

б)В нарах разрядов: (k-{-2) и «; (fe-j-2-j-l) и (л-1);... ) и (п.-г); ... возмол ны три вида соединений.

1.Выход rk непосредственно соединяется со входами схем «ИЛИ(п-t) и «ИЛИ(-|+2+0.

2.Выход Fk соединен с одним входом двухвходной схемы «И, второй вход которой соединен с единичным выходом триггера Тг(п-s), а выход - со входами схем: «ИЛИ (й+2+si) и «ИЛИ (n-s).

3.Выход Fk соединен с одним из входов трехвходовой схемы «И, два других входа которой соедииены соответственно с единичным выходом триггера Тг(п-г) и нулевым выходом триггера Ta{k- -2-}-r}, а выход соединен со входами схем «ИЛИ(&+2+г) и «ИЛИ{п-г).

Для некоторых пар разрядов (й+2+2) и (п-г) выход Fk не подсоединяется ко входам схем «ИЛИ(й+2+2) и «ИЛИ («-2) нн иепосредственно, ни через схемы «И.

Соединение первого вида имеет место, если выполняется условие:

В n-t

Соединение второго вида имеет место, если выполняются условия:

A+2+s 5o rt-s S,

Соединение третьего вида имеет место, если выполняются условия:

5о +2+/- 5 ; .

Наконец, отсутствие соединения выхода Fk со входами схем «ИЛИ(А+2+2) и «ИЛИ(п-2) имеет место, если выполняются условия: ,

Здесь

В /г(р-й) + 1, Во п-(р-).

Объясним теперь, на основании каких рассуждений устанавливается вид соединения (или отсутствие соединения) в паре разрядов, напомним, что k-номер граничного разряда преобразуемой части комбинации.

Очевидно, что при перестановке значений в паре разрядов (й+2+r) и (я-г) необходимо подать единичные сигналы на счетные входы триггеров Тг (+2+г) и Те (п-г) в том и только в том случае, если значения указанных

разрядов противоположных(т.е.-ЛГА42+г )Если же значения рассматриваемых разрядов совпадают (т. е. ) единичных сигналов на счетные входы триггеров подавать не нужно. Так как разряд k-граничный, то Xif , , т. е. х k+i всегда.

Для того чтобы установить совпадают или противоположны значения разрядов в нарах (ft+2+r) и (л-г), необходимо для каждого /е разбить правую часть комбииации, начиная с (/г+2)-го разряда, на три области:

Область «О, область «О или «1 и область «1.

Область «О («1) - это разряды правой части (начиная с х), значение которых, наверняка равно «нулю («едииице), при данном k.

Область «О или 1 - это разряды нравой части, значение которых при данном /г заранее неизвестно. Разряды области «О или 1 при данном k могут быть равны либо нулю, либо единице.

Область «О -это разряды (/fe+2)

-(Р-1)Область «О ИЛИ 1 - разряды

n(p-l) + (p-k). Область «1 - разряды л-() ,

номер последнего разряда области «О будет обозначать Во.

ВО П-(Р-).

35 Номер первого разряда области «1 будет

обозначать В

(p-k) + .

Если , разряд (n-t)принадлежит

i

области «1 (), то парный ему разряд (/г+2+0 принадлел(;ит «области «О, и следовательно означает, что

подавать единичные сигналы на входы соответствующих триггеров необходимо, и поэтому выход rk непосредственно соединяется со входами схем «ИЛИ (л-) и «ИЛИ(А+ +2+0 - соединение первого вида.

Если разряд (+2+s) принадлежит области «О (т. е. +2+1 So), а разряд () принадлежит области «О или 1 (т. е. ), то значения указанных разрядов

противополол ны при условии Хд 1.

Поэтому здесь имеет место соедииение второго вида.

Если разряды (й+2+r) и (л-г) принадлежат области «О или 1 (т. е. .б Л+2+г и , либо

a)- A+2+r 0 л:, 1,либо

Следовательно, на единичные входы соответствующих триггеров сигналы нужно подавать, если х,. и . Поэтому здесь имеет место соединение третьего вида.

Наконец, если разряды (й-(-2+2) н (л-г) принадлежат области «О (т. е. fe+2+2 Bo и п-Z)BO), то и, следовательно, на входы соответствующих триггеров сигналов подавать не нулсно. Поэтому выход fk не подсоединяется ко входам «ИЛИ (й-|-2+2) «ИЛИ («-2).

При нодаче сигнала начальной установки на вход схемы «ИЛИ записываются единицы в первые р триггеров и нулн-в остальные триггеры. Таким образом, первая комбинация, вырабатываемая устройством, имеет вид:

1... .

Затем на основной вход устройства (объединенные входы схемы „Я „Я блока 2) подаются сигналы г/вх.

При подаче каждого сигнала г/вх в устройстве образуется новая комбинация. Процесс образования новой комбинации протекает следующим образом: входной сигнал раснространяется по ценям переноса блока 2 до тех пор, пока не обнаружит триггер Tek, являющийся граничным триггером, нреобразуемой части комбинации. После этого на выходе Fk появляется нмпульс, а перенос дальше не раснространяется. Имнульс с выхода Fk поступает в блок 3, в котором вырабатываются сигналы для осуществления перестановки в соответствующих парах разрядов (фиг. 4).

Импульсы с выходов схем «ИЛИ блока 5 проходят на счетные входы триггеров и запоминающего регистра и опрокидывают их, производя, таким образом, преобразование правой части комбинации.

Комбинации, если их рассматривать как двоичные числа, генерируются устройством в убывающем порядке. Последней в одном цик0---0

ле работы вырабатывается комбинация--.-

п-р

1 ...1

Если указанная комбинация запи р

сана в регистре р и подается сигнал t/вх, то перенос в блоке 2 распространяется до первого разряда (так как ни у одной единицы нет справа нуля). Появляется импульс на выходе HI блока 2. Этот импульс через схему «ИЛИо устанавливает устройство в начальное состояние (1....10...0). Одновременно потребителям выдается сигнал «конец цикла.

Предмет изобретения

1.Устройство для генерации кода ностоянного веса, содержащее заноминающий регистр

и логические схемы, отличающееся тем, что, с целью сокращения оборудования устройства, в нем установлены блок выделения граничного разряда преобразуемой части кодовой комбинации и блок преобразования правой части кодовой комбинации, выходы которого подключены к счетным входам триггеров запоминающего регистра, нулевые и единичные выходы триггеров запоминающего регистра подсоединены к одной грунне входов блока нреобразования нравой части кодовой комбинации и ко входам блока выделения граничного разряда преобразуемой части кодовой комбинации, выходы которого соединены с

другой грунной входов блока преобразования правой части кодовой комбинации.

2.Устройство по п. 1, отличающееся тем, что, с целью упрощения блока выделения граничного разряда преобразуемой части кодовой комбинации, выходы триггеров i-ro и (г+1)-го разрядов заноминающего регистра подсоедннены к первым и вторым входам логических узлов t-ro разряда блока выделения граничного разряда преобразуемой части кодовой комбинации, а выход логического узла г-го разряда блока выделения граничного разряда преобразуемой части кодовой комбинации подключен к третьему входу логического узла (f-1)-го разряда блока выделения граннчного разряда преобразуемой части кодовой комбинации.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР ДВОИЧНОГО КОДА ПОСТОЯННОГО ВЕСА | 1969 |

|

SU238228A1 |

| УСТРОЙСТВО для ГЕНЕРАЦИИ ТРОИЧНОГО КОДА С ПОСТОЯННЫМ КОЛИЧЕСТВОМ «НУЛЕЙ» | 1969 |

|

SU251931A1 |

| ГЕНЕРАТОР К-ИЧНОГО РАВНОВЕСНОГО КОДА | 1970 |

|

SU260286A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2519523C1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1181155A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКИХ КОДОВ | 1971 |

|

SU317066A1 |

| Двухканальный аналого-цифровой преобразователь | 1981 |

|

SU995314A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

CofSuf ffji f 3-го eudo

CoeAjiffffuf

2-i Sut

/ eapeo fO3yff aff

4 t/OC/ГГЛ

/Ув/грео /зазуемае

i-ч- vac/m

f.fff , .. n-j л

ft-t-r н п п-1 -

Даты

1970-01-01—Публикация