Изобретение относится к вычислительной технике и может быть использовано в качестве входного устройства цифровых вычислительных комплексов для регистрации быстропротекающих электрических процессов.

Известен n-разрядный аналого-цифровой преобразователь (АЦП), содержащий устройство управления (УУ), схему сравнения (СС) и n-разрядный преобразователь код-напряжение (ПКН, DAC). УУ состоит из n-разрядного регистра (RG) и n-триггеров со схемами И. Схема сравнения представлена аналоговым компаратором напряжения, на входы которого подается входное напряжение и напряжение с выхода ПКН. УУ, СС и n-разрядный ПКН объединены в n-разрядный блок преобразования (БП). Выходы БП образованы n-информационными выходами, являющимися выходами n-триггеров. [1]

Недостатком аналога является невысокое быстродействие. Для n-разрядного АЦП быстродействие составляет n тактов.

Наиболее близким по технической сущности является аналого-цифровой преобразователь разрядностью n, содержащий триггер, схему И, n-разрядный мультиплексор, n от 1 - до n-разрядных блоков преобразования, каждый из которых включает n-разрядный регистр (RG), n триггеров Тг1,…, Тгn со схемами И И1 Иn, n-разрядный преобразователь код-напряжение и схему сравнения, причем:

к счетному входу C n-разрядного регистра подключен выход схемы И, к входу которой подключена шина тактовых импульсов и выход триггера, к входу S которого подключена шина запуск, а к входу R - выход младшего разряда n-разрядного регистра;

выходы n-разрядного регистра n,…,1 подключены к входам схем И И1,…,Иn, к входу S триггеров Тг1 Тгn-1 подключены выходы 1,…, n-1 n-разрядного регистра, к другому входу схем И И1,…, Иn подключен выход схемы сравнения, к входам которой подключен измерительный канал и выход n-разрядного преобразователя код-напряжение, выходы схем И И1,…, Иn подключены к входам R триггеров Тг1,…, Тгn;

шина запуск подключена к входу направления счета V n-разрядного регистра, к входу S триггера Тгn, а также к входу R триггеров Тг1,…, Тгn-1; выход триггеров Тг1,…, Тгn-1 соответственно подключен к входам а1,…,an n-разрядного преобразователя код-напряжение.

Прототип также включает n n-разрядных мультиплексоров (МП), n-разрядный приоритетный шифратор (ПШ, CD). Разряды цифрового кода сформированы выходными цепями мультиплексоров, начиная с n-го мультиплексора.

Недостатком прототипа является невысокая надежность работы и значительные массогабаритные показатели за счет использования большого числа аналоговых и цифровых логических устройств.

Целью изобретения является улучшение эксплуатационных характеристик АЦП, а именно надежности работы и массогабаритных характеристик.

Поставленная цель достигается тем, что в известном АЦП разрядностью n, содержащем n-разрядный приоритетный шифратор, триггер Тг0, схему И И0, n-разрядный регистр, n триггеров Тг1,…, Тгn со схемами И И1,…, Иn, n-разрядный преобразователь код-напряжение и схему сравнения, в котором: к счетному входу С n-разрядного регистра подключен выход схемы И И0, к входу которой подключен выход триггера Тг0, к входу S которого подключена шина запуск; выходы n-разрядного регистра F0,…, Fn-1 подключены к входам схем И И1,…, Иn, к входу S триггеров Тг1,…, Tгn-1 соответственно подключены выходы Fn-1,…, F1 n-разрядного регистра, к входу схем И И1,…, Иn подключен выход схемы сравнения, к входам которой подключен измерительный канал и выход n-разрядного преобразователя код-напряжение, выходы схем И И1,…, Иn соответственно подключены к входам R триггеров Тг1,…,Тгn; шина запуск подключена к входу направления счета V п-разрядного регистра, к входу S триггера Тгn, а также к входу R триггеров Тг1,·, Тгn-1 выход триггеров Тг1,…, Тгn соответственно подключен к входам а1,…, an n-разрядного преобразователя код-напряжение. Дополнительно содержит n аналоговых компараторов напряжения К1,…, Kn, n блоков эталонных напряжений Uэт1,…, Uэтn, а также n-разрядный демультиплексор (DMS) и генератор тактовых импульсов, причем: генератор тактовых импульсов подключен к входу схемы И И0; к входу аналоговых компараторов напряжения подключен измерительный канал, к другому входу аналоговых компараторов напряжения К1,…, Kn соответственно подключены выходы блоков эталонных напряжений Uэт1,…,Uэтn, к входу которых подключена шина питающего напряжения Uпит, выходы аналоговых компараторов напряжения К1,…, Kn соответственно подключены к входам х0,…, xn-1 n-разрядного приоритетного шифратора; выходы приоритетного шифратора y0,…, yk-1 подключены к адресным входам n-разрядного демультиплексора А0,…, Ak-1, шина запуск подключена к входу D n-разрядного демультиплексора и к входу R n-разрядного регистра; выходы n-разрядного демультиплексора Fn-1,…, F0 соответственно подключены к входам D0,…, Dn-1 n-разрядного регистра, а также к входам S триггеров Тгn,…, Тг1, младший разряд n-разрядного регистра подключен к входу R триггера Тг0; разряды цифрового кода сформированы выходными цепями триггеров Тгn,…, Тг1 начиная с 1-го триггера.

Использование новых узлов и новых функциональных связей обеспечивает уменьшение количества аналоговых и цифровых логических устройств, за счет чего увеличивается надежность работы аналого-цифрового преобразователя и уменьшаются массогабаритные показатели.

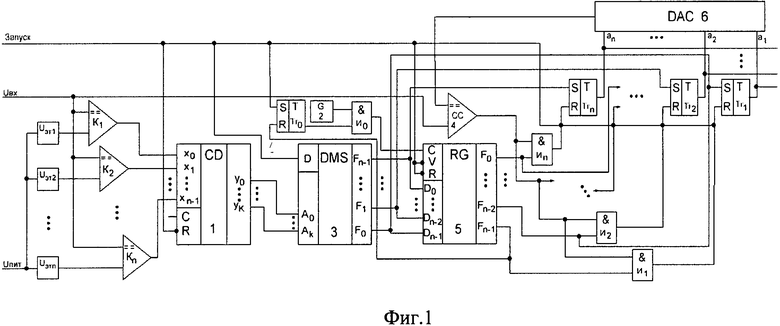

На фиг.1 представлена функциональная схема n-разрядного АЦП.

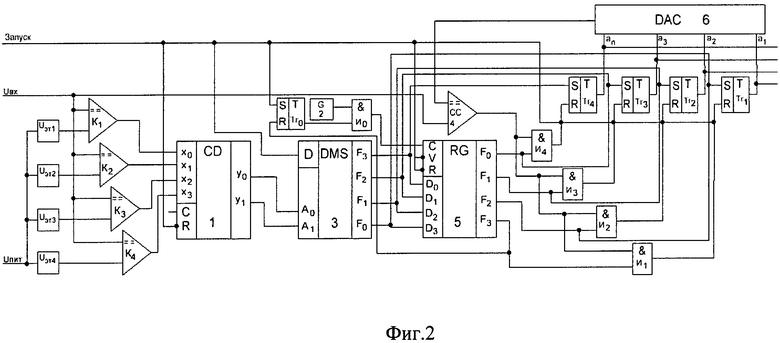

На фиг.2 приведена функциональная схема четырехразрядной реализации АЦП.

n-разрядный АЦП содержит: n-разрядный приоритетный шифратор 1; генератор тактовых импульсов 2; n-разрядный демультиплексор 3; схему сравнения 4; n-разрядный регистр 5; n-разрядный преобразователь код-напряжение 6; n блоков эталонных напряжений Uэт1,…, Uэтn; n аналоговых компараторов напряжения К1,…, Kn; триггер Тг0; схему И И0; n триггеров Тг1,…, Тгn со схемами И И1,…, Иn.

В котором: к входу аналоговых компараторов напряжения К1,…, Kn подключен измерительный канал Uвх, к другому входу аналоговых компараторов напряжения К1,…, Kn соответственно подключены выходы блоков эталонных напряжений Uэт1,…, Uэтn, к входу которых подключена шина питающего напряжения Uпит, выходы аналоговых компараторов напряжения К1,…, Kn соответственно подключены к входам x0,…, xn-1 n-разрядного приоритетного шифратора 1; выходы приоритетного шифратора 1 y0,…, yk-1 подключены к адресным входам А0,…, Ak-1 n-разрядного демультиплексора 3; выходы n-разрядного демультиплексора 3 Fn-1,…,F0 соответственно подключены к входам D0,…, Dn-1 n-разрядного регистра 5, а также к входам S триггеров Тгn,…, Тг1 младший разряд n-разрядного регистра 5 подключен к входу R триггера Тг0; к счетному входу C n-разрядного регистра 5 подключен выход схемы И И0, к входу которой подключен генератор тактовых импульсов 2 и выход триггера Тг0 к входу S, которого подключена шина запуск; выходы n-разрядного регистра 5 F0,…, Fn-1 подключены к входам схем И И1,…, Иn, к входу S триггеров Тг1,…,Тгn-1 соответственно подключены выходы Fn-1,…,F1 n-разрядного регистра 5, к другому входу схем И И1,…, Иn подключен выход схемы сравнения 4, к входам которой подключен измерительный канал и выход n-разрядного преобразователя код-напряжение 6, выходы схем И И1,…, Иn соответственно подключены к входам R триггеров Тг1,…, Тгn; шина запуск подключена к входу D n-разрядного демультиплексора 3, к входу R и V n-разрядного регистра 5, к входу S триггера Тгп, а также к входу R триггеров Тг1,…, Trn-1; выход триггеров Тг1,…, Тгn соответственно подключен к входам а1,…, an n-разрядного преобразователя код-напряжение 6.

Значения эталонных напряжений с блоков Uэт1,…, Uэтn соответствуют напряжению, равному единице разряда цифрового кода, согласно порядковому номера блока эталонного напряжения.

Аналого-цифровой преобразователь функционирует следующим образом.

В первом такте работы АЦП по приходу импульса по шине запуск обнуляются значения на n-разрядном приоритетном шифраторе 1, n-разрядном регистре 5 и триггерах Тг1,…, Тгn, а триггер Тг0 переводится в единичное состояние и подает на один из входов схемы И 2 логическую единицу, аналоговые компараторы напряжения К1,…, Kn вырабатывают импульсы, поступающие на информационные входы х0,…, xn-1 n-разрядного приоритетного шифратора 1, который считывает значения информационных входов x0,…, xn-1 и генерирует код, поступающий на адресные входы демультиплексора 3, который коммутирует вход D с одним из выходов F0,…, Fn-1, при этом сигнал проходит через n-разрядный регистр 5 и устанавливает в единичное состояние триггер, к примеру Тгk, который подает единичное значение на вход ak ПКН 6, при этом схемой сравнения 4 производится сравнение напряжения с измерительного канала Uвх и эталонного напряжения с выхода ПКН 6, если напряжение с измерительного канала Uвх меньше напряжения с выхода ПКН 6, то схема сравнения 4 выдаст импульс, который, пройдя схему Иk, установит триггер Тгk в состояние 0. n-разрядный регистр производит сдвиг единицы с выхода Fk на выход Fk-1, при этом триггер Тгk-1 переводится в единичное состояние, при этом, если напряжение измерительного канала UBX больше напряжения с выхода ПКН 6, то триггер Тгk-1 сохраняет состояние 1. Такты работы аналого-цифрового преобразователя повторяются до тех пор, пока на младшем разряде n-разрядного регистра 5 не будет единицы, при этом триггер Тг0 переводится в нулевое состояние, тем самым закрывая схему И И0. Разряды цифрового кода формируются выходными цепями триггеров начиная с 1-го триггера.

В качестве примера ниже приведено аналого-цифровое преобразование четырехразрядным аналого-цифровым преобразователем фиг.2 напряжения измерительного канала Uвх, соответствующего цифровому коду 0011.

В первом такте триггер Тг0 переводится в единичное состояние и подает на один из входов схемы И 2 логическую единицу, одновременно аналоговые компараторы напряжения К1,…, К4 вырабатывают импульсы, поступающие на информационные входы приоритетного шифратора 1, приоритетный шифратор 1 считывает значения информационных входов х0 - 1, x1 - 1, х2 - 0, х3 - 0 и генерирует код y0 - 1, y1 - 0, поступающий на адресные входы а0 и а1 демультиплексора 3. Демультиплексор 3 коммутирует вход D с выходом F1, при этом триггер Тг2 переводится в единичное состояние, на вход а2 ПКН 6 поступает единица, соответственно на его выходе формируется эталонное напряжение, соответствующее цифровому коду 0010. На выходе схемы сравнения 4 импульс не формируется, триггер Тг2 сохраняет свое значение, четырехразрядный регистр 5 производит сдвиг единицы на выход F3, триггер Tг1 переводится в единичное состояние, а триггер Тг0 в состояние 0, тем самым закрывается схема И0.

Использование описанного аналого-цифрового преобразователя позволяет сократить необходимое число аналоговых и цифровых логических устройств относительно прототипа с сохранением заданного быстродействия, а именно для n-разрядного АЦП на:

n n-разрядных мультиплексоров;

n-1 от 1 до n-1-разрядных блоков преобразования, например, k-разрядный блок преобразования включает: схему сравнения; k-разрядный преобразователь код-напряжение; k-разрядный регистр; k триггеров; k схем И.

Полезным эффектом от использования устройства является повышение надежности его работы, а также структурное упрощение АЦП и снижение массогабаритных показателей.

В качестве экономического положительного эффекта можно выделить снижение стоимости аналого-цифрового преобразователя по сравнению с прототипом.

Положительные эффекты от использования аналого-цифрового преобразователя достигаются за счет применения оригинальных схемотехнических решений, позволяющих снизить число используемых аналоговых и цифровых логических устройств.

Промышленная осуществимость предлагаемого АЦП обосновывается тем, что в примере его технической реализации используются известные по своему прямому функциональному назначению узлы и связи.

Источники информации

1. Гиттис Э.И., Пискулов Е.А. Аналого-цифровые преобразователи: Учеб. пособие для вузов. - М.: Энергоиздат, 1981. - 360 с.(стр.233-236) - аналог.

2. Патент на полезную модель Аналого-цифровой преобразователь, №119190, опубл. 10.08.2012, авторы Кривоногов А.Н., Константинов Е.Н., патентообладатель ФГУП "18 ЦНИИ" МО РФ - прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2028730C1 |

| Вычислительный преобразователь информации | 1985 |

|

SU1330642A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1589395A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве входного устройства цифровых вычислительных комплексов для регистрации быстропротекающих электрических процессов. Технический результат - улучшение эксплуатационных характеристик аналого-цифрового преобразователя (АЦП), а именно надежности работы и массогабаритных характеристик. Аналого-цифровой преобразователь содержит n-разрядный приоритетный шифратор, триггер Тг0, схему И И0, n-разрядный регистр, n триггеров Тг1, …, Тгn со схемами И И1, …, Иn, n-разрядный преобразователь код-напряжение, схему сравнения, шину запуска, n аналоговых компараторов напряжения K1, …, Kn, n блоков эталонных напряжений Uэт1, …, Uэтn, n-разрядный демультиплексор и генератор тактовых импульсов. 2 ил.

Аналого-цифровой преобразователь, содержащий n-разрядный приоритетный шифратор, триггер Тг0, схему И И0, n-разрядный регистр, n триггеров Тг1, …, Тгn со схемами И И1, …, Иn, n-разрядный преобразователь код-напряжение и схему сравнения, в котором:

к счетному входу C n-разрядного регистра подключен выход схемы И И0, к входу которой подключен выход триггера Тг0, к входу S которого подключена шина запуск;

выходы n-разрядного регистра F0, …, Fn-1 подключены к входам схем И И1, …, Иn, к входу S триггеров Тгn-1, …, Tг1 соответственно подключены выходы F1, …, Fn-1 n-разрядного регистра, к другому входу схем И И1, …, Иn подключен выход схемы сравнения, к входам которой подключен измерительный канал и выход n-разрядного преобразователя код-напряжение, выходы схем И И1, …, Иn соответственно подключены к входам R триггеров Тг1, …, Тгn;

шина запуск подключена к входу направления счета V n-разрядного регистра, к входу S триггера Тгn, а также к входу R триггеров Тг1, …, Тгn-1, выход триггеров Тг1, …, Тгn соответственно подключен к входам а1, …, an n-разрядного преобразователя код-напряжение;

отличающийся тем, что дополнительно содержит n аналоговых компараторов напряжения K1, …, Kn, n блоков эталонных напряжений Uэт1, …, Uэтn, а также n-разрядный демультиплексор и генератор тактовых импульсов, причем:

генератор тактовых импульсов подключен к входу схемы И И0;

к входу аналоговых компараторов напряжения подключен измерительный канал, к другому входу аналоговых компараторов напряжения К1, …, Kn соответственно подключены выходы блоков эталонных напряжений Uэт1, …, Uэтn, к входу которых подключена шина питающего напряжения Uпит, выходы аналоговых компараторов напряжения К1, …, Kn соответственно подключены к входам x0, …, xn-1 n-разрядного приоритетного шифратора;

выходы приоритетного шифратора y0, …, yk-1 подключены к адресным входам n-разрядного демультиплексора A0, …, Ak-1;

шина запуск подключена к входу D n-разрядного демультиплексора и к входу R n-разрядного регистра;

выходы n-разрядного демультиплексора Fn-1, …, F0 соответственно подключены к входам D0, …, Dn-1 n-разрядного регистра, а также к входам S триггеров Тгn, …, Тг1;

младший разряд n-разрядного регистра подключен к входу R триггера Тг0;

разряды цифрового кода сформированы выходными цепями триггеров Тгn, …, Тг1 начиная с 1-го триггера.

| Способ получения суперфосфата | 1958 |

|

SU119190A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2028730C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| US 7173557 B2, 06.02.2007 | |||

| JP 2012105108 A, 31.05.2012 | |||

| JP 2008124571 A, 29.05.2008 | |||

Авторы

Даты

2014-06-10—Публикация

2012-11-06—Подача