Пзвестны запоминающие устройства на цилиндрических тонких магнитных пленках, содержащие блок памяти, магистраль тактовых импульсов, регистр числа, регистр адреса, формирователи минимальных и максимальных уровней токов управления, местное устройство управления со счетчиком тактовых импульсов и схемами совпадения для запуска формирователей минимальных и максимальных уровней токов управления.

Предложенное устройство отличается тем, что в него введены триггер, вентиль и переключатель единичных и нулевых входов числового регистра. Единичный вход триггера соединен с выходом счетчика тактовых импульсов, единичный выход - со входами схем совпадения, осуществляющих за.пуск формирователей минимальных уровней токов, и со входом вентиля, другой вход которого связан с магистралью тактовых импульсов, а выход соединен соответственно с нулевым входом триггера, со счетным входом регистра адреса и с одним из входов переключателя. Со вторым входом переключателя соединен выход счетчика тактовых импульсов, а нулевой выход триггера соединен со входами схем совпадения, осуществляющих запуск формирователей максимальных уровней токов. Это позволяет обеспечить автоматический контроль запоминающего устройства в наиболее тяжелом режиме работы запоминающих ячеек.

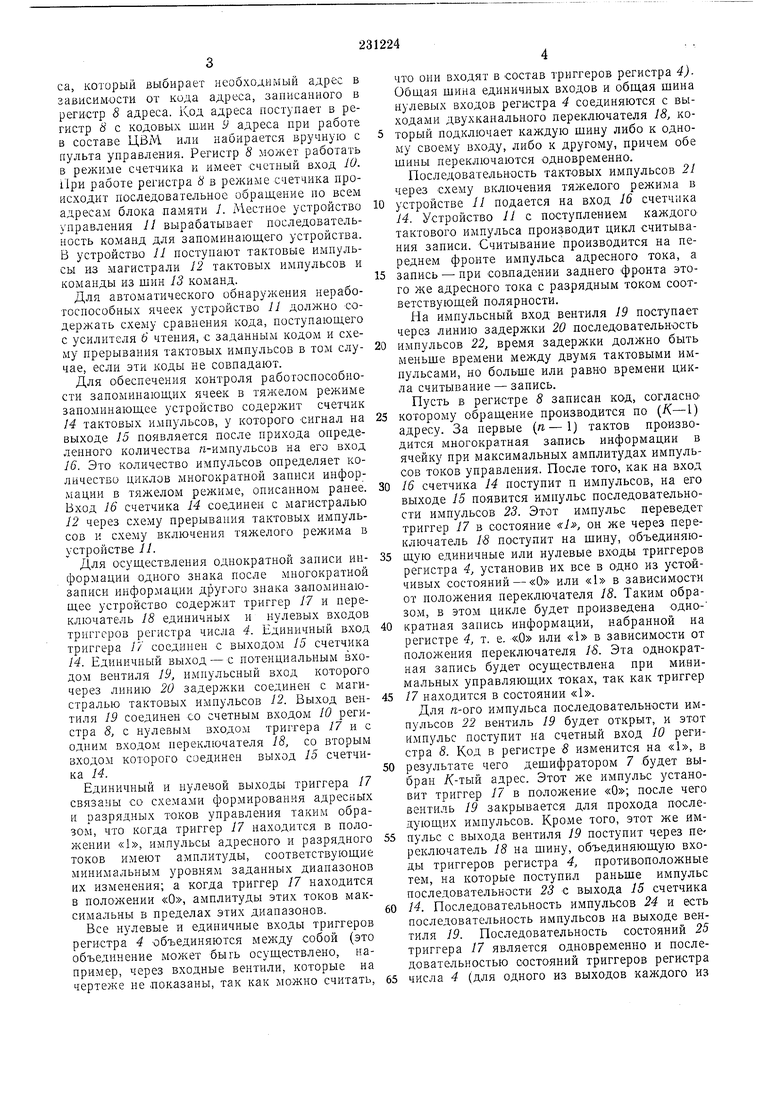

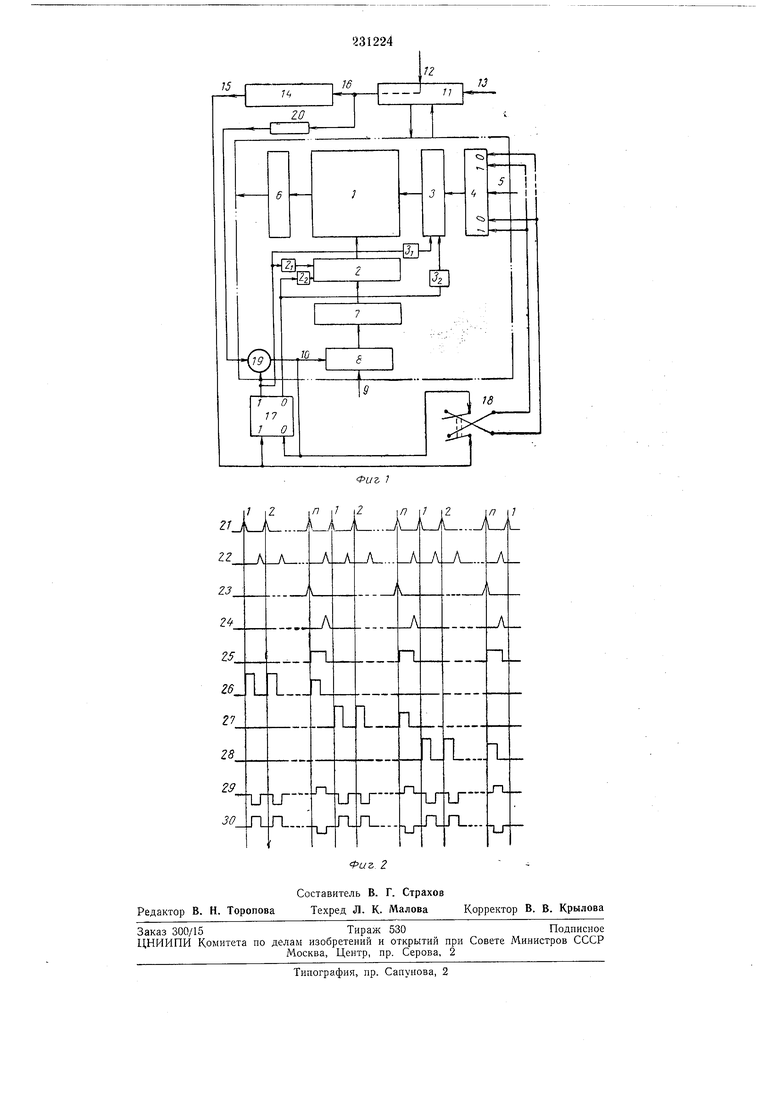

На фиг. 1 приведена блок-схема предлагаемого запоминающего устройства; на фиг. 2 - временная диаграмма работы этого устройства.

Запоминающее устройство содержит блок памяти / на цилиндрических тонких магнитных пленках. Схема 2 формирования адресных токов может формировать импульсы тока, амплитуды которых соответствуют максимальному и минимальному уровням заданного или практически достижимого диапазона изменения амплитуд адресных токов. Схема 3 формирования разрядных токов может формировать импульсы тока, амплитуды которых также соответствую двум уровням заданного диапазона их изменения.

На чертеже позициями 2, 3 обозначены схемы совпадения, осуществляющие запуск формирователей минимальных уровней токов,

позициями 2z, 2 - схемы совпадения, осуществляющие запуск формирователей максимальных уровней токов.

Схема 3 управляется регистром 4 числа. Код числа поступает при работе в составе

ЦВМ или набирается вручную с пульта управления запоминающего устройства на регистр числа из кодовых шин 5 числа.

Полезные сигналы с запоминающих ячеек блока памяти 1 усиливаются усилителями 6

са, который выбирает необходимый адрес в зависимости от кода адреса, записанного в регистр S адреса. Код адреса поступает в регистр и с кодовых шин У адреса при работе в составе ЦВМ или набирается вручиую с аульта управления. Регистр 8 может работать в режиме счетчика и имеет счетный вход 10. 11ри работе регистра 8 в режиме счетчика происходит последовательное обращение по всем адресам блока памяти 1. Местное устройство управления 11 вырабатывает последовательность команд для запоминающего устройства. В устройство 11 поступают тактовые импульсы из магистрали 12 тактовых импульсов и команды из щин 13 команд.

Для автоматического обнаружения неработоспособных ячеек устройство 11 должно содержать схему сравнения кода, поступающего с усилителя 6 чтения, с заданным кодом и схему прерывания тактовых импульсов в том случае, если эти коды не совпадают.

Для обеспечения контроля работоспособности запоминающих ячеек в тяжелом режиме запоминающее устройство содержит счетчик 14 тактовых импульсов, у которого сигнал на выходе 15 появляется после прихода определенного количества п-импульсов на его вход 16. Это количество импульсов определяет количество циклов многократной записи информации в тяжелом режиме, описанном ранее. Вход 16 счетчика 14 соединен с магистралью 12 через схему прерывания тактовых импульсов и схему включения тяжелого режима в устройстве 11.

Для осуществления однократной записи информации одного знака после многократной записи информации другого знака запоминающее устройство содержит триггер 17 и переключатель 18 единичных и нулевых входов триггеров регистра числа 4. Единичный вход триггера 17 соединен с выходом 15 счетчика 14. Единичный выход -с потенциальным входом вентиля 19, импульсный вход которого через линию 20 задержки соединен с магистралью тактовых импульсов 12. Выход вентиля 19 соединен со счетным входом 10 регистра 8, с нулевым входом триггера /7 и с одним входом переключателя 18, со вторым входом которого соединен выход 15 счетчика 14.

Единичный и нулевой выходы триггера 17 связаны со схемами формирования адресных и разрядных токов управления таким образом, что когда триггер 17 находится в полоимении «1, импульсы адресного и разрядного токов имеют амплитуды, соответствующие минимальным уровням заданных диапазонов их изменения; а когда триггер 17 находится в положении «О, амплитуды этих токов максимальны в пределах этих диапазонов.

Все нулевые и единичные входы триггеров регистра 4 объединяются между собой (это объединение может быть осуществлено, например, через входные вентили, которые на чертеже не показаны, так как можно считать.

что онн входят в состав триггеров регистра 4). Общая щина единичных входов и общая щина нулевых входов регистра 4 соединяются с выходами двухканального переключателя 18, который подключает каждую щину либо к одному своему входу, либо к другому, причем обе шины переключаются одновременно.

Последовательность тактовых импульсов 21 через схему включения тяжелого режима в

устройстве 11 подается на вход 16 счетчика 14. Устройство 11 с поступлением каждого тактового импульса производит цикл считывания записи. Считывание производится на переднем фронте импульса адресного тока, а

запись - при совпадении заднего фронта этого адресного тока с разрядным током соответствующей полярности.

На импульсный вход вентиля 19 поступает через линию задержки 20 последовательность

импульсов 22, время задержки должно быть меньше времени между двумя тактовыми имнульсами, но больше или равно времени цикла считывание - запись. Пусть в регистре 8 записан код, согласно

которому обращение производится по (К-1) адресу. За первые (п-1) тактов производится многократная запись информации в ячейку при максимальных амплитудах импульсов токов управления. После того, как на вход

16 счетчика 14 поступит п импульсов, на его выходе 15 появится импульс последовательности импульсов 23. Этот импульс переведет триггер 17 в состояние «1, он же через переключатель 18 постудит на шину, объединяющую единичные илн нулевые входы триггеров регистра 4, установив их все в одно из устойчивых состояний - «О или «1 в зависимости от полом ения переключателя 18. Таким образом, в этом цикле будет произведена однократная запись информации, набранной на регистре 4, т. е. «О или «1 в зависимости от положения переключателя 18. Эта однократная запись будет осуществлена при минимальных управляющих токах, так как триггер

/7 находится в состоянии «1.

Для п-ого импульса последовательности импульсов 22 вентиль 19 будет открыт, и этот импульс поступит на счетный вход 10 регистра 8. Код в регистре 8 изменится на «1, в

результате чего дешифратором 7 .будет выбран Х-тый адрес. Этот же импульс установит триггер 17 в положение после чего вентиль 19 закрывается для прохода последующих импульсов. Кроме того, этот же импульс с выхода вентиля 19 поступит через переключатель 18 на тину, объединяющую входы триггеров регистра 4, противоположные тем, на которые поступил раньше импульс последовательности 23 с выхода 15 счетчика

14. Последовательность импульсов 24 и есть последовательность импульсов на выходе вентиля 19. Последовательность состояний 25 триггера 17 является одновременно н последовательностью состояний триггеров регистра этих триггеров). Последующие (п- 1) циклов будут производить многократную запись по К - тому адресу, п-ът цикл произведет однократную запись, после чего произойдет переход на (K-t- 1} адрес и т. д. После того, как в регистре 8 будут перебраны все возм0л ные кодовые комбинации, устройство вновь вернется к (К - I) адресу. При этом во всем блоке памяти будет храниться однократно записанная информация 10 одного знака. 26 - есть последовательность импульсоз адресного тока по (/С-1) адресу; 27 - Я-тому адресу и 28 - по (К + I) адресу; 29 - последовательность импульсов 15 разрядного тока при проверке работоспособности ячеек по «1, 30 - при проверке по «О. Переход от последовательности 29 к последовательности 30 и наоборот производится изменением положения переключателя 18.20 Если первое считывание по каждому адресу нового цикла обхода адресов будет контрольным, то полученный режим работы запоминающего устройства будет самым тяжелым для запоминающих ячеек на цилиндри- 25 ческих тонких пленках, так как это есть считывание однократно записанной информации при минимальных токах управления, которое производится после многократной записи информации противоположного знака в соседние ЗО запоминающие ячейки, производимой при максимальных токах управления. Полезный сигнал, соответствующий однократно записанной информации, должен быть надежно различим на фоне помех и усилен усилителем 35 чтения. Сигналы с усилителей 6 чтения, полученные по первому обращению после перехода на новый адрес, должны поступать на устройство сравнения, все они должны быть либо сигналами «1 либо сигналами «О в 40 зависимости от положения переключателя 18. В том случае, если какие-либо сигналы отсутствуют (меньще порога срабатывания) или есть сигналы, несущие противоположную информацию, срабатывает устройство, преры- 45 вающее тактовые импульсы, а код в регистре 6 и схема сравнения, имеющие индикацию на пульте, дают координаты неработоспособных ячеек.,,i.j Начальное состояние триггера 17 и тригге- 50 ров регистра 4 перед переходом на тяжелый режим работы может быть любым, цикл устанавливается после одного обхода всех адресов. Перед включением схемы сравнения и останова полезно несколько раз обойти все ад- 55 реса в тяжелом режиме работы. 5 Если наблюдать выходной сигнал с запоминающих ячеек одного разряда на экране осциллографа, когда запоминающее устройство работает в тяжелом режиме, то полученная картина даст максимальный разброс сигналов в этом разряде, что бывает необходимо знать при наладке. При работе в описанном режиме, благодаря тому, что импульсы тока по всем разрядам имеют одиу полярность, электронные схемы управления запоминающего устройства и схемы питания будут работать в наиболее тяжелых условиях. Так что указанный режим является тяжелым не только для запоминающих ячеек на цилиндрических тонких магнитных пленках, но и для схем управления запоминающего устройства и для схем питания. Поэтому запоминающее устройство, отлаженное в режиме работы, описанном в настоящей заявке, отличается высокой надежностью и работоспособностью. Предмет изобретения Запоминающее устройство на цилиндрических магнитных пленках, содержащее блок памяти, магистраль тактовых импульсов, регистр числа, регистр адреса, формирователи минимальных и максимальных уровней токов управления, местное устройство управления со счетчиком тактовых импульсов и схемами совпадения для запуска формирователей минимальных и максимальных уровней токов управления, отличающееся тем, что, с целью обеспечения автоматического контроля запоминающего устройства в наиболее тяжелом режиме работы запоминающих ячеек, в него введены триггер, вентиль и переключатель единичных и нулевых входов числового регистра, причем единичный вход указанного триггера соединен с выходом счетчика тактовых импульсов, единичный выход - со входами схем совпадения, осуществляющих запуск формирователей минимальных уровней токов, и со входом упомянутого вентиля, другой вход которого связан с магистралью тактовых импульсов, а выход соединен соответственно с нулевым входом указанного триггера, со счетньш входом регистра адреса и с одним из входов упомянутого переключателя, со вторым входом которого соединен выход счетчика тактовых импульсов, а нулевой выход указанного триггера соединен со входами схем сонпадения, осуществляющих запуск формирователей максимальных уровней токов.

;j

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| Устройство контроля кода счетчика | 1979 |

|

SU815920A1 |

| Устройство обнаружения кодов групповой синхронизации | 1990 |

|

SU1812628A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| АН СССР J „T.'^i''; • •-^^^••';• ^--i^A,. .jf;:.\tC2CO!GC;ri'^^>& плг^иткз •->& | 1965 |

|

SU172567A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

Даты

1968-01-01—Публикация