Изобретение относится к те.хнике представления аналоговой величины ее цифровым эквивалентом и может быть использовано в сиCTejMax автоматического унравления, аналогоцифровых комплексах и т. д.

Известно устройство для нреобразования напряжения в цифровой код путем одновременного кодирования сначала группы старших разрядов (грубый отсчет), а затем группы младших разрядов (точный отсчет), содержащее схемы сравнения по числу уровней грубого отсчета, резисторный делитель, генератор илгпульсов, счетчик, преобразователь кода в напряжение, усилитель, переключатель и схему сравнения коррекции кода.

Однако нри преобразовании быстро изменяющегося нанряжения разность преобразуемого и компенсирующего напряжений к моменту точного отсчета может превысить динамический дианазон ступени точного отсчета, в результате чего возникает динамическая погрешность.

Цель предлагаемого изобретения заключается в умеиьщении динамической погрешности при преобразовании быстро изменяющихся иапряжепий.

ную экстраполяцию преобразуемого напряжения. Это позволяет получить к моменту точного отсчета такую величину разности преобразуемого и компенсирующего напряжений, которая укладывается в динамический диапазон ступени точного отсчета.

Предлагаемый преобразователь отличается тем, что содержит сумматор, выходы которого соединены с преобразованием кода в напряжение, а входа через схемы «PI подключены к шифратору и блоку управления.

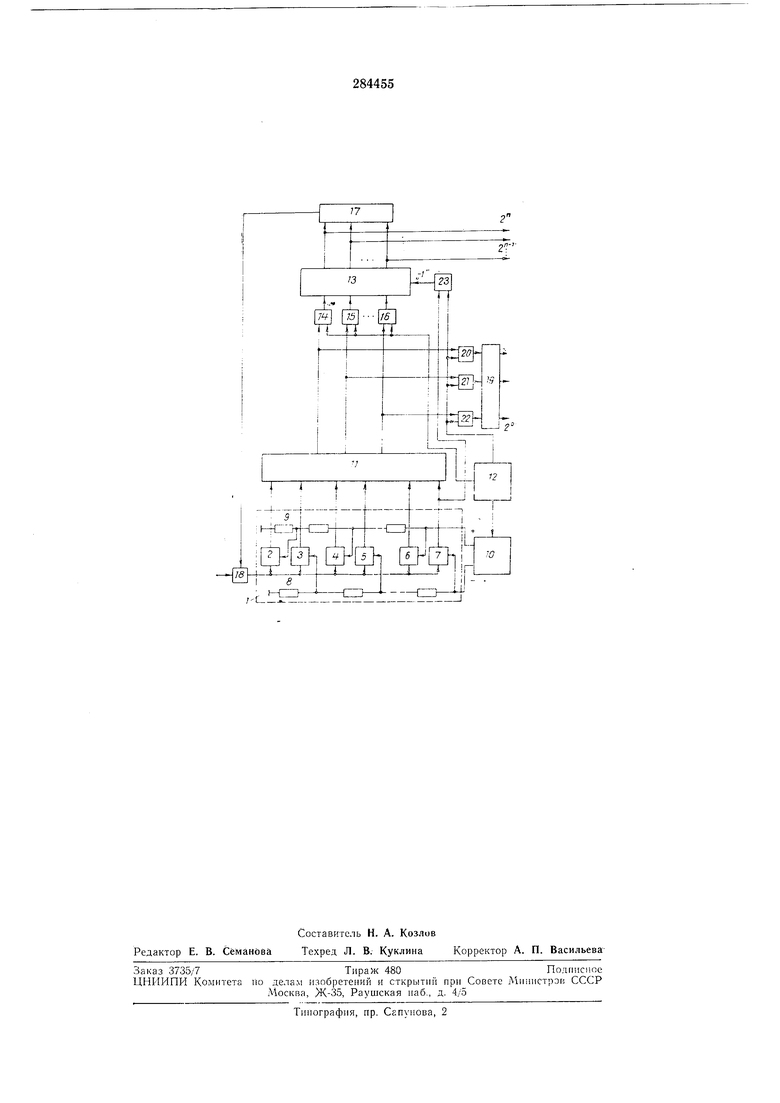

На чертеже приведена функциональная схема нредлагаемого устройства.

Преобразователь состоит из узла квантования 1, в состав которого входят схемы сравнения 2-7, число которых равно количеству уровней квантования, отдельно для положительных и отрицательных напряжений, и два делителя опорных нанряжений 8 и 9 на резисторах; блока выдачи опорных напряжений 10, выходы которого подключены к делителям онорных напряжений; шифратора //, входы которого соединены с выходами узла квантования; устройства выдачи управляющих импульсов 12. Входы сумматора 13 через схемы «И 14-16, связанные с устройсгвом выдачи управляющих импульсов, соединяются с выходами шифратора 11. Входы преобразователя код - нанряжение 17 соединены с выходами сумматора. На вход устройства суммирования

напряжений 18 подается преобразуемое напряжение и компенсирующее напряжение с выхода преобразователя код-напряжение 17, а выход - соединяется с входами всех схем сравнения. Входы регистра 19 для хранения кода младших разрядов через схемы «И 20- 23, связанные с устройством выдачи управляющих импульсов, соединены с выходами узла квантования.

Перед началом преобразования происходит гашение предыдущего кода.

При первом отсчете через устройство суммирования напряжений на первые входы всех схем сравнения 2-7 поступает преобразуемое напряжение. На вторые входы этих схем подаются фиксированные напряжений с делителей 5 и .9 опорных напряжений, построенных таким образом, что напряжение в каждой носледуюи;ей точке делителя отличается от предыдущего на воличи)}- одного уровня квантования. Результат сравнения кодируется с помоихью шифратора // и через схемы «И 14-16 поступает на сумматор 13. Отрицательное напряжение кодируется дополнительным кодом для замены операции вычитаияя операцией сложения.

С выходов сумматора 13 код поступает на преобразователь код - напряжение /7, на выходе которого формируется компенсирующее напряжение.

При втором отсчете на схемы сравнения 2- 7 поступает разность изменившегося за врслш .между отсчетами преобразуемого и комиенсирующего напряжений. Онорные напряжошя, выдаваемые с блока опорных напряжений 10 на узел квантования /, уменьшаются вдвое. В результате сравнения на выходах шифратора // получается удвоенный код приращения входного напряжения за время отсчетами, соторый суммируется с кодом, иолучсины.м при первом отсчете и хранящимся в сумматоре. На выходе преобразователя код - напряжение 17 формируется новое компенсирующее напряжение, которое при равенстве интервалов времени между отсчетами соответствует входному напряжению, экстраполирован ис.м у к моменту точного отсчета. Это позволяет получить такую разность входного и компенсирующего напряжений к моменту точного отсчета, которая укладывается в динамнческнй диапазон точного отсчета.

Третнй отсчет (точный) осуществляется спомощью тех же схе.м сравнения 2-7, для чего опорные напряжения, выдаваемые с блока опорных напряжений 10, уменьшаются в 2

раз (где п - число разрядов кода грубогоотсчета). Результат сравнения кодируется с помощью шифратора // и заносится в регистр 19 хранения кода iлaдшиx разрядов. Если разность входного и комиенсируюшего

нанряжений отрицательна, она кодируется дополнительным КОДОЛ1, а 113 содержимого сум.матора 13 вычитается единица.

В итоге иолучается код преобразуемого нанряжения с количеством разрядов, равным

су.мме разрядов грубого и точного отсчетов (отрицательные напряжения В1з1даются в дополнительном коде).

П р е д м е т н з о б р с т е н и я

Преобразователь напряжения в код, содержащий схемы сравнения, шифратор, блок опорных напряженнй, нреобразователь кода в напряжение, схемы «И, регистр для хранения кода младших разрядов, устройство суммирования нанряжений, блок управления, отличающийся тем, что, с целью уменьшения дииамической погрешности, он содержит сумматор, выходы которого соединены с преобразователем кода в напряжение, а входы через схемы «Pi подключены к шифратору и блоку управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU305580A1 |

| Устройство воспроизведения изображений в условных цветах | 1980 |

|

SU932652A1 |

| Преобразователь перемещения в код | 1988 |

|

SU1531221A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU732955A1 |

| Преобразователь напряжения в код | 1976 |

|

SU599349A1 |

| Преобразователь перемещения в код | 1985 |

|

SU1277395A2 |

| Преобразователь перемещения в код | 1974 |

|

SU541189A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Преобразователь угла поворота вала в код | 1979 |

|

SU881802A1 |

| Двухотчетный преобразователь углового перемещения в цифровой код | 1975 |

|

SU526932A1 |

Даты

1970-01-01—Публикация