I

Изобретение относится к измерительной и вычислительной технике и может быть использовано в различных информационно-измерительных системах

Изв,естны преобразователи напряжения в kofl параллельно-последователь.ного уравновешивания, циклические, в которых в каждом такте преобразования параллельно определяются несколько разрядов цифрового кода, содержащие дифференциальный усилитель, преобразователь напряжения в код, схемы сравнения, шифратор и регистры. В них размеры и положение шкалы эталонных напряжения (ШЭН) устанавливаются в предположении, что за время с момента предыдущего сравнения сигнала с ШЭН до момента текущего сравнениявходной сигнал изменился незначительно l .

Однако в этих преобразователях на пряжение в код преобразуется в ограниченном частотном диапазоне. При расширении частотного диапазона преобразуемых сигналов в низ возрастают динамические погрешности.

Известен аналого-цифровой преобразователь параллельно-последовательного уравновешивания с масштабным преобразованием нескомпенсированной разности, состоящий из дифференциального

усилителя, один вход которого соединен с входной клеммой устройства, другой вход - с выходом преобразователя кода в напряжение, третий вход - с выходом блока управления, блока сравнения, подклю генного к выходу дифференциального усилителя, дешифратора, соединенного с выходом блока сравнения, клапанов и регистров 2. Дифференциальный усилитель выполнен с переменным коэффициентом усиления, величина M.J которого определяется по тактам уравновешивания в соответствии с соотношением

is № АЛ-( А

Рде m число схем сравнения;

oL - основание системы счисления Процесс преобразования напряжения в код состоит из трех тактов, в каждом из которых производится квантование сигнала на восемь уровней.

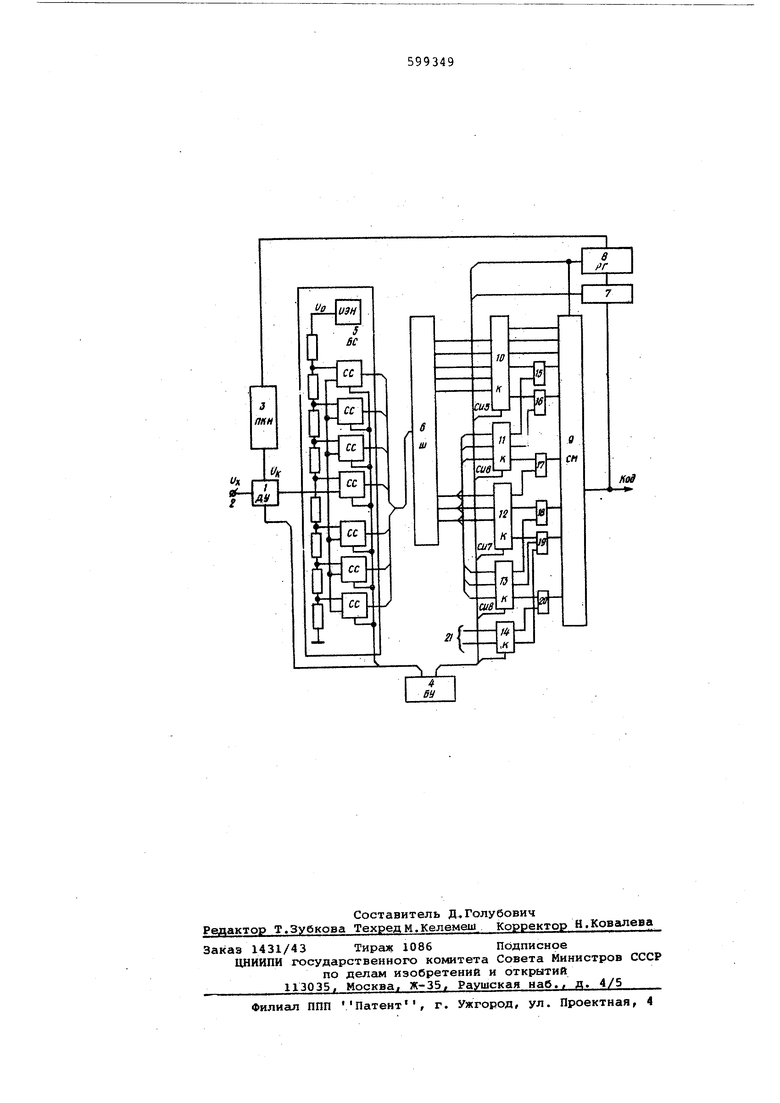

Однако такой преобразователь преобразует напряжения, изменяющиеся со скоростью, не превосходящей 0,5 кванта младшего разряда за время преобразования. По этой причине частотный диапазон преобразуемых им напряжений ограничен. При увеличении допустимой скорости изменения преобразующего сигнала в них возрастают динамические погрешности. Цель изобретения - увеличение допустимой скорости изменения входного сигнала путем изменения коэффициента масштабного преобразования нескомпенсированной разности по тактам уравновеишвания с тем, чтобы исключить выход преобразуемого сигнала из преде лов шкалы эталонных напряжений. Это достигается тем, что в преобразователь, содержащий дифференциальный усилитель с переменным коэффициентом усиления, один вход которого соединен с входной клеммой устройства другой вход - с выходом преобразовате Ля кода в напряжение, третий вход - с выходом блока управления, блок сравнения, подключенный к выходу дифферен циального усилителя и к выходу блока управления, шифратор, соединенный с выходамиблока сравнения, клапаны и регистр одни входы которых соединены с выходами блока управления, другие входы регистра соединены с выходами клапанов, а выходы регистра соединены с входами преобразователя кода в напряжение, введены сумматор, элементы ИЛИ/ шины кода смещения шкалы и допол нительные клапаны, входы синхронизации которых соединены с выходами бло ка управления, причем одни входы сум матора через дополнительные клапаны соединены с выходами шифратора, другие входы сумматора соединены соотве ственно с выходами одних элементов И входы которых через соответствующие дополнительные клапаны соединены с в ходами шифратора, входы Ьшадших раз рядов сумматора через другие элемент ИЛИ и дополнительные клапаны подключены к шинам Кода смещения шкалы, а выходы сумматора через клапаны соеди нены с входами регистра. На чертеже показана структурная схема предлагаемого преобразователя напряжения в код. Преобразователь напряжения в код содержит дифференциальный усилитель 1, один вход которого соединен с вхо Ной клеммой устройства 2, другой BXO с выходом преобразователя кода в напряжение 3, третий вход - с выходом блока управления 4. Дифференциальный усилитель. 1 выполнен с переменным ко эффициентом усиления, величину MI которого определяют по тактам уравно вешивания 1 . в соответствии с соотношением . , где И - число схем сравнения; допустимое приращение сигна ла на i -м такте, отнесенное к величине кванта младшего разряда кода. Устройство состоит также из блока сравнения 5, подключенного к выходу дифференциального усилителя 1 и к ыходу блока 4 управления,шифратора 6, соединенного с выходами блока 5 сравнения, клапанов 7 и регистра 8. Одни входы клапанов 7 и регистра 8 соединены с выходами блока 4 управления, другие входы-регистра 8 соединены с выходами клапанов 7, а выходы регистра 8 соединены с входами преобразователя 3 кода в напряжение. Устройство снабжено также сумматором 9, дополнительными клапанами 10, 11, 12, 13 и 14, входы синхронизации которых соединены с выходами блока 4 управления, и элементы ИЛИ 15, 16, 17, 18, 19 и 20, Причем одни входы сумматора 9 через дополнительные клапаны Ю соединены с выходами шифратора 6. Другие входы сумматора 9 соединены соответственно с выходами элементов ИЛИ 15, 16, 17, 18, 19 и 20, входы которых через соответствующие дополнительные клапаны 10, 11, 12 и 13 соединены с выходами шифратора 6. Входы младших разрядов сумматора 9 через дополнительные клапаны 14 и элементы ИЛИ 19 и 20 подключены в шинам кода смещения шкалы 21. Выходы сумматор 9 через клапаны 7 соединены с входами регистра 8.. Преобразователь напряжения в код работает следующим образом. По сигна-. лу блока 4 управления коэффициент усиления М дифференциального усилителя 1 устанавливается равным 1, затем регистр 8 сбрасывается в нуль, а в сумматор 9 заносится нуль. Далее в сумматор 9 через клапан 14 заносится код смещения шкалы, который вводится, чтобы исключить выход преобразуемого сигнала из диапазона шкалы эталонных напряжений на следующем такте уравновешивания. -После установления переходных процессов в преобразователь кода в напряжение 3 и дифференциальном усилителе 1 преобразуемое напряжение и поступает в блок 5 сравнения, где оно сравнивается с набором эталонныхнапряжений. Результат сравнения фиксируется в блоке сравнения 5. По результату сравнения, указывающему на принадлежность преобразуемого напряжения U , определенному кванту шкалы эталонных напряжений, шифратор 6 формирует двоичный код номера этого кванта. Затем двоичный код номера кванта подается через клапаны 10, на входы сумматора 9, который образует путем сложения с-ранее занесенным кодом смещения шкалы код компенсирующего напряжения. Далее код компенсирующего напряжения через клапан 7 заносится в регистр В. В соответствии с этим кодом преобразователь 3 вырабатывает компенсирующее напряжение JK/ этом один такт уравновешивания преобразуемого напряжения Ux заканчивается.

Во втором такте уравновешивания коэффициент усиления дифференциального усилителя 1 изменяется на Mg/равный,например, 6. Разность ULI UX-UK усиливается в 6 раз и внов поступает на вход блока сравнения 5.

По результату сравнения, зафиксированному в блоке сравнения 5, шифратор 6 Формирует очередные три разряда двоичного кода преобразуемого напряжения, которые через клапаны 11, элементы ИЛИ 15 и 16 поступают на входы сумматора 9, содержимое которого предварительно изменено на величину смещения, шкалы. Двоичные коды, определенные на первом и втором тактах урав новешивания, суммируются в сумматоре 9 с перекрытием их в разрядах.

Далее двоичный код с выхода сумматора 9 через клапан 7 передается в регистр 8, сигналы с выхода которого инициируют выработку компенсирующего напряжения UKJПроцесс определения очередных разрядов двоичного кода преобразуемого напряжения в третьем и в четвертом тактах Идет в последовательности, аналогичной описанной, с тем лищь отличием, что коэффициент усиления дифференциального усилителя 1 устанавливается равным 4 6 4 24 и 24 2 48. В четвертом такте код смещения шкалы на -входы сумматора 9 не подается, так как компенсирующее напряжение в нем не вырабатывается..

Увеличение допустимой скорости изменения входного сигнала при сохранении заданного уровня динамической погрешности в устройстве обеспечивается заданием условий работы, искЛючакяцих выход преобразуемого напряжения вследствие его изменения в процессе преобразования из шкалы эталонных напряжений.

Формула изобретения

Преобразователь напряжений в код, содержащий дифференциальный усилитель с переменным коэффициентом усиления, один вход которого соединен с входной устройства, другой вход - с выходом преобразователя кода в напряжение, третий вход - с выходом блока управления, блок сравнения, подключенный к выходу дифференциального усилителя и к выходу блока управления, шифратор, соединенный с выходами блока сравнения, клапаны и регистр, одни входы которых соединены с выходами блока управления, другие входы регистра соединены с выходами клапанов, а выходы регистра соединены с входами преобразователя кода в напряжение, от л и ч а ю щ и и с я тем, что, с целью увеличения допустимой скорости изменения входного сигнала, в него введены сумматор, элементы ИЛИ, шины кода смещения шкалы и дополнительные клапаны, входы синхронизации которых соединены с выходами блока управления, причем одни входы сумматора через дополнительные клапаны соединены с выходами шифратора, другие входал сумматора соединены соответственно с выходами одних элементов ИЛИ, входы которых через соответствующие дополнительные клапаны соединены с выходами шифратора, входы младших разрядов сумматорачерез другие элементы ИЛИ и дополнительные клапаны подключены к шинам кода смещения шкалы, а выходы сумматора через клапаны соединены с входами регистра.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР

213616, М.кл.Н 03 Е 13/17, 16.07.7

2,ЦЛфровые электроизмерительные Приборы. Под ред. В.М.Шпяндина, М., Энергия, 1972, с.298.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь напряжения в код | 1979 |

|

SU928634A2 |

| Преобразователь напряжения в код параллельно-последовательного уравновешивания | 1980 |

|

SU900442A2 |

| Преобразователь напряжения в код | 1975 |

|

SU729839A1 |

| Преобразователь напряжения в код | 1980 |

|

SU884126A1 |

| Функциональный преобразовательНАпРяжЕНия B КОд | 1979 |

|

SU818004A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Рециркуляционный преобразователь напряжения в код двойного уравновешивания | 1980 |

|

SU884129A1 |

| Вычислительный преобразовательНАпРяжЕНия B КОд | 1979 |

|

SU822347A1 |

| Преобразователь напряжения в код последовательного приближения | 1978 |

|

SU790290A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

Авторы

Даты

1978-03-25—Публикация

1976-03-18—Подача