1

Изобретение относится к области преобразования и кодирования информации и предназначено для представления аналоговой величины в виде кода.

Известны двухотсчетные нреобразователи угловых перемещений в код, которые используют в каналах глубокого и точного отсчетов преобразование «фаза-временной интервал- код 1. Для таких преобразователей характерна плохая стабильность электронной отсчетной части из-за на.чичия избирательных цепей, нуль-органов.

Известны также преобразователи считывания, снимающие информацию обычно в виде циклического кода 2. Однако в них необходимо при1менение специальных датчиков и дополнительных логических устройств для преобразования циклического кода в арифметический.

Известны преобразователи, отличительной особенностью которых является использование в канале точного отсчета электромеханической фазовой следящей системы. Код начала грубого отсчета может формироваться любым способом 3. Они характеризуются высокими требованиями к электромеханическому узлу, большим весом и габаритами.

Наиболее близким по технической сущности к изобретению является преобразователь угол - код, содержащий двухотсчетный синусно-косинусный вращающийся трансформатор, выход грубого отсчета которого соединен с формирователем-ограничителем, кварцевый генератор соединен через делитель частоты с

блоком считывания кОлТ,а грубого отсчета.

Такой преобразователь имеет малые разрешающую способность и точность (14-16 двоичных разрядов), плохую стабильность схемы при изменении температхры окружающей среды из-за наличия избирательных цепей н нуль-органов.

Цель изобретения - повыщение точности и разрешающей способности преобразователя. Это достигается тем, что в предлагаемый

двухотсчетный преобразователь введены фазовый детектор, генератор импульсов, реверсивный счетчик и блок управления реверсивным счетчиком, блок согласования отсчетов, блок памяти, блок ввода кода, синхронизатор, дополнительный делитель частоты, дешифраторы, сумматор, делитель напряжения и блок формирования синусоидальных сигналов. Выход точного отсчета синусно-косинусного вращающегося трансформатора через последовательно соединенные фазовый детектор, генератор импульсов и блок управления реверсивным счетчиком соединен с входом реверсивного счетчика, один из выходов которого подключен к одному пз входов блока согласЪванпя отсчетов, к другому входу которого подключей через блок памяти );ыход блока считывания грубого отсчета. Выход фазо1;о1о детектора соединен с выходом блока управления реверсивным счетчиком, выход формирователя-ограничителя через синхронизатор соединен с блоком считывания кода грубого отсчета. Выход старших разрядов реверсивного счетчика через последовательно соединенные блок ввода кода, дополнительный делитель частоты и одни из дешифраторов подключен к одно.му из входов блока фор.мирования синусоидальных сигналов, на другой вход которого через другой дешифратор подключен один из выходов делителя частоты. Другой выход делителя подключен к блоку ввода кода, выходы кварцевого генератора - к входам синхронизатора и дополнительного делителя. Выход младших разрядов реверсивного счетчика соединен с одним из входов унравляемого делителя напряжения. Один из выходов блока формирования синусоидальных сигналов через управляемый делитель напряжения и сумматор соединеи с входом фазового детектора, другой выход блока формирования синусоидальных сигналов соединен с одним из входов сумматора, а третнй выход - с входами грубого и точного отсчетов синусно-косннусного вран,а1ои1егося трансформатора.

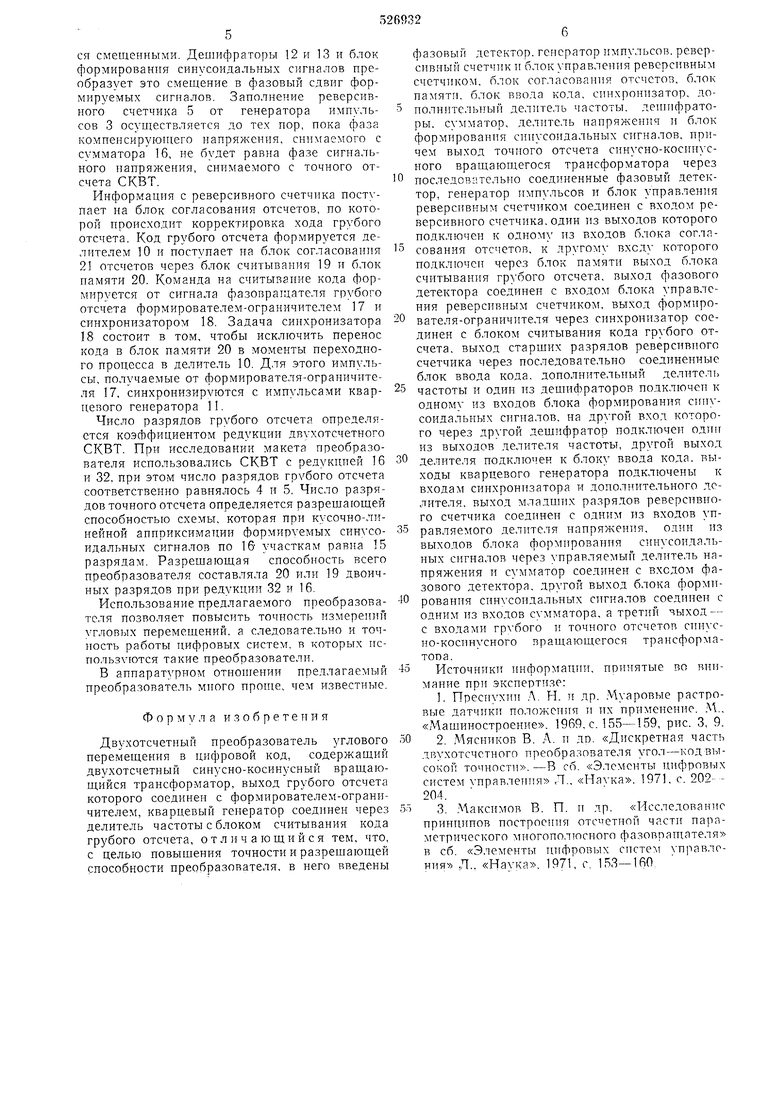

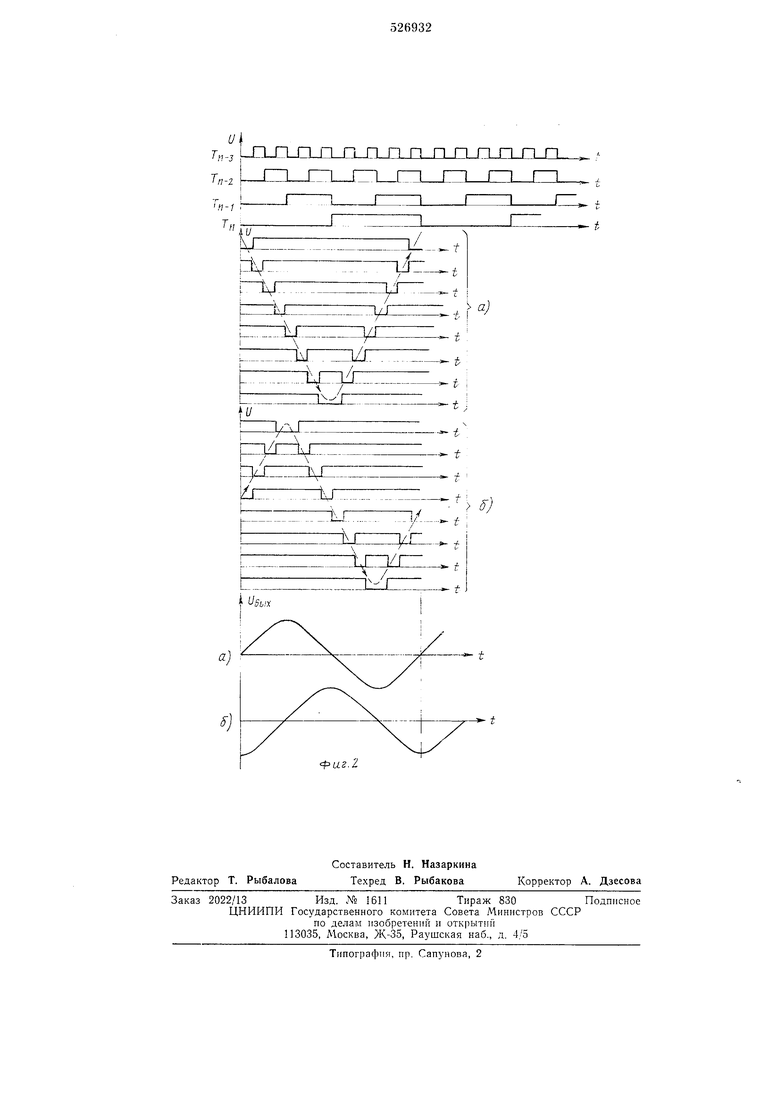

На фиг. 1 показана блок-схема двухотсчетиого преобразователя углового перемешения 15 цифровой код; на фиг. 2 приведена диаграмма, поясняющая принцип формирования синусоидальных сигналов.

Двухотсчетный преобразователь углового перемещения в цифровой код содержит двухотсчетный синуспо-косинусный вращающийся трансформатор (СКВТ) 1, фазовый детектор 2, генератор 3 импульсов, блок 4 управления реверсивным счетчиком, реверсивный счетчик 5, содержащий соответетвенно младшие и старшие разряды 6 и 7, блок 8 ввода кода, делители 9 и 10 частоты, кварцевый генератор 11, дешифраторы 12 н 13, блок 14 формирования синусоидальных сигналов, хнрав.тяемый делитель 15 напряжения, сумматор 16, формирователь-ограничитель 17, синхронизатор 18, блок 19 считывания кода грубого отсчета, блок 20 памяти н блок 21 согласования отсчетов.

Выход точного отсчета СКВТ 1 через последовательно соединенные фазовый детектор, генератор имнульсов и блок управления реверсивным счетчиком соединеи с входо.м реверсивного счетчика, выход которого подключен к одному из входов блока согласования отсчетов, к другому входу которого подключен через блок памяти выход блока считывания грубого отсчета. Выход фазового детек1ора соединен с входо.м блока управления реверсивным счетчиком, а формирователя-ограничителя через синхронизатор соединен с блоком считывания кода грубого отсчета.

Выход старших разрядов реверсивного счетчика через последовательно соединенные блок

кода, донолиител1)Иы1| делитель Macioты а одни из дешнфраюров нодк.лючсн к одио.му нз входов блока форм11ро1 а1111я сииусондальпых сигналов, на гои 11ход KOTopoio

через другой дешифратор подключен один из выходов делителя. Другой выход делителя подключен к блоку ввода кода. Выход кварцевого генератора подключен к входам синхронизатора и донолнителыюго делителя. Выход младших разрядов реверсивного счетчика еоединен с одним из входов унравляе.мого делителя напряжепия. Один из выходов блока фор.мирователя cинycoидaль iыx сигналов через управляемый делитель напряжения и

сумматор соединен с входом фазового детектора, другой выход блока формирования синусоидальных сигналов соединен с одним из входов су.мматора, а третий выход - с входами грубого и точного отсчетов синусокосинусного вращающегося трансформатора.

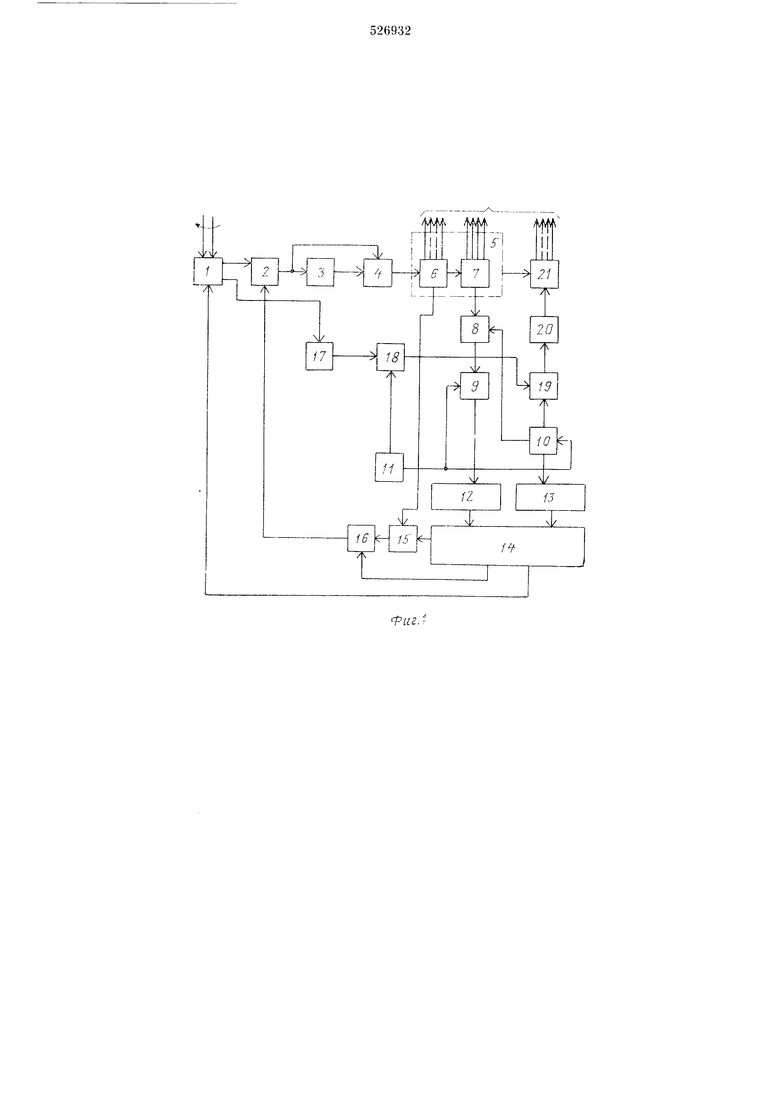

Диаграмма на фиг. 2 ноясияет принцип формирования компенсирующего синусоидального сигнала. С последних триггеров дополнительного делителя 9 инфор.мация ностунает на дешифратор 12. Две иоследовательиости и.мнульсов с дешифратора 12 (а - для формирования сиифазного сигнала, б---для формирования квадратурного сигнала) постунают на блок формирования синусоидальных сигиалов.

С нервого и второго выходов снимаются два сдвииутых на 90 напряжения, амнл Г1лда одного из них изменяетея в соответствии с кодом младших разрядов с реверсивного счетчика 5. Таким образо.м, фазовый сдвиг результирующего сигнала, спи.маемого с сумматора 16 и подаваемого па фазовый детектор 2, определяется геометрической суммой синфазного и частн квадратурного напряжений.

Предлагаемое устройсчво работает следующим образом.

В исходном состоянии реверсивный счетчик 5 и делители 9 и 10 находятся в исходном состоянии. Сигиал с точного отсчета (ЖВТ ностунает на фазовый детектор 2, на второй

вход которого иоступает компенснруюпхее нанряжение, в фор.мированни которого участвуют блокн 5, 8, 9, 10, 12, 14, 15, 16, образующие эталонный фазовращатель. Напряжение рассогласования, пропорциональное фазе между

сигнальным нанряжение.м, снимаемым с точного отсчета СКВТ и комие 1сирующим - с эталоиного фазовран1,ате;1я, ностунает на генератор нмиульсов и блок упра1 лен11я реверсивиым счетчиком, которые в зависимости от

знака и амнлитуды 1аг ряження рассогласования управляют режимом работы реверсивного счетчика (су.ммнрование или вычитание, частота занолнеиия). Код старших разрядов реверсивного счетчика 5 через блок ввода кода

записывается в донолннтел) делитель 9. Запись кода осуществляется один раз за период занолиения делителя 10. В результате периодического ввода кода в донолнительный делитель 9 кодовые комбинации в параллельпо работающих делителей частоты оказываются смещенными. Дешифраторы 12 и 13 и блок формирования синусоидальных сигналов преобразует это смещение в фазовый сдвиг формируемых сигналов. Заполнение реверсивного счетчика 5 от генератора импульсов 3 осуществляется до тех пор, пока фаза комненсируюп1его напряжения, снимаемого с сумматора 16, не будет равна фазе сигнального напряжения, снимаемого с точного отсчета сквт. Информация с реверсивного счетчика поступает на блок согласования отсчетов, по которой происходит корректировка хода грубого отсчета. Код грубого отсчета формируется делителем 10 и поступает на блок согласования 2 отсчетов через блок считывания 19 и блок памяти 20. Команда на считывание кода формируется от сигнала фазовращателя грубого отсчета формирователем-ограничителем 17 и синхронизатором 18. Задача синхронизатора 18 состоит в том, чтобы исключить перенос кода в блок памяти 20 в моменты переходного процесса в делитель 10. Для этого импульсы, получаемые от формирователя-ограничителя 17, синхронизируются с импульсами кварцевого генератора И. Число разрядов грубого отсчета определяется коэффициентом редукции двухотсчетного СКВТ. При исследовании макета преобразователя использовались СКВТ с редукцией 16 и 32. при этом число разрядов грубого отсчета соответственно равнялось 4 и 5. Число разрядов точного отсчета определяется разрешающей способностью схемы, которая при кусочно-линейной апприксимации формируемых синусоидальных сигналов по 16 участкам равна 15 разрядам. Разрешающая способность всего преобразователя составляла 20 или 19 двоичных разрядов при редукции 32 и 16. Использование предлагаемого преобразователя позволяет повысить точность измерений УГЛОВЫХ перемещений, а следовательно и точность работы цифровых систем, в которых ИСПОЛЬЗУЮТСЯ такие преобразователи. В аппаратурном отпонтепии предлагаемый преобразователь много проще, чем известные. Формула изобретения Двухотсчетный преобразователь углового перемещения в цифровой код, содержацдий Двухотсчетный синусно-косинусный вращающийся трансформатор, выход грубого отсчета которого соединен с формирователем-ограничителем, кварцевый генератор соединен через делитель частоты с блоком считывания кода грубого отсчета, отличающийся тем, что, с целью повыщепия точности и разрешающей способности преобразователя, в него введены фазовый детектор.генератор импульсов.реверсивный счетчик и блок управления реверсивным счетчиком, блок согласования отсчетов, блок памяти, блок ввода кода, синхронизатор, дополннтельный делитель частоты, дешифраторы, сумматор, делитель напряжения и блок формирования синусоидальных сигналов, причем выход точного отсчета синусно-косинусного вращающегося трансформатора через последовательно соединенные фазовый детектор, генератор импульсов и блок управления реверсивным счетчиком соединен с входом реверсивного счетчика, один из выходов которого подключен к одному из входов блока согласования отсчетов, к другому входу которого по.аключеп через блок памяти выход блока считывания грубого отсчета, выход фазового детектора соединен с входом блока управления реверсивным счетчиком, выход формирователя-ограничителя через синхронизатор соединен е блоком считывания кода грубого отсчета, выход старших разрядов реверсивиого счетчика через последовательно соединенные блок ввода кода, дополнительный делител1 частоты и одип из дешифраторов подключен к одному из входов блока формирования син соидальных сигналов, на другой вход которого через другой дешифратор подключен один из выходов делителя частоты, другой выход делителя подключен к блоку ввода кода, выходы кварцевого генератора подключены к входам сиихронпзатора и дополнительного делителя, выход младших разрядов реверсивного счетчика соединен с одним из входов управляемого делителя напряжения, один из выходов блока формирования сшусоидальных снгналов через управляемый делитель напряжения и сумматор соединен с в.хсдом фазового детектора, другой выход блока формирования синусоидальных сигналов соединен с одним пз входов сумматора, а третий яыход - с входами гр бого и точного отсчетов сннусно-косинусного вращающегося трансформатопа. Источники информации, поинятые во впимание при экспертизе: . Преснухтш Л. Н. и др. Муаровые растровые датчики положения и их примепение. .., «Машиностроение. 1969, с. 155-159, рис. 3, 9. 2. Мясников В. А. и до. «Дискретная часть двухотсчетного преобразователя угол-кодвысокой точности. -В сб. «Элементы цифровых систем управления Л., «Наука. 1971. с. 202- 204. 3. Максимов В. П. н др. «Исследование принципов построения отсчетной части параметрического многополюсного фазовращателя в сб. «Элементы цифровых систем управления Д.. «Наука. 1971, с, 153-160

Т„.., LTLnLTLn R П П П П ,

)

)

риг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU732955A1 |

| Двухотсчетный преобразователь углапОВОРОТА ВАлА B КОд | 1979 |

|

SU840995A1 |

| Двухотсчетный преобразователь углового перемещения в цифровой код | 1977 |

|

SU651389A2 |

| Двухотсчетный преобразователь угла поворота вала в код | 1979 |

|

SU924736A1 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU669374A1 |

| Преобразователь угла поворота вала в код | 1978 |

|

SU771115A2 |

| Преобразователь угла поворотаВАлА B КОд | 1979 |

|

SU813487A1 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU684578A1 |

| Компенсационный преобразователь угловых перемещений в код | 1975 |

|

SU546922A1 |

Авторы

Даты

1976-08-30—Публикация

1975-02-10—Подача