Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении схем ЦВМ и цифровой автоматики.

Известен реверсивный сдвигающий регистр, выполненный на потенциальных элементах «И-ИЕ («ИЛИ-НЕ), каждый разряд которого состоит из запоминающей схемы, представлениой триггером памяти и двумя коммутационными триггерами, и логической схемы, выполненной на двух элементах.

Для построения такого разряда необходимо восемь логических элементов. Время срабатывания разряда определяется суммой задержки запоминающей и логической схем.

Цель настоящего изобретения - повысить быстродействие сдвигового регистра при одновременном упрощепии его схемы.

Это достигается .путем включения в цепь триггеров памяти схемы запоминания дополп.ительпого логического элемента «И-НЕ («ИДИ-НЕ), играющего роль второго единичного плеча триггера, при этом триггеры памяти осуществляют функции памяти и управлепия сдвигом вправо (влево).

Последний выполнен в виде последовательно соединенных разрядов на логических потенциальных элементах «И-НЕ («ИДИ- НЕ) с .передачей прямого кода информации. Каждый разряд регистра состоит из триггера памяти с двумя единичными выходами н двух коммутационных триггеров.

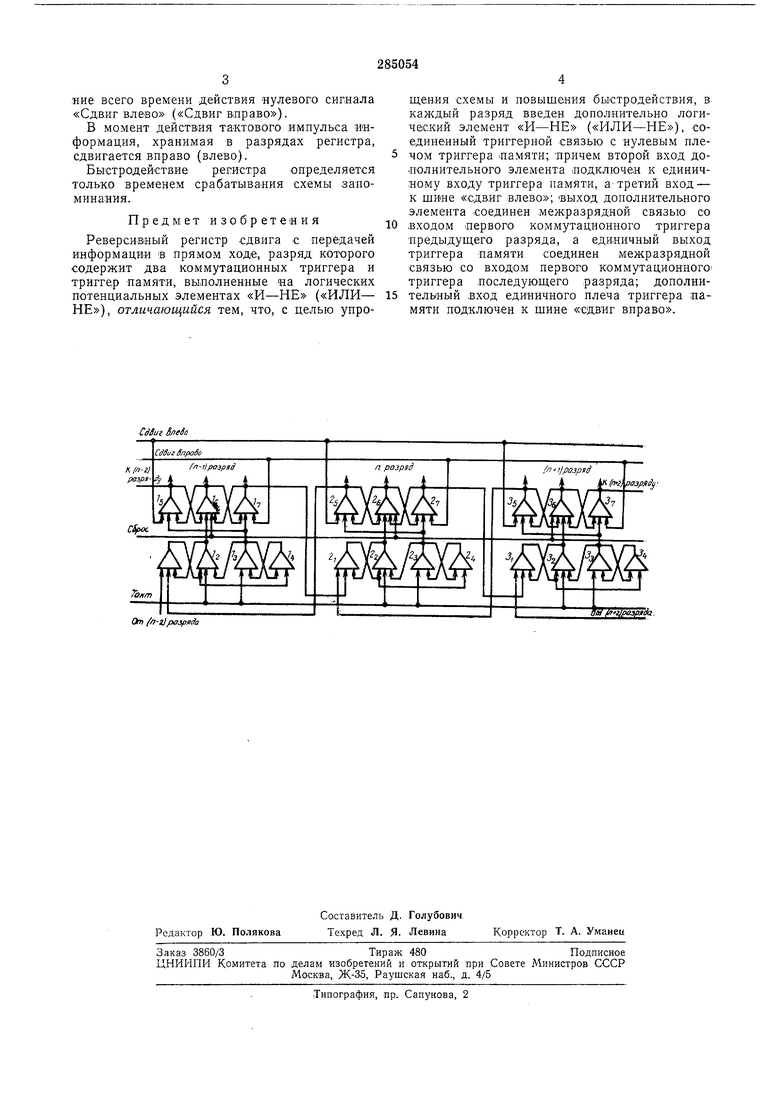

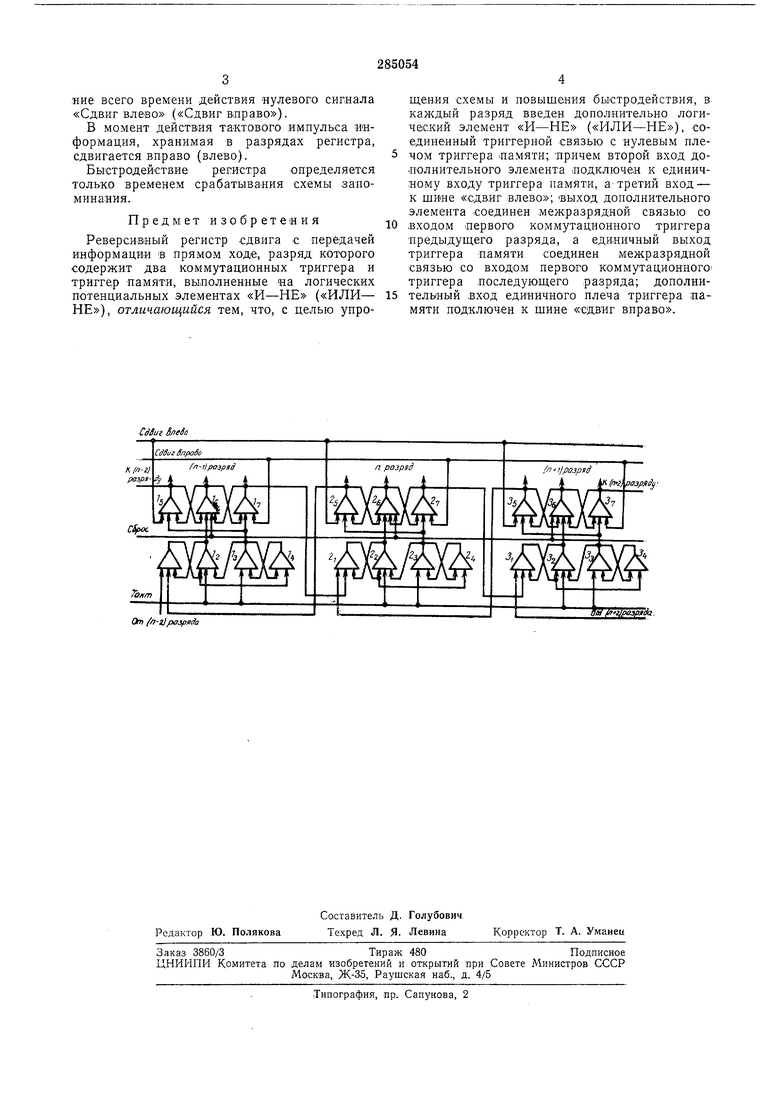

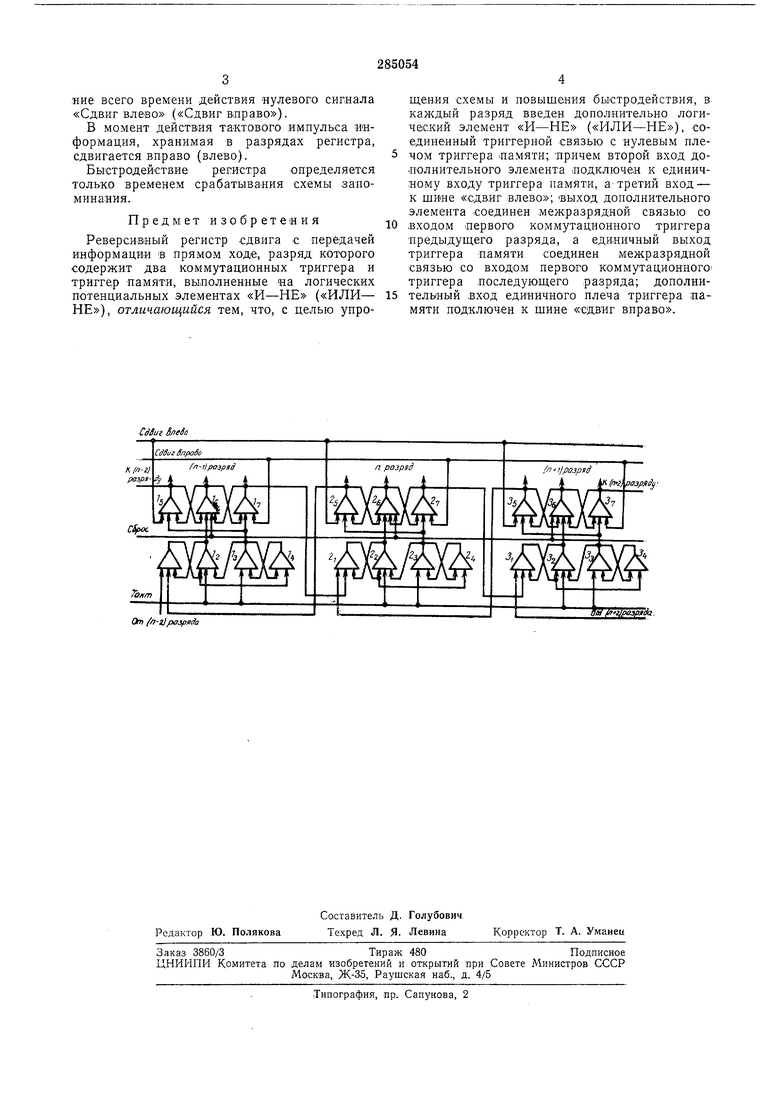

На чертеже показаны три разряда регистра: п; (rt+l) и (я-1).

Разряд (п-1) образован элементами Л- - IT. Элементы, li, 1 образуют первый коммутационный триггер, /3 и 1 - второй коммутационный триггер. Элементы 5 и /6 и дополнительный элемент «И-НЕ («ИДИ- НЕ) /7 образуют триггер памяти, который имеет один нулевой выход (./е) и два единичных (5, )Элементы 2i-2 образуют разряд п регистра, элементы - разряд (я+1) регистра. Назначение элементов с одинаковыми индексами во всех разрядах аналогично.

Предложенный сдвиговый регистр работает следующим образом.

При подаче единичного управляющего сигнала «Сдвиг вправо («Сдвиг влево) в триггерпую связь с элементами 1(, 2, Зц включаются соответственно элементы 1-, 2-„ 3-i (U, 2-, 3з); элементы 1, 2, З- (IT, 2т, Зт) отключаются lOT триггерпой связи, и на их выходе сохраняется сигнал логической единицы в течение всего времени действия нулевого сигнала «Сдвиг влево («Сдвиг влраво).

В момент действия тактового импульса информация, хранимая в разрядах регистра, сдвигается вправо (влево).

Быстродействие регистра определяется только временем срабатывания схемы запоминания.

Предмет изобретения

Реверсивный регистр сдвига с передачей информации В прямом ходе, разряд которого содержит два коммутационных триггера и триггер памяти, выполненные на логических потенциальных элементах «И-НЕ («ИЛИ- НЕ), отличающийся тем, что, с целью упрощения схемы и повышения быстродействия, в каждый разряд введен дополнительно логический элемент «И-НЕ («ИЛИ-НЕ), соединенный триггериой связью с нулевым плечом триггера памяти; прлчем второй вход дополнительного элемента подключен к единичному входу триггера памяти, а третий вход - к шине «сдвиг влево ; выход дополнительного элемента соединен .межразрядной связью со

входом первого коммутационного триггера предыдущего разряда, а единичный выход триггера памяти соединен межразрядной связью со входом первого коммутационного триггера последующего разряда; дополнительный вход единичного плеча триггера памяти подключен к шине «сдвиг вправо.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный регистр сдвига | 1974 |

|

SU593317A1 |

| Устройство сдвига | 1979 |

|

SU832599A1 |

| Реверсивный регистр сдвига | 1971 |

|

SU474853A1 |

| Реверсивный регистр сдвига | 1990 |

|

SU1721632A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ КОДОВ | 1967 |

|

SU201774A1 |

| Реверсивный регистр сдвига | 1979 |

|

SU780047A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Электропривод с устройством обнаружения отказов | 1990 |

|

SU1781811A1 |

| Устройство для сопряжения | 1979 |

|

SU842772A1 |

| Электропривод постоянного тока | 1985 |

|

SU1262677A1 |

Ciffue f/Tffo

OfTt /fJ-2 po3pff a

Даты

1970-01-01—Публикация