1

Изобретение относится к области дискретной автоматики и вычислительной техники.

.tisBecTeH реверсивный сдвигающий регистр, выполненный на потенциальных элементах И-iriL. (i LjLfi-JrlE), каждый разряд которого состоит из запоминающей схемы, представленной триггером памяти и двумя коммутационными триггерами и логической схемы, выполненной на двух элементах 1J.

педостатками такого регистра являются большое количество оборудования и низкое быстродействие.

Известен также .реверсивный регистр сдвига, построенный на логических элементах И-НЕ (ИЛИ-НЕ), каждый разряд которого содержит несимметричный D-триггер, включающий / 6-триггер памяти, основной коммутационный и вспомогательный RS-триггеры 2.

Недостатком такого реверсивного регистра сдвига является сложность снятия информации с выходов разрядов регистра, так как требуется дополнительная схема для дешифрации нахождения единичной информации на выходах единичных плеч триггеров памяти в режимах «сдвиг вправо и «сдвиг влево.

Цель изобретения - упрощение вывода информации из разрядов регистра и повышение надежности.

Указанная цель достигается тем, что в основной коммутационный У б-триггер каждого разряда введен элемент И-НЕ (И 1И-НЕ), первый вход которого соединен с нулевым

выходом триггера памяти последующего разряда, второй вход - с нулевым выходом основного коммутационного ,Ь-триггер а, выход- с дополнительными входами нулевого плеча основного и единичного плеча вспомогательного коммутационных ..-триггеров, информационный вход единичного плеча основного коммутационного ./ S-триггера соединен с нулевым выходом триггера памяти предыдущего разряда, дополнительный вход едиНИЧ.НОГО плеча основного коммутационного триггера и второй вход элемента И-НЕ (ИЛИ-НЕ) соединены соответственно с входами «сдвиг вправо и «сдвиг влево.

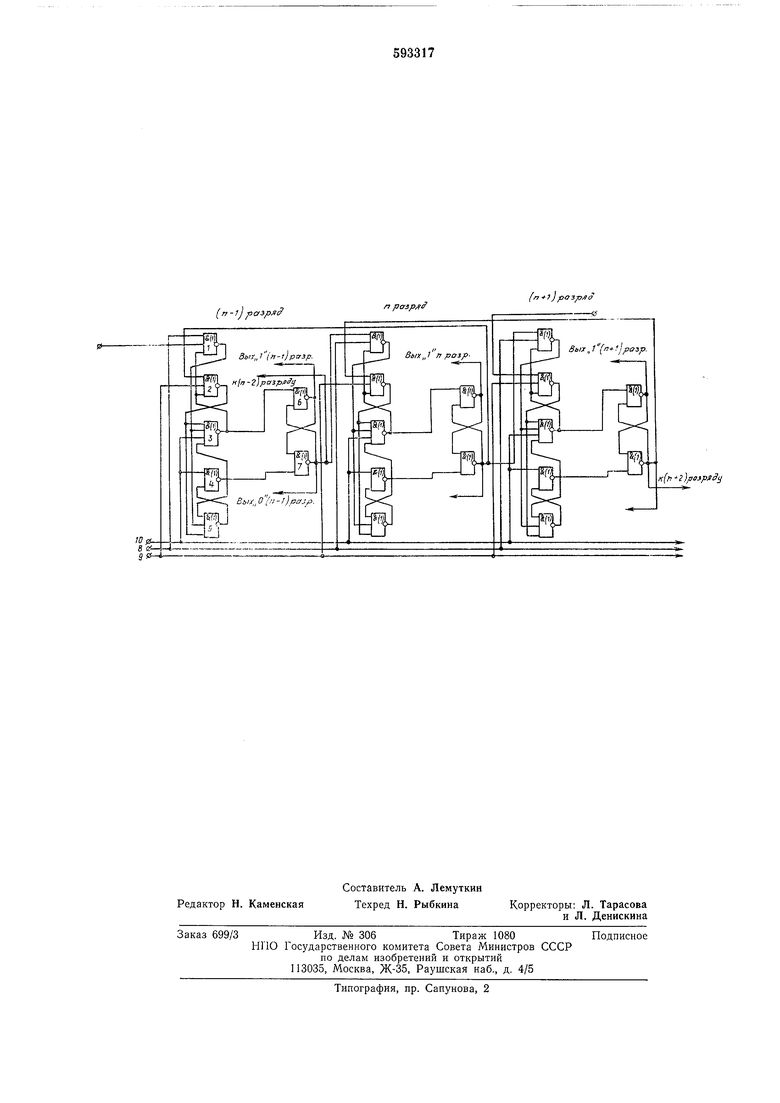

На чертеже представлена структурная схема предлагаемого устройства, где изображены три разряда регистра; п, () и (п-1). Разряд регистра состоит из двух коммутационных / 5-триггеров - основного и вспомогательного (элементы 1, 2, 3 и 4, 5 соответственно) и одного триггера памяти (элементы 6, 7).

В каждом разряде регистра сдвига коммутационный ./ S-триггер, принимающий информацию от соседних разрядов регистра (например элементы 1, 2, 3 для 1я-1 разряда), содержит дополнительный элемент И-НЕ (ИЛИ-НЕ), первый вход которого соединен с нулевым выходом триггера памяти последующего разряда, информационный вход единичного плеча этого же коммутационного триггера соединен с нулевым выходом триггера памяти предыдущего разряда, дополнительные входы единичного плеча основного коммутационного 5-триггера и элемента И-НЕ (ИЛИ-НЕ) соединены соответственно со входами «сдвиг вправо 8, «сдвиг влево 9. Тактовые импульсы подаются на вход 10.

Устройство работает следующим образом.

При подаче сигнала логической единицы на вход 8 «сдвиг вправо и логического нуля на вход 9 «сдвиг влево в каждом разряде регистра с нулевым плечом (для я-1|-го разряда, например элемент 3) основного коммутационного триггера включается основное единичное плечо (для п-1|-го разряда элемент 1), а на выходе элемента И-НЕ (элемент 2) на все время действия управляющих сигналов сохраняется сигнал логической единицы. Тогда в момент действия тактового сигнала информация, хранимая в разрядах регистра, сдвигается вправо.

При подаче сигнала логической единицы на вход 9 «сдвиг влево, и логического нуля на вход 8 «сдвиг вправо в триггерную связь с нулевым ллечом (элемент 3) основного коммутационного триггера включается элемент 2, а на выходе единичного плеча (элемент 1) сохраняется сигнал логической единицы на все время действия управляющих сигналов. Тогда в момент действия тактового сигнала информация, хранимая в разрядах регистра, сдвигается влево.

В предлагаемом реверсивном регистре сдвига независимо от режима работы (сдвиг вправо или влево) в каждом разряде информация снимается с одних и тех же выходов триггера памяти. Поэтому нет необходимости в дополнительных устройствах дешифрации

режима работы и определения рабочего плеча триггера памяти.

Кроме того, в предлагаемом реверсивном регистре сдвига исключена потеря информации при переходе от режима «сдвиг вправо к режиму «сдвиг влево, так как при переходе от одного режима сдвига к другому триггер памяти не коммутируется.

Формула изобретения

Реверсивный регистр сдвига, построенный на логических элементах И-НЕ (ИЛИ- НЕ), каждый разряд которого содержит несимметричный D-триггер, включающий RSтриггер памяти, основной коммутационный и вспомогательный / S-триггеры, отличающийся тем, что, с целью упрощения вывода информации из разрядов регистра и повышеПИЯ надежности, в основной коммутационный 5-триггер каждого разряда введен элемент И-НЕ (ИЛИ-НЕ), первый вход которого соединен с пулевым выходом триггера памяти последующего разряда, второй вход - с

нулевым выходом основного коммутационного / 5-триггера, выход -с дополнительными входами нулевого плеча основного и единичного нлеча вспомогательного коммутационных 7 5-триггеров, информационный вход единичного нлеча основного коммутационного RSтриггера соединен с нулевым выходом триггера памяти предыдущего разряда, дополнительный вход единичного плеча основного коммутационного триггера и второй вход элемента И-НЕ (ИЛИ-НЕ) соединены соответственно с входами «сдвиг вправо и «сдвиг влево.

Источники информации, принятые во внимание при экспертизе

1. Прангишвили И. В. и др. Микроэлектроника и однородные структуры для построения логических и вычислительных устройств, М., 1967, с. 43, рис. 1.18. 2. Авторское свидетельство СССР № 285054,

кл. Н ОЗК 23/04, 1969. n-JJ 1азря$ п разр (fj -f J ) K{r-2)

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный регистр сдвига | 1971 |

|

SU474853A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1970 |

|

SU285054A1 |

| -Разрядный регистр сдвига | 1977 |

|

SU746734A1 |

| Реверсивный регистр сдвига | 1979 |

|

SU780047A1 |

| Реверсивный счетчик | 1977 |

|

SU708516A2 |

| Реверсивный счетчик с последовательным переносом | 1974 |

|

SU516196A1 |

| Устройство для сопряжения | 1979 |

|

SU842772A1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Реверсивный регистр сдвига | 1990 |

|

SU1721632A1 |

| Реверсивный сдвигающий регистр | 1977 |

|

SU734809A1 |

Авторы

Даты

1978-02-15—Публикация

1974-04-02—Подача