(54) УСТРОЙСТВО СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Ассоциативный параллельный процессор | 1973 |

|

SU495664A1 |

| Аналоговое запоминающее устройство | 1975 |

|

SU598127A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1970 |

|

SU285054A1 |

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Устройство для контроля электрических цепей | 1987 |

|

SU1506398A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1971 |

|

SU297073A1 |

1

Изобретение относится к цифровой вычислительной технике и может найти применение в микропроцессорах для осуществления ускоренной операции сдвига информации влево-вправо в качестве регистра множителя-делителя арифметического узла, а также в быстродействующих приборах автоматики.

Известен реверсивный регистр сдвига, содержащий сдвиговые разряды и межразрядные переключатели, первый вход у которого соединен с выходом -предыдущего сдвигового разряда, а второй вход - с выходом последующего сдвигового разряда, причем сдвиговые входы сдвиговых разрядов объединены между собой 1.

Наличие в известном устройстве межразрядных переключателей обеспечивает реверсивное продвижение информации в сдвиговых разрядах, однако при этом значительно удлиняется временная протяженность последовательной структуры устройства, в результате чего быстродействие процесса сдвига информации существенно снижается.

Наиболее близким к предлагаемому по технической сущности является реверсивный

регистр сдвига, содержащий сдвиговые разряды, ключи 2. Однако это устройство обладает низким быстродействием за счет удлинения временной протяженности последовательной структуры устройства.

Цель изобретения - повыщение быстродействия устройства.

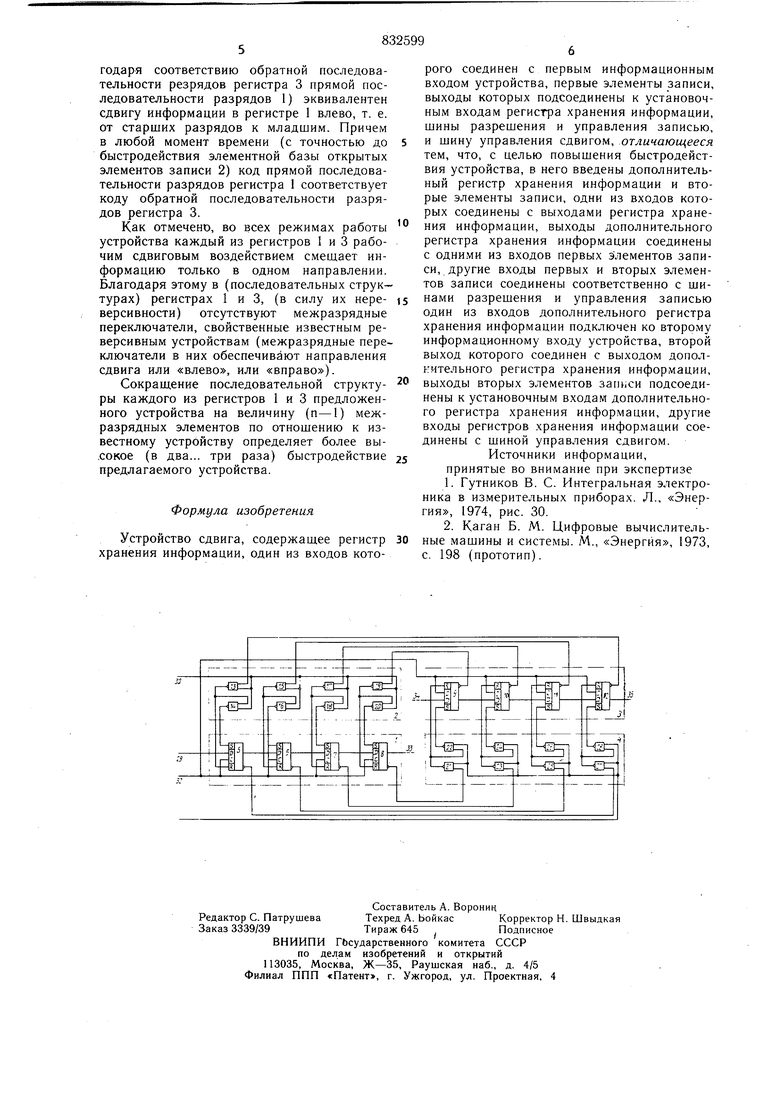

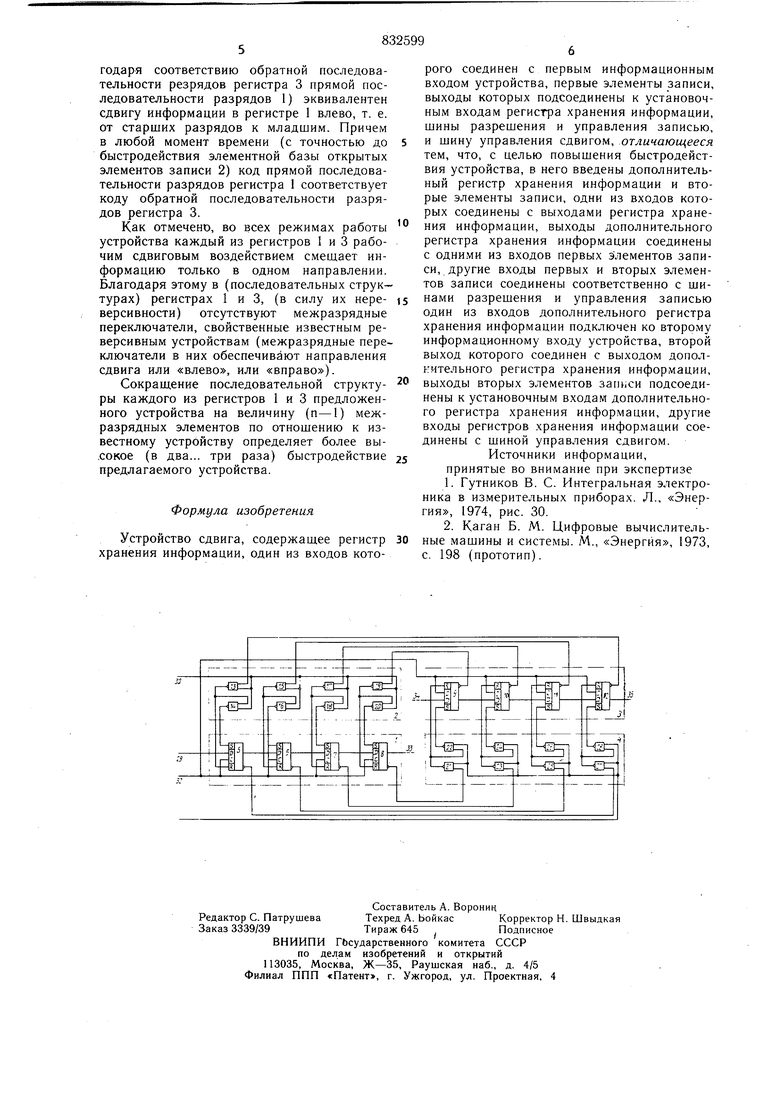

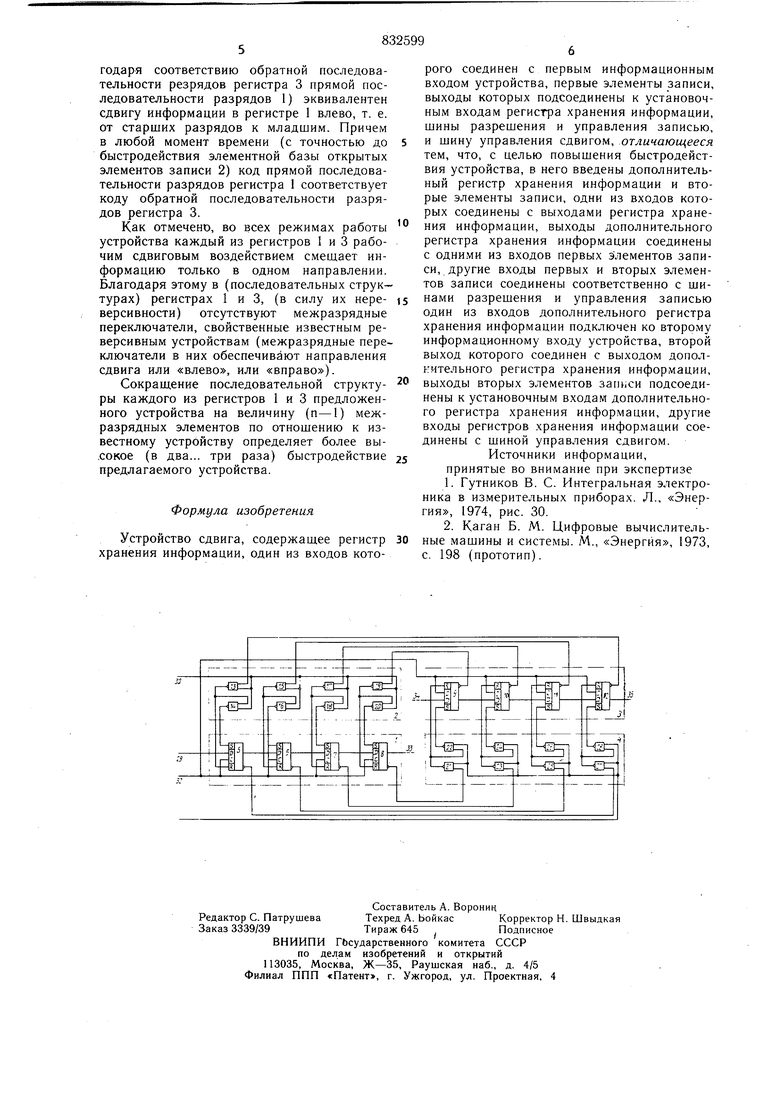

Поставленная цель достигается тем, что в устройство, содержащее регистр хранения информации, один из входов которого соединен с первым информационным входом устройства, первые элементы записи, выходы которых подсоединены к установочным входам регистра хранения информации, щины разрешения и управления записью, и щину управления сдвигом, введены дополнительный регистр хранения информации и вторые элементы записи, одни из входов которых соединены с выходами регистра хранения информации, выходы дополнительного регистра хранения информации соединены с одними из входов первых элементов записи, другие входы первых и вторых элементов записи соединены соответственно с щинами разрешения и управления записью, один из входов дополнительного регистра хранения информации подключен ко второму информационному входу устройства, второй выход которого соединен с выходом дополнительного регистра хранения информации, выходы вторых элементов записи подсоединены к установочным входам дополнительного регистра хранения информации, другие входы регистров хранения информации соединены с шиной управления сдвигом. На чертеже представлена функциональная схема предложенного устройства. Устройство содержит регистр 1 хранения информации, первые элементы 2 записи, дополнительный регистр 3 хранения информации, вторые элементы 4 записи, причем регистр 1 выполнен на триггерах 5-8, регистр 3 - на триггерах 9-12, первые и вторые элементы записи могут быть выполнены на элементах И-НЕ 13-28, первый (информационный) .вход 29 устройства шины разрешения записи 30 и 31 (управления записью), шину 32 управления сдвигом, первый выход 33 устройства и вторые вход 34 и выход 35 устройства. При параллельном вводе в устройство информации, подлежащей сдвигу, элементы 2 записи должны содержать по дополнительному входу в каждом разряде. Устройство работает следующим образом. Режим последовательного ввода информации в устройство. В данном режиме на шины 30 и 31 подаются соответственно запрещающий и разрешающий сигналы. Информация, подлежащая записи, начиная со старших разрядов, подается на первый вход 29 и соответствующим числом тактов, подаваемых на щину 32 управления сдвигом, устанавливается в регистр 1. В связи с разрешающим на шине 31 сигналом информация, установленная на регистре 1, принудительна записывается в регистр 3 обратной последовательности разрядов. Причем в любой момент времени (с тонностью до быстродействия элементарной базы элементов 4 записи код обратной последовательности разрядов регистра 3 соответствует коду прямой последовательности разрядов регистра 1. Возможен вариант последовательного ввода в устройство информации, начиная с младших разрядов. При этом на шины 30 и 31 подаются соответственно разрешающий и запрещающий сигналы. Информация, подлежащая записи, начиная с младших разрядов, подается на второй вход 34 и соответствующим числом тактов, подаваемых на шину 32 управления сдвигом, устанавливается в регистр 3. В связи с разрешающим на щине 30 сигналом, в любой момент времени (с точностью до быстродействия элементной базы элементов 2 записи) код прямой последовательности разрядов регистра 1 соответствует коду обратной последовательности разрядов регистра 3. Режим параллельного ввоДа информации в устройство. Вводимая в устройство параллельным образом информация может быть представлена прямой последовательностью разрядов (слева младшие разряды, справа - старшие разряды), либо обратной последовательности разрядов. При прямой последовательности разрядов вводимого кода информация подается на дополнительный вход (на чертеже не показан) элементов 2 записи. При этом ч рез элементы 4 записи (на шине 31 присутствует отпирающий сигнал) код обратной последовательности разрядов регистра 3 принимает значение кода прямой последовательности разрядов регистра 1, т. е. соответствует введенной информации. При обратной последовательности разрядов вводимого кода информация подается на дополнительный вход (на чертеже не показан) элементов 4. При этом через открытые элементы 2 записи (на шине 30 присутствует отпирающий сигнал) код прямой последовательности разрядов регистра 1 Принимает значение кода обратной последовательности разрядов регистра 3, т. е. соответствует введенной информации. Режим сдвига информации вправо. В данном режиме на шинах 30 и 31 присутствуют соответственно запирающий и отпирающий сигналы. На первый вход 29 подается нулевой логический уровень. Путем подачи на щину 32 управления сдвигом определенного числа тактовых импульсов записанная информация в регистре 1 сдвигается вправо (младшие разряды в сторону старших разрядов) на соответствующее число разрядов. При этом благодаря открытым элементам 4 записи по шине 31 в любой момент времени (с точностью до быстродействия элементной базы элементов 4 записи)код обратной последовательности разрядов регистра 3 соответствует коду прямой последовательности разрядов регистра 1. Режим сдвига информации влево. В данном режиме на шинах 30 и 31 присутствуют соответственно отпирающий и запирающий сигналы, на второй вход 34 подается нулевой логический уровень. Путем подачи на шину 32 управления сдвигом определенного числа тактовых импульсов записанная информация в регистре 3 сдвигается вправо (младщие разряды регистра 3 сдвигаются в сторону старших разрядов) на соответствующее число разрядов. Сдвиг информации вправо в регистре 3 (благодаря соответствию обратной последовательности разрядов регистра 3 прямой последовательности разрядов 1) эквивалентен сдвигу информации в регистре 1 влево, т. е. от старших разрядов к младшим. Причем в любой момент времени (с точностью до быстродействия элементной базы открытых элементов записи 2) код прямой последовательности разрядов регистра 1 соответствует коду обратной последовательности разрядов регистра 3.

Как отмечено, во всех режимах работы устройства каждый из регистров 1 и 3 рабочим сдвиговым воздействием смещает информацию только в одном направлении. Благодаря этому в (последовательных структурах) регистрах 1 и 3, (в силу их нереверсивности) отсутствуют межразрядные переключатели, свойственные известным реверсивным устройствам (межразрядные переключатели в них обеспечивают направления сдвига или «влево, или «вправо).

Сокращение последовательной структуры каждого из регистров 1 и 3 предложенного устройства на величину (п-1) межразрядных элементов по отношению к известному устройству определяет более вы.сокое (в два... три раза) быстродействие предлагаемого устройства.

Формула изобретения

Устройство сдвига, содержащее регистр хранения информации, один из входов которого соединен с первым информационным входом устройства, первые элементы записи, выходы которых подсоединены к установочным входам регистра хранения информации, шины разрешения и управления записью, и шину управления сдвигом, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены дополнительный регистр хранения информации и вторые элементы записи, одни из входов которых соединены с выходами регистра хранения информации, выходы дополнительного регистра хранения информации соединены с одними из входов первых элементов записи, другие входы первых и вторых элементов записи соединены соответственно с шинами разрешения и управления записью один из входов дополнительного регистра хранения информации подключен ко второму информационному входу устройства, второй выход которого соединен с выходом дополнительного регистра хранения информации, выходы вторых элементов запьси подсоединены к установочным входам дополнительного регистра хранения информации, другие входы регистров хранения информации соединены с шиной управления сдвигом.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-05-23—Публикация

1979-07-16—Подача