(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Устройство для сбора информации от многоразрядных дискретных датчиков | 1986 |

|

SU1529230A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1370643A2 |

1

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных комплексах для сопряжения ЭВМ между соСоЙ и с каналами передачи данных.

Известны устройства для сопряжения, содержащие буферное запоминающее устройство, в состав которого входят регистри, группы элементов И ввода информации и группы элементов И вывода информации,.распределитель ввода информации, распределитель выйода информации, регистр меток,сум- матер, схемл сравнения,регистры констант, узел управления 1.

Недостаток этих устройств состоит в больших аппаратурных затратах.Наиболее близким к предлагаемому по технической сущности является устройство для сопряжения, содержащее оперативное запоминающее устройство с группой элементов И по числу разрядов регистров сдвига, реверсивный тактовый распределитель, элемент задepжки, триггер, формирователь импульсов сдвига, первые входы М-ой группы элементов И соединены с М-ым разрядом входной шины, выходы элементов И соединены с одноименными разрядами М-го сдвисаюшего регистра.

вторые входы элементов И одноименных разрядов всех групп подключены к соответствующим выходам реверсивного тактового распределителя, первый вход которого соединен с выходом триггера и входом формирователя импульсов сдвига, выход которого соединен с шиной сдвига, второй вход реверсивного тактового распределителя

0 соединен с шиной синхронизации ввода и одним из входов элемента задержки, второй вход которого подключен к шине синхронизации, а выход соединен с первым входом триггера, второй вход

5 которого соединен с шиной синхронизации вывода. В этом устройстве входной код поступает на входы элементов И, вторые входы которых управляются сигналами с выходов реверсивного

0 распределителя. Сдвиг реверсивного распределителя вправо осуществляется сигналом Синхронизация ввода после окончания записи в соответствующие разрядил регистров входного кода.

5 Вывод информации происходит из последних разрядов регистров сдвига и сопровождается сигналом Синхронизация вывода ,который поступает на вход триггера. Триггер формирует сигнал

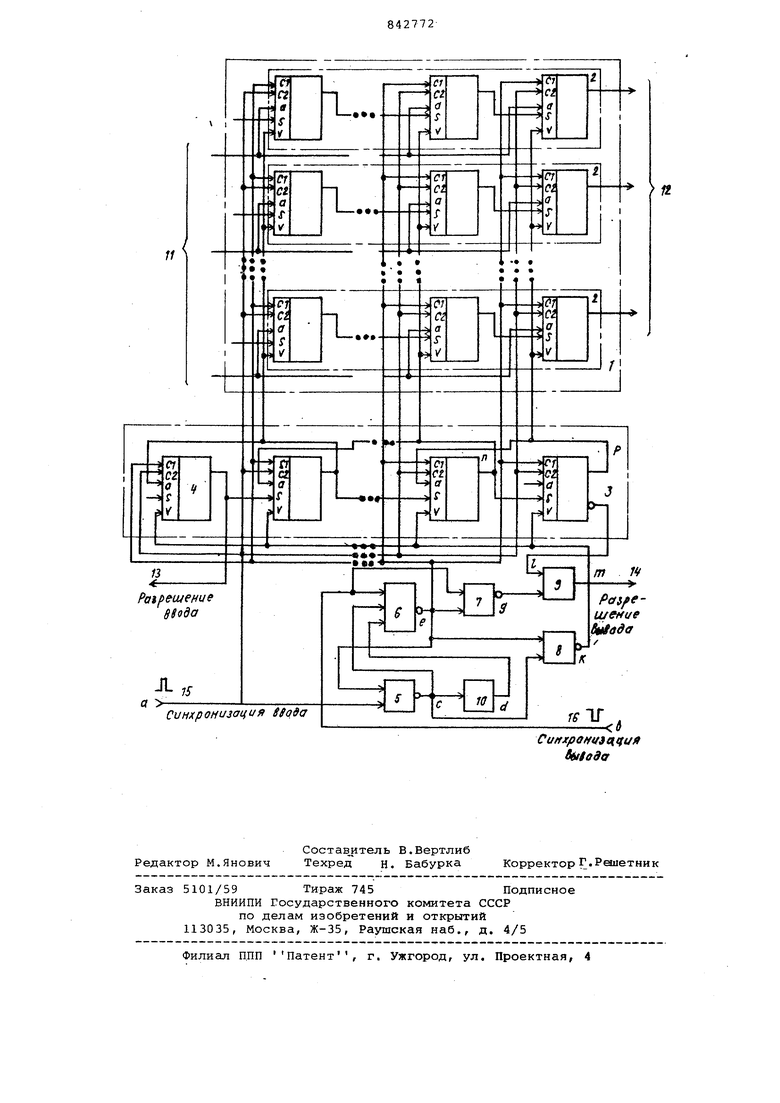

0 сдвига влево для реверсивного распределителя и запускает формирователь цмпульсов сдвига, который форкирует сигнал, сдвигающий информацию, записанную в сдвиговых регистрах, на оди разряд вправо. Устранение неопределенности при совпадении сигналов .Синхронизация ввода и Си нхрониза ция давода осуществляется элементом задержки, который синхронизирует ся сигналом Синхрониз щия и не пропускает сигнал Синхронизация ввода на вход триггера в момент действия сигнала Синхронизация вывода 2. Недостатками этого устройства явля низкая скорость обмена информацией из-за невозможности совмещения операций записи и считывания, низкая достоверность при передаче информации, так как отсутствие блокировки ввода-вывода может привести к перепол нению регистра и к приему ложной информации принимающей машиной, а такж сложность устройства из-за необходимости создания специальных синхронизирующих сигналов. Цель изобретения - увеличение быс родействия и достоверность передачи информации. Поставленная цель достигается тем что в устройство, содержащее блок памяти, выполненный гна регистрах сдвига, реверсивный распределитель и эле мент задержки, причем информационные выхдды регистров сдвига являются соо ветствующими информационными выходам устройства, введены четыре элемента И-НЕ, элемент И и триггер дополнительного разряда реверсивного.распре делителя, причем информационные входы регистров сдвига являются соответствующикт информационными входами устройства, входы синхронизиции сдви га соединены с входами синхронизации реверсивного распределителя и триггера дополнительного разряда реверсивного распределителя и выходом первого элемента И-НЕ, а входы 15 синхронизации записи соединены с входом синхронизации ввода устройства, входами синхронизации записи реверсивного .распределителя и триггер дополнительного разряда реверсивного реопределителя и первым входом второ го элемента Н-НЕ, вторым входом подключенного к первым входам первог и третьего элементов И-НЕ и входу сингфонизации вывода устройства, управляющие входа разрядов регистров соединены соответственно с информационными выходами одноименных разрядов реверсивного распределителя информационный выход последнего разряда и управляющий вход которого сое динены соответственно с информационными входом и управляющим входом триггера дополнительного разряда реверсивного распределителя, управляющим входом подключенного к выходу четвертого элемента И-НЕ, первый вход которого подключен к выходу третьего элемента И-НЕ, второму входу первого элемента И-НЕ и через элемент задержки к третьему входу первого элемента И-НЕ, выходом подключенного ко вторым входам четвертого и третьего элементов И-НЕ, выход которого и управляющий выход реверсивного распределителя подключены соответственно к первому и второму входам элемента И, выход которого является выходом разрешения вывода устройства, информационный выход триггера дополнительного разряда реверсивного распределителя соединен с выходом разрешения ввода устройства и. информационным входом реверсивного распределителя. На чертеже представлена блок-схема устройства. Устройство содержитблок 1 памяти на регистрах 2 сдвига, реверсивный распределитель 3, триггер 4 дополнительного разряда реверсивного распределителя 3, второй 5, первый б, третий 7 и четвертый 8 элементы И-НЕ, элемент И 9, элемент задержки 10, информационные входы 11 и выходы 12 устройства, входы разрешения ввода 13 и вывода 14 устройства, входы синхронизации 15 ввода и 16 вывода. Устройство работает следующим образом. Перед началом работы все разряды реверсивного распределителя 3, за исключением первого,, находятся в нулевом состоянии, а в первом записа, поэтому на управляющие входы первых разрядов регистров 2 подается уровень логической , разрешающий запись информации в эти разряды по информационным входам, На управляющие входы всех остальных pJlЗpядoв регистров 2 с выходов jje. верси вного распределителя 3 подаегся уровень логического О, разрешающий сдвиг информации, но запрещающий запись по информационным входам. С выхода дополнительного (последнего) разряда реверсивного распределителя 3(триггера 4) по выходу 13 в передающую машину подается сигнал, разраиающий ввод информации в устройство. Сигнал нулевого уровня с инверсного выхода нулевого разряда (управляющего выхода) реверсивного ;распределителя 3 через элемент И 9 по выходу 14 запрещает вывод информации в принимающую машину. На вход 15 из передающей машины поступает уровень логического О, поэтому на выходе И-НЕ 5 элемента задержки 10 и на втором и третьем входе элемента И-НЕ б имеются уровни . На вход 16 из принимающей машины подается уровень зультате на выходе элемента И-НЕ 6 имеют уровень Q, который подается на вход элемента И-НЕ 8, обеспечивая на его выходе и на управляющих входах разрядов реверсивного распределителя уровень , разрешающий запись информации в них по информационным входам. Сигнал нулевого уров ня с выхода элемента И-НЕ 6 подается также на вход элемента И-НЕ 7 и обес печивает на его выходе уровень логической . Единичный импульс синхрониэации ввода из передающей машины проходит на вход элемента И-НЕ 5, не изменяя уровня на его выходе, так как на второй вход элемента И-НЕ 5 подан уровень Р. По заднему фронту импульса синхронизации ввода, поступающего на входы С2 синхронизации за писи, происходит запись информации в первые разряды регистров 2, так как на управляющих входах в них присутствует уровень , разрешающий запись, и осуществляется сДвиг влево в реверсивном распределителе 3, так как на управляющие входы всех его разрядов ,с выхода элемента И-НЕ 8 подается уровень. , разроиающий запись информации. Поэтому после окончания импульса синхронизации вво да первый разряд реверсивного распре делителя 3 переходит в состояние и единичный сигнаш с его инвер сного выхода проходит на выход элемента И 9, так как на другом входе элемента И 9 действует сигнал единич ного уровня с выхода элемента И-НЕ 7 Таким образом, после записи, кода в первые разряды регистров 2 из передающей машины с выхода элемента И 9 в принимающую машину подается сигнал, разрешающий вывод информации и из первого разряда реверсивного распределителя 3 сдвигается в его второй разряд, с выхода которого единичный уровень подается на входы управления вторых разрядов регистров 2. После окончания второго импульса синхронизации ввода происходит запис кода с входом 11 во вторые разряды регистров 2, а , записанная во втором разряде реверсивного распределителя 3, сдвигается в его третий разряд. Следовательно, при приеме устройством сопряжения каждого параллельного кода по сигналу Синхронизация ввода происходит сдвиг 1 в реверсивном распределителе 3 влево на один разряд. Так происходит до записи кода в последние разряды регистров 2, когда i иЬ предпоследнего разряда реверсивного распределителя сдвигаетсд в его дополнительный разряд. В этом случае снимается сигнал разраиения ввода на вы ходе 12, что свиДетельс твует о запол нении всех регистров 2 блока 1 памяти. Принимающая ЭВМ при наличии сигна ла Разрешение вывода на выходе 14 с выхода элемента 19 может в любой момент начать считывать информацию из ре гистров 2 блока 1, подав на вход 16 импульс синхронизации нулево-, го уровнд. Этот импульс поступает на вход элемента И-НЕ 6. По переднему фронту этого импульса происходит считывание параллельного кода из первых разрядов регистров 2. При несовпгщении во времени с импульсом синхрониЭсщии ввода импульс синхронизации вывода формирует на выходе элемента И-НЕ 6 импульс единичного уровня и равной ему длительностью, который подается на входы синхронизации сдвига С1 каждого разряда всех регистров 2 и реверсивного распределителя 3. Поэтому по заднему фронту импульса с выхода элемента И-НЕ 6 происходит сдвиг информации на один разряд вправо во всех заполненных разрядах регистров 2, так как на управляющих входах этих разрядов действует сигнал нулевого уровня с выходов реверсивного распределителя 3, разрешающий сдвиг вправо. Одновременно поступает сигнал единичного уровня с выхода элемента И-НЕ 5. Поэтому на выходе элег-гента И-НЕ 8 формируется сигнал нулевого уровня, который подается не входы управления всех разрядов реверсивного распределителя 3, разраиая тем самым сдвиг вправо.Поэтому по заднему фронту сигнала с выхода первого элемента И-НЕ б проходит сдвиг 1 в предыдущий разряд реверсивного распределителя. Окончание сигнала нулевого уровня на выходе элемента И-НЕ 8 происходит позднее окончания импульса на выходе элемента K-tiB б на время задержки сигнала элементом И-НЕ 8, что обеспечивает надежный сдвиг вправо. Таким образом, несовпадение импульсов Синхронизация ввода и Синхрони3 аци 0 шдвода продви гает 1 в реверсивном рдспределителе 3 и ииформгщию в регистрах 2 на один шаг вправо до тех пор, пока эта занесется в перш:1й разряд реверсивного распределителя. В этом случае на шдходе элемента И 9 появляется уровень, снимающий на выходе 14 сигнал Разрешение вывода . В случае совпадения во времени |импульсов синэфонйзации вывода и синхронизации ввода на выходе элемента И-НЕ 5 формируется сигнал нулевого уровня, который поступает.на второй вход элемента И-НЕ 6, и через время, определяемое элементом задержки 6, натретий вход элемента И-«Е б. Одновременно сигнал нулевого уровня поступает на вход элемента И-НЕ, 8, поддерживая на его выходе единичный уровень, кото1%1й подается на входы управления каждого реверсивного распределителя, разрешая тем самым режим сдвига влево. Время задержки в элементе задержки б выбирается в эавиримости от времени переходных проце сов в регистрах 2 и в реверсивном распределителе Зи длительности сигнёша Синхронизация ввода на входе 15. Очевидно, что в случае совпадения во времени импульсов Синхронизация ввода и Синхронизация вывода задний отрицательный фронт сигнала на выходе элемент И-НЕ 6 формируется не ранее, чем че рез время задержки элемента 10, пос ле окончания импульса синхронизация ввода. Поэтому в этом случае независимо происходит запись информации из передающей машины в соответс вующие разряды регистров 2 и вывод информации из первых разрядов .регис ров 2 в принимающую машину (по пере нему фронту импульса синхронизации вывода). При этом по заднему фронту импульса Синхронизация ввода пр исходит сдвиг 1 на один разряд влево в реверсивном распределителе 3 и через время, большее времени за держки на элементе 10, формируется задний фронт сигнала на выходе элемента И-НЕ,6, по которому происходит сдвиг информации в регистрах 2 и в реверсивном распределителе 3 на один разряд вправо. Если импул Синхронизация вывода заканчи- с вается раньше, чем сигнал с выхода элемента задержки 10, то после его окончания на выходе элемента И-НЕ 7 формируется сигнал нулевого уровня, который через элемент И 9 снимает сигнал Разрешение вывода до окон чания сигнала на выходе элемента задержки 10. Это позволяет избежать повторного вывода одной и той же информации., Таким образом, применение предлагаемого устройства позволяет организовать обмен информации при любом соотнесении скоростей работы передаю щей и принимающей машин. Быстродейст вие устройства определяется быстродействием применяемой элементной базы. Для своего функционирования уст ройство йе требует создания специаль ных синхронизирующих импульсов, что позволяет сопрягать универсальные выпycкae ыe промышленностьюэвм, которыёу как правило/при выводе информа ции выдают только один импульс сопровождения информации. Кроме того, устройство |Обеспечивает высокую надежность неискаженной передачи инфор маци при относительно небольшой сло ности -и объеме оборудования. Формула изобретения Устройство для сопряжения, содержащее блок памяти, выполненный на ре гистрах сдвига, реверсивный распределитель и элемент задержки, причем ; информационные выходы регистров сдвига являются Соответствующими информационными выходами устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены четыре элемента И-НЕ, элемент И и триггер дополнительного разряда реверсивного распределителя, причем информационные входы регистров сдвига являются соответствующими информационными входами устройства, входы синхронизации сдвига соединены с входами синхронизации реверсивного распределителя и триггера дополнительного разряда реверсивного распределителя и выходом первого элемента И-Н а выходы синхронизации записи, соединены с входом синхронизации ввода устройства,входами синхронизации записи реверсивного распределителями триггера дополнительного разряда реверсивного распределителя и первым входом второго элемента И-НЕ, вторым входом подключенного к первым входам первого и третьего элементов И-НЕ и входу синхронизации вывода устройства, управляющие входы разрядов регистров сдвига соединены соответственно с информационными выходами одноименных разрядов реверсивного распределителя, информационный выход последнего разряда и управляющий вход которого соединены соответственно с информационным входом и управляющим входом триггера дополнительного разряда реверсивного распределителя, управляющим входом подключенного к выходу четвертого элемента И-НЕ первый вход которого подключен к выходу третьего элемента И-НЕ, ВТОРОМУ входу первого элемента И-НЕ и через элемент задержки к., третьему входу первого элемента И-НЕ,выходом подключенного ко вторым входам четвертого и третьего элементов И-НЕ, выход которого и управляющий выход реверсивного распределителя подключены соответственно к первому и второму входам элемента И, выход которого является выходом разрешения вывода устройства, информационный выход триггера дополнительного разряда реверсивного распределителя соединен с выходом разрешения ввода устройства и информационным входом реверсивного распределителя. Источники информации/ принятые во внимание при экспертизе 1.Авторское свидетельство СССР 602934, кл. G Об F 3/04, 1975. 2.Авторское свидетельство СССР № 401999, кл. G 06 F 13/02, 1971 (прототип).; Синхронизация

1t

Синз1рвн«9в(чия fitloSff iSada

Авторы

Даты

1981-06-30—Публикация

1979-07-09—Подача