Изобретение относится к области вычислительной техники и может быть использовано в качестве самостоятельного узла-частотомера, входного преобразователя информации для цифровых вычислительных машин (ЦВМ), составной части частотно-импульсных вычислительных устройств.

Известен преобразователь частоты в код, содержащий вычитающее устройство, счетчик, дешифраторы, схемы совпадения, схемы сборки и регистр.

Недостатком известного устройства является значительное количество оборудования (триггеров), необходимое для его изготовления.

Целью изобретения является построение преобразователя частоты в код при меньших затратах оборудования, но сохраняющего точностные и динамические характеристики известного преобразователя.

Эта цель достигается тем, что выходы вычитаюш,его устройства подключены ко входам первой схемы сборки, выход которой соединен со входом счетчика, и к первым входам первой группы схем совпадения, выходы которых соединены со -входами -регистра; вторые входы этих схем совпадения подключены к выходам-первого-дешифратора, входы которого соединены с выходам«--разря.дов-счетчи-ка и со входами второго дешифратора, выходы которого соединены с первыми входами второй

группы схем совпадения; ко вторым входам этих схем совпадения подключены шины опорных частот, а выходы пх подсоединены ко входам третьей группы схем совпадения, вторые входы которых подключены к выходам второй группы схем сборки, входы которых соединены с выходами разрядов регистра и с выходами первого дешифратора, а выходы - со входами третьей схемы сборки, выходы которой соединены со входом вычитающего устройства.

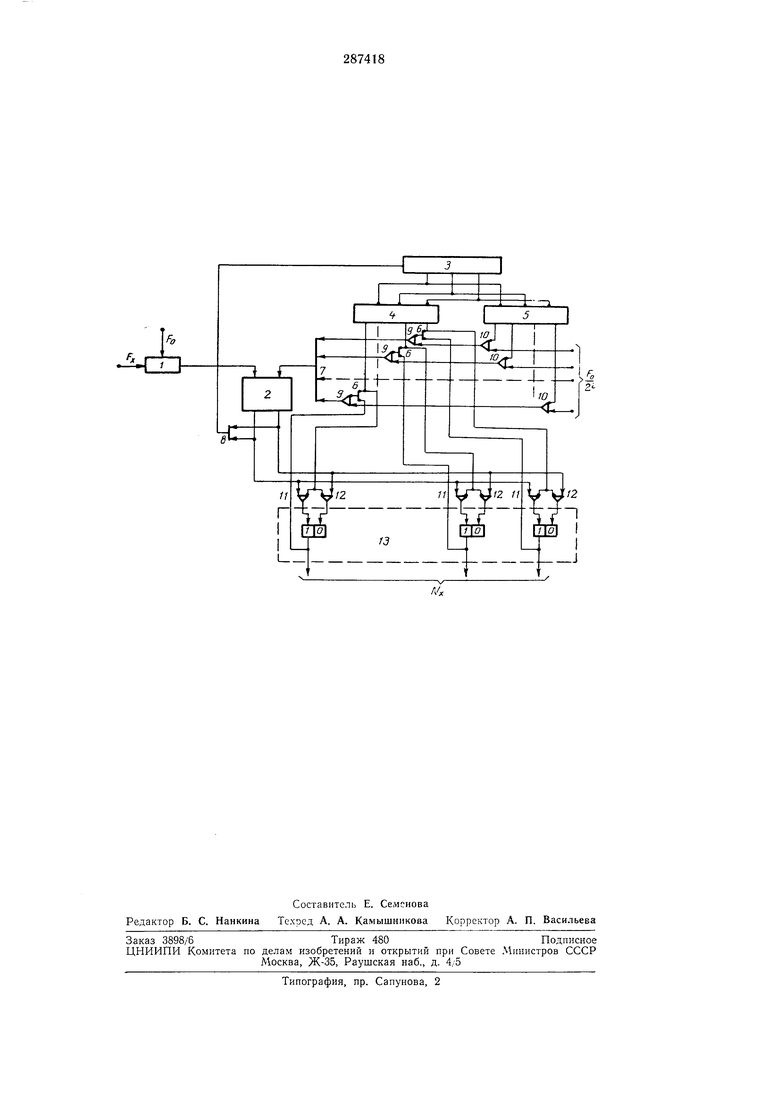

Предложенное устройство, изображенное на чертеже, состоит из блока синхронизации /, вычитающего устройства 2, счетчика 3, дещифраторов 4 и 5, схем сборки 6, 7, 8, импульсно-цотенцнальных схем совпадения 9- 12 и выходного регистра /5.

Вход частоты F соединен с блоком синхронизации /, к другому входу которого подключена шина опорной частоты /о. Выход блока / соединен со входом вычитающего устройства 2, оба выхода вычитающего устройства подключены к импульсным входам импульсно-потенциальных схем совпадения П и 12, соединенных потенциальными входами с соответствующими выходами дещифратора 4, выходы схем совпадения соединены с установочными входами триггеров выходного регистра 13. Кроме этого, выходы вычитающего устройства подключены ко входам схемы сборки 8, выход которой соединен со входом счетчика 3, выходы триггеров последнего подключены ко входам дешифраторов 4 и 5. Выходы дешифратора 5 соединены с потенциальными входами импульспо-потенциальных схем совпадения 10, к ИМПУЛЬСНЫМ входам которых F F подключены шины опорных частот , - ,.. ., Выходы схем 10 соединены с импульсными входами импульсно-потенциальных схем совпадения 9, выходы которых подключены ко входам схемы сборки 7, выход .которой соединен со входом вычитающего устройства. К потснциальным входам схем совладения 9 подключены выходы потенциальных схем сборки 6, входы которых соединены с соответствуюш,ими выходами дешифратора 4 и единичными выходами триггеров выходного регистра 13. При поступлении на вход устройства частоты Fjf первый имиульс этой частоты, пройдя через вычитающее устройство, переводит счетчик 3 из состояния 00... 00 в состояние 00... 01. При этом дешифратор 5 выдает разрешающий потенциал на схему совпадения 10, управляющую прохождением старщей опорной частоты - . Одновременно дешифратор 4 выдает разрещающий потепциал на схему 5 (через схему сборки 6} и схемы совпадения У/ и 12, стоящие на входе старшего триггера выходного регистра 13, в результате старшая Р опорная частота -- через схему совпадения 9 и сборки 7 поступит на второй вход вычитающего устройства 2 для контроля. Контроль заключается в проверке условий F, либо /. При выполнении какого-либо из условий появляется разностный импульс на том или ииом выходе вычитающего устройства и записывает «О или «1 в старший разряд выходного регистра IS. В случае положительного исхода проверки (зап;1сь «1) выходной сигнал старшего триггера выходного регистра 13 дублирует разрешающий потенциал дешифратора 4, поступающий на схему 9, управляющую прохождением старшей опорной частоты -. Этот же ра.зиостнь1Й импульс переводит код счетчика 5 й,з состояния 00 ... 01 в состояние 00 ... 10. Црд-,91ом,деи1ифратор 5 выдает разрешающий потеии,нал Н;а. две схемы совпадения, управляющие Прохождением опорных частот 7j -.Дещифратор 4 выдает разрешающий сигнал ТОЛЬКО на одну схему совпадения 9, управляющую прохождением опорной частоты - . На вход вычитающего устройства в укаfзанном случае поступит набор частот flj- + + т. е. производится проверка условий F :2 - а, 4- - либо, F а, - + - , X 22-- 2 22 0при F. .-- (при первом исиытании); 1при fx (при первом испытании). В зависимости от результата этого испытания на том или ином выходе вычитающего устройства появляется разиостпый импульс,, записывающий «О или «I в старший разряд выходиого регистра и производящий переключение счетчика 3. Рассмотренный процесс продолжается до lex пор, пока не будут проверены услов-ия, аналогичные приведенным выше, для каждого разряда выходного регистра. По окончании цикла преобразования контрольный счетчик 3 устансвится в состояние ОО . . . 00, дешифратор 5 выдает разрешающие потенциалы на пес схемы совпадения 10, дешифратор 4 выдаст на всех выходах запрещающие потенциалы. Из всех схем совпадения 9 будут открыты только те, на которые подается разрешающий потенциал с триггеров выходного регистра 13. Предмет изобретения Преобразователь частоты в код, содержащий вычитающее устройство, счетчик, дешифраторы, cxejMbi совиадения, схемы сборки и регистр, отличающийся тем, что, с целью сокращения оборудования, выходы вычитающего устройства подключены ко входам первой схемы сборки, выход которой соединен со входом счетчика, и к первым входам первой группы схем совпадения, выходы которых соединены со входами регистра, а вторые входы этих схем совпадения подключены к выходам первого дешифратора, входы которого соединены с выходами разрядов счетчика и со входами второго дещифратора, выходы которого соединены с первыми входами второй группы схем совпадения, ко вторым входам этих схем совпадения подключены шины опорных частот, а выходы их подсоединены ко входам третьей группы схем совпадения, вторые входы которых подключены к выходам второй группы схем сборки, входы которых соединены с выходами разрядов регистра « с выходами первого дещифратора, а выходы со входамч третьей схемы сборки, вы.ходы которой соединены со входом вычитак)щего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для УМНОЖЕНИЯ и ДЕЛЕНИЯ ЧАСТОТНО- ИМПУЛЬСНЫХ СИГНАЛОВ | 1972 |

|

SU333564A1 |

| УСТРОЙСТВО для ЦИФРОВОГО РЕГУЛИРОВАНИЯ СКОРОСТИ | 1973 |

|

SU374580A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU264457A1 |

| Цифровая система измерения глубинного положения морской пьезосейсмографной косы | 1976 |

|

SU894640A1 |

| Устройство для формирования импульсных последовательностей | 1975 |

|

SU618839A1 |

| Устройство для умножения двоичных чисел | 1973 |

|

SU482741A1 |

| Преобразователь частоты в код | 1971 |

|

SU443482A1 |

| Автоматическое устройство для формирования и испытания химического источника тока | 1983 |

|

SU1112446A1 |

| Преобразователь код-частота | 1980 |

|

SU869059A1 |

| ОДТЕНТНО-ТЕХНН-Г- :^':и|БИБЛИОТЕКА | 1970 |

|

SU287404A1 |

Даты

1970-01-01—Публикация