1

Изобретение относится к автоматике и вычислительной технике.

Целью изобретения является повышение надежности устройства.

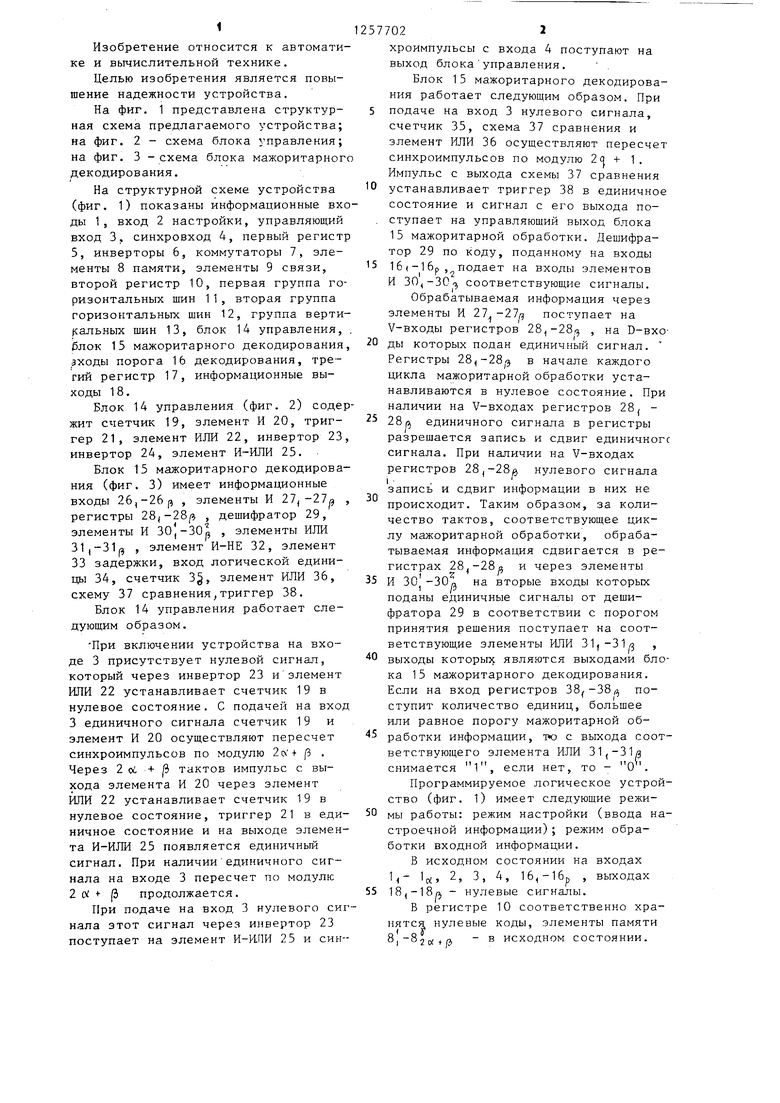

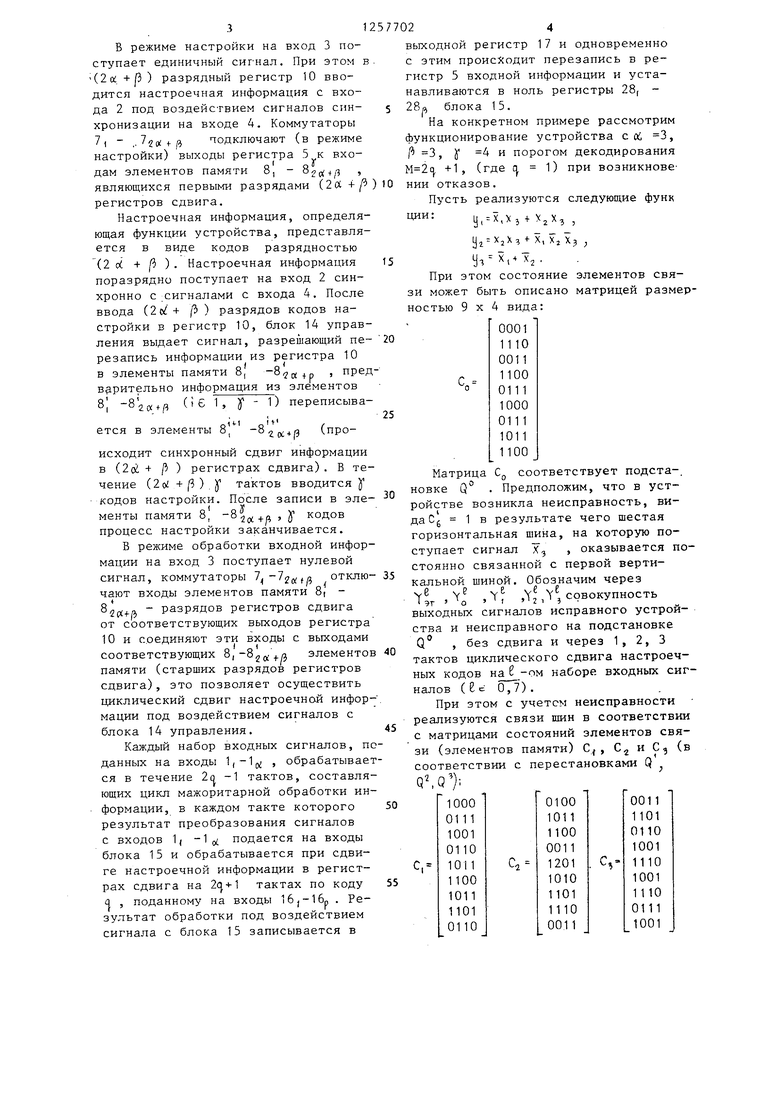

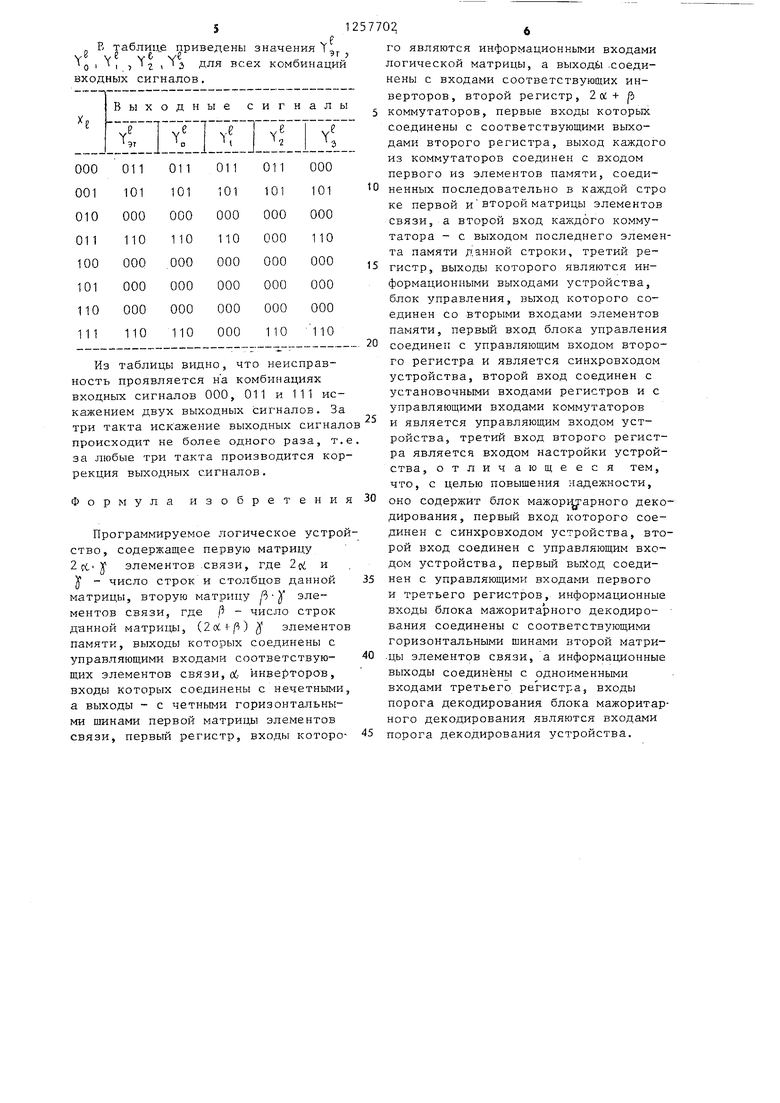

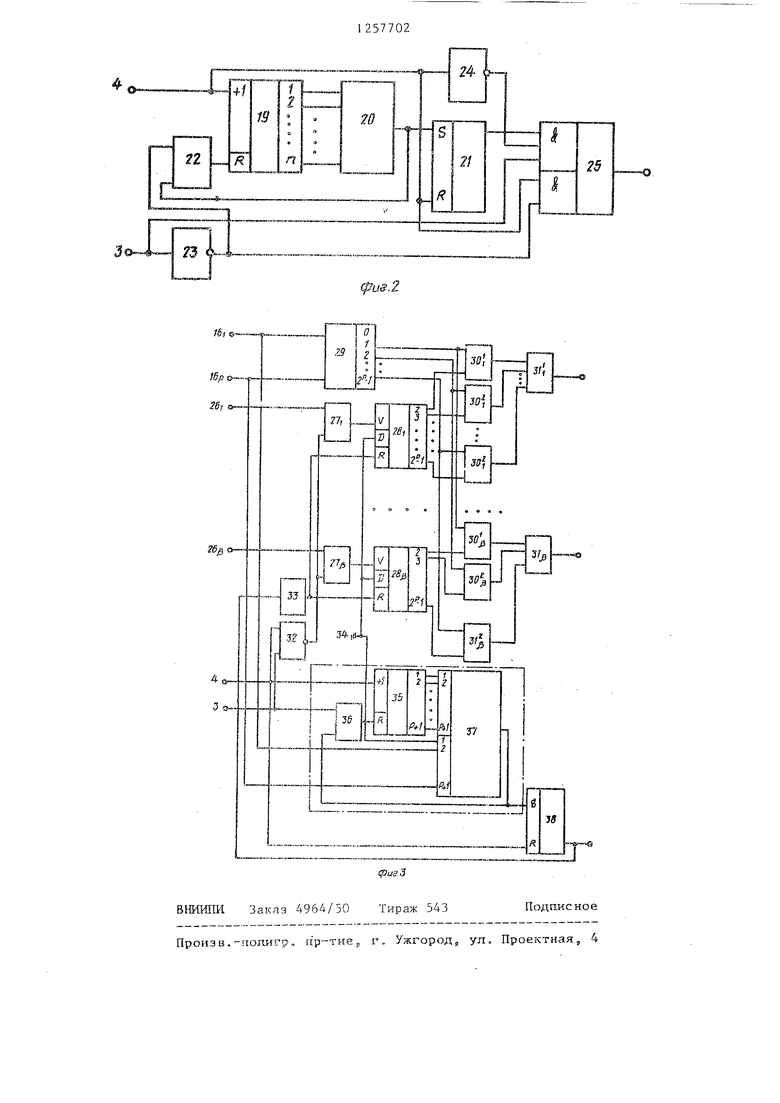

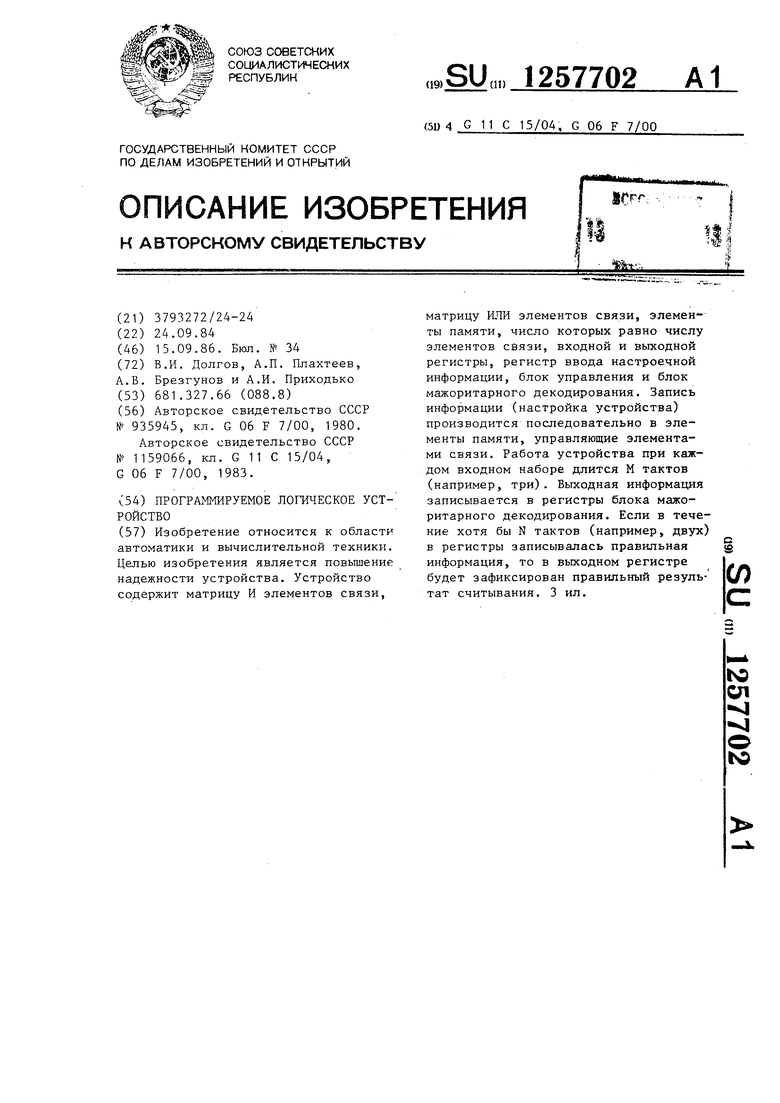

На фиг, 1 лредставлена структурная схема предлагаемого устройства; на фиг. 2 - схема блока управления; на фиг, 3 -схема блока мажоритарног декодирования.

На структурной схеме устройства (фиг, 1) показаны информационные входы 1, вход 2 настройки, управляющий вход 3, синхровход 4, первый регистр 5, инверторы 6, коммутаторы 7, элементы 8 памяти, элементы 9 связи, второй регистр 10, первая группа горизонтальных шин 11, вторая группа горизонтальных шин 12, группа верти- (сальных шин 13, блок 14 управления, Ьлок 15 мажоритарного декодирования зходы порога 16 декодирования, третий регистр 17, информационные выходы 18.

Блок 14 управления (фиг. 2) содержит счетчик 19, элемент И 20, триггер 21, элемент ИЛИ 22, инвертор 23, инвертор 24, элемент 25.

Блок 15 мажоритарного декодирования (фиг. 3) имеет информационные входы 26,-26р , элементы И 27,-27д , регистры 28(-28 , дешифратор 29, элементы И 30,-ЗОа , элементы ИЛИ 31,-31 л , элемент И-НЕ 32, элемент 33 задержки, вход логической единицы 34, счетчик 3, элемент ИЛИ 36, схему 37 сравнения,триггер 38,

Блок 14 управления работает следующим образом.

При включении устройства на входе 3 присутствует нулевой сигнал, который через инвертор 23 и элемент ИЛИ 22 устанавливает счетчик 19 в нулевое состояние. С подачей на вход 3 единичного сигнала счетчик 19 и элемент И 20 осуществляют пересчет синхроимпульсов по модулю 2cv + р . Через 2 oi р тактов импульс с выхода элемента И 20 через элемент ИЛИ 22 устанавливает счетчик 19 в нулевое состояние, триггер 21 в единичное состояние и на выходе элемента И-ИЛИ 25 появляется единичный сигнал. При наличии единичного сигнала на входе 3 пересчет по модулю 2 (У (3 продолжается.

При подаче на вход 3 нулевого сигнала этот сигнал через инвертор 23 поступает на элемент И-ИПИ 25 и син-577022

хроимпульсы с входа 4 поступают на выход блока управления.

Блок 15 мажоритарного декодирования работает следующим образом. При 5 подаче на вход 3 нулевого сигнала, счетчик 35, схема 37 сравнения и элемент ИЛИ 36 осуществляют пересчет синхроимпульсов по модулю 2q + 1. Импульс с выхода схемы 37 сравнения

0 устанавливает триггер 38 в единичное

состояние и сигнал с его выхода по- . ступает на управляющий выход блока 15 мажоритарной обработки. Дешифратор 29 по коду, поданному на входы

5 16 ( ,,подает на входы элементов И 30, соответствующие сигналы. Обрабатываемая информация через элементы И поступает на V-входы регистров 28,-28,,з на D-exo- ды которых подан единичный сигнал. Регистры 28, в начале каждого цикла мажоритарной обработки устанавливаются в нулевое состояние. При наличии на V-входах регистров 28, - 28л, единичного сигнала в регистры разрешается запись и сдвиг единичного сигнала. При наличии на V-входах регистров 28,-28й нулевого сигнала

0

запись и сдвиг информации в них не

происходит. Таким образом, за количество тактов, соответствующее циклу мажоритарной обработки, обрабатываемая информация сдвигается в регистрах а и через элементы

И 30 п вторые входы которых поданы единичные сигналы от дешифратора 29 в соответствии с порогом принятия решения поступает на соответствующие элементы ИЛИ 31,-31 л

выходы которых являются выходами блока 15 мажоритарного декодирования.

Если на вход регистров 38,-38д по I ступит количество единиц, большее

или равное порогу мажоритарной об- работки информации, тю с выхода соответствующего элемента ИЛИ 31,-31/g снимается 1, если нет, то - О .

Программируемое логическое устройство (фиг. 1) имеет следующие режи- мы работы: режим настройки (ввода настроечной информации); режим обработки входной информации.

В исходном состоянии на входах 1,- IP/, 2, 3, 4, 16,-16р , выходах 18,-18rj - нулевые сигналы.

В регистре 10 соответственно хранятся нулевые коды, элементы памяти (; + 0 исходном состоянии.

3

В режиме настройки на вход 3 поступает единичный сигнал. При этом (2 и +р ) разрядный регистр 10 вводится настроечная информация с входа 2 под воздействием сигналов синхронизации на входе 4. Коммутаторы ( .. 72iXf/ подключают (в режиме настройки) выходы регистра 5 к вхо

дам

элементов памяти 8, - Sg

являющихся первыми разрядами (2(Х +)10

регистров сдвига.

Настроечная информация, определяющая функции устройства, представляется в виде кодов разрядностью (2 о( + (5 ) . Настроечная информация поразрядно поступает на вход 2 синхронно с сигналами с входа 4. После ввода ( /3 ) разрядов кодов настройки в регистр 10, блок 14 управления выдает сигнал, разрешающий пе- резапись информации из регистра 10 в элементы памяти 8, , пред вэрительно информация из элементов

2 tp

(16 1, Jf - 1) переписывается в элементы 8

it-1

(про гл + р

исходит синхронный сдвиг информации в (2oi н- / ) регистрах сдвига) . В течение (2ог + f ) . jf тактов вводится Jf кодов настройки. После записи в эле- менты памяти 8, , у кодов процесс настройки заканчивается.

В режиме обработки входной информации на вход 3 поступает нулевой сигнал, коммутаторы cttPi отклю- чают входы элементов памяти 8| - S ftfft разрядов регистров сдвига от соответствующих выходов регистра 10 и соединяют эти входы с выходами соответствующих Sj-Bjo +a элементов памяти (старших разрядов регистров сдвига), это позволяет осуществить циклический сдвиг настроечной информации под воздействием сигналов с блока 14 управления.

Каждый набор входных сигналов, поданных на входы 1(-1jy; , обрабатывается в течение 2о -1 тактов, составляющих цикл мажоритарной обработки информации, в каждом такте которого результат преобразования сигналов с входов 1, -1 подается на входы блока 15 и обрабатывается при сдвиге настроечной информации в регистрах сдвига на тактах по коду а , поданному на входы 16)-16„ . Результат обработки под воздействием сигнала с блока 15 записывается в

нии отказов.

4

выходной регистр 17 и одновременно с этим происходит перезапись в регистр 5 входной информации и устанавливаются в ноль регистры 28, - 28а блока 15.

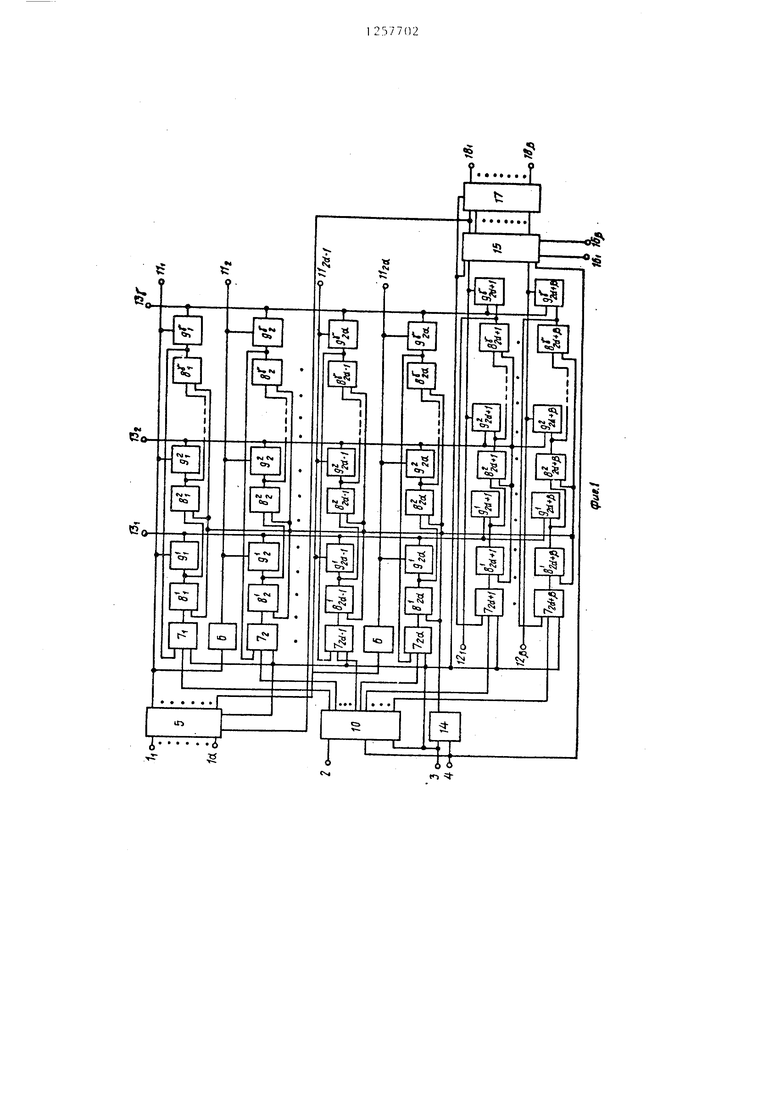

На конкретном примере рассмотрим функционирование устройства с oi 3, / 3, у 4 и порогом декодирования +1, (где с 1) при воэникнове

Пусть реализуются следующие функ Ции: У, Х,ХЗ + Х,Хз ,

, + X, XjX, ;

У, ХПХ,,

При этом состояние элементов связи может быть описано матрицей размерностью 9x4 вида:

0001

11 10

0011

1100

0111

1000

0111

1011

1100

Матрица С соответствует подста-. новке Q° . Предположим, что в устройстве возникла неисправность, вида С 1 в результате чего шестая горизонтальная шина, на которую поСоступает сигнал X,

оказывается постоянно связанной с первой вертикальной шиной. Обозначим через

С vE

, Л, ,2 Л

е

9Г

ВЫХОДНЫХ сигналов исправного устройства и неисправного на подстановке Q , без сдвига и через 1, 2, 3 тактов циклического сдвига настроечных кодов на -ом наборе входных CHI- налов ( 6 с; 0, 7) .

При этом с учетом неисправности реализуются связи шин в соответствии с матрицами состояний элементов связи (элементов памяти) С,, С и С (в соответствии с перестановками Q

1000 01 11 1001 0110 1011 1100 1011 1101 0110

с,

Е таблице приведены значения Y,,

v V ° V

о I м 7 2 1 3 всех комбинаций

Из таблицы видно, что неисправность проявляется н а комбинациях входных сигналов 000, 011 и 111 искажением двух выходных сигналов. За три такта искажение выходных сигнало происходит не более одного раза, т.е за любые три такта производится коррекция выходных сигналов.

Формула изобретения

Программируемое логическое устройство, содержащее первую матрицу 2fC у элементов .связи, где 2ci и У - число строк и столбцов данной матрицы, вторую матрицу - элементов связи, где ft - число строк данной матрицы, () элементов памяти, выходы которых соединены с управляющими входами соответствующих элементов связи,об инверторов, входы которых соединены с нечетными, а выходы - с четными горизонтальными шинами первой матрицы элементов связи, первый регистр, входы котороfO

15

20

25

30

5

0

5

го являются информационными входами логической матрицы, а выходь .соединены с входами соответствующих инверторов, второй регистр, 2« + р 5 коммутаторов, первые входы которых соединены с соответствующими выходами второго регистра, выход каждого из коммутаторов соединен с входом первого из элементов памяти, соединенных последовательно в каждой стро ке первой и второй матрицы элементов связи, а второй вход каждого коммутатора - с выходом последнего элемента памяти данной строки, третий регистр, выходы которого являются информационными выходами устройства, блок управления, выход которого соединен со вторыми входами элементов памяти, первый вход блока управления соединен с управляющим входом второго регистра и является синхровходом устройства, второй вход соединен с установочными входами регистров и с управляющими входами коммутаторов и является управляющим входом устройства, третий вход второго регистра является входом настройки устройства, отличающееся тем, что, с целью повышения надежности, оно содержит блок мажор1уарного декодирования, первый вход которого соединен с синхровходом устройства, второй вход соединен с управляющим входом устройства, первьй соединен с управляющими входами первого и третьего регистров, информационные входы блока мажоритарного декодирования соединены с соответствующими горизонтальными шинами второй матри- .цы элементов связи, а информационные выходы соединены с одноименными входами третьего регистра, входы порога декодирования блока мажоритарного декодирования являются входами порога декодирования устройства.

f

I « «I

(pus.2

ё 2b, o-

23

77,

0 i

г -/

30l

J l

JOf

/,,

/

эт

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая логическая матрица | 1983 |

|

SU1159066A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Программируемое запоминающее устройство | 1985 |

|

SU1282219A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

Изобретение относится к области автоматики и вычислительной техники. Целью изобретения является повышение надежности устройства. Устройство содержит матрицу И элементов связи, матрицу ИЛИ элементов связи, элемен- ты памяти, число которых равно числу элементов связи, входной и выходной регистры, регистр ввода настроечной информации, блок управления и блок мажоритарного декодирования. Запись информации (настройка устройства) производится последовательно в элементы памяти, управляющие элементами связи. Работа устройства при каждом входном наборе длится М тактов (например, три). Выходная информация записывается в регистры блока мажоритарного декодирования. Если в течение хотя бы N тактов (например, двух) в регистры записывалась правильная информация, то в выходном регистре будет зафиксирован правильный результат считывания. 3 ил. i СЛ С to СП

Kf

н1

ri

33

(,

3/

.хг

J4 liti.

36

ВНИИПИ Заказ 4964/50 Тираж 543

Пронзв.-попигр. cfp-тие, г. Ужгород, ул. Проектная, 4

3/J

A/

J7

Подписное

| Программируемая логическая матрица | 1980 |

|

SU935945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Программируемая логическая матрица | 1983 |

|

SU1159066A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-09-15—Публикация

1984-09-24—Подача