Изобретение относится к вычислительной .

Известеи нреобразователь средней частоты случайной последовательности импульсов, содержащий триггер, ключи, формирователь источники разноиолярных напряжений и интегрирующий усилитель. Его работа осиована на непрерывных иреобразоваииях тииа «времеииой интервал - число - временной иитервал.

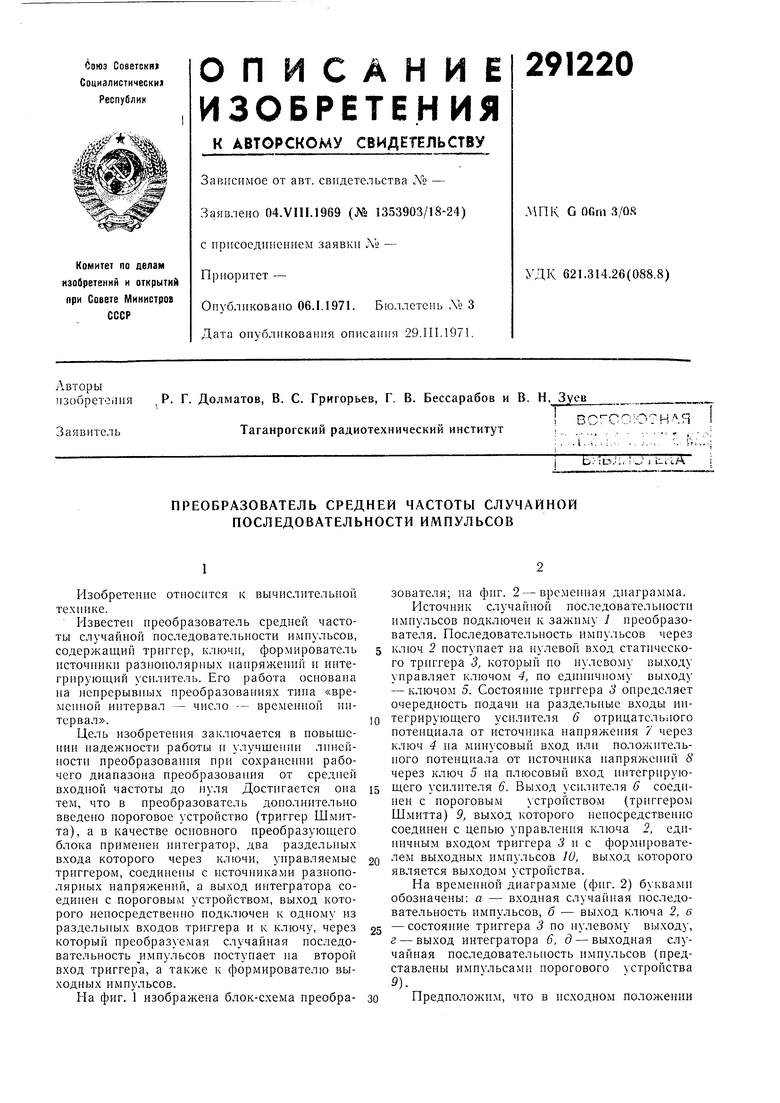

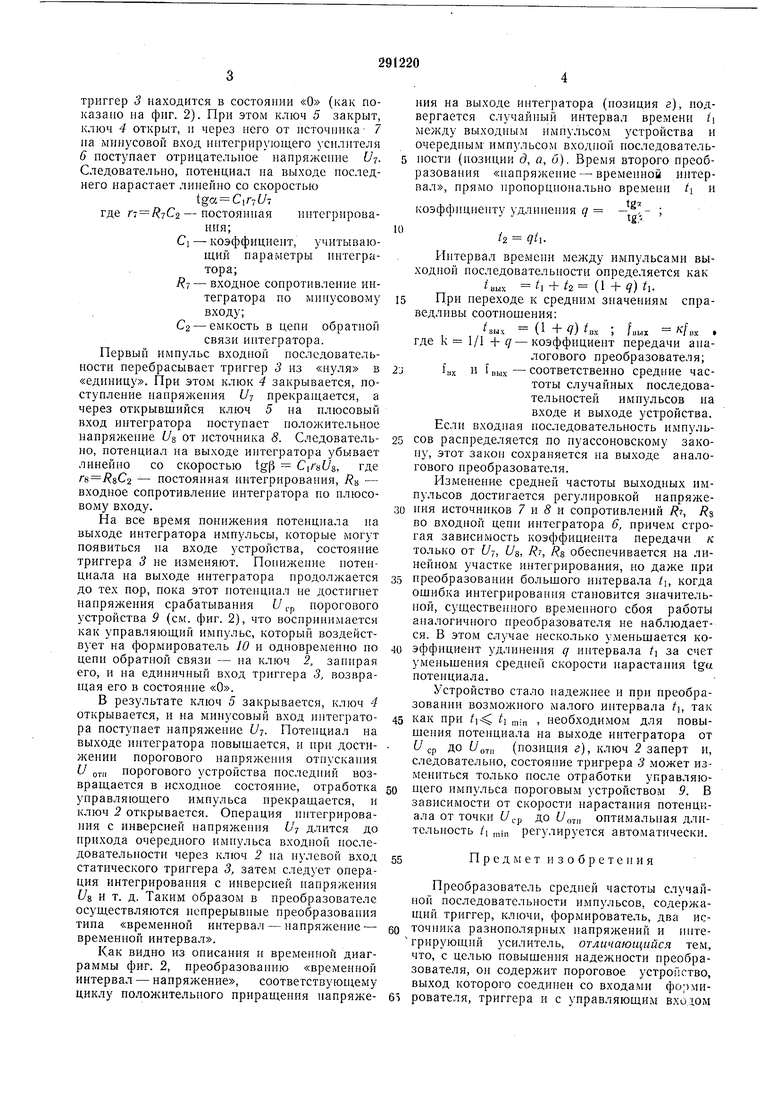

Цель изобретеиня заключается в повышении надежности работы и улучшении линейности преобразования при сохранегип рабочего диапазона преобразования от средней входной частоты до нуля Достигается она тем, что в преобразователь дополнительно введено пороговое устройство (триггер Шмитта), а в качестве основного преобразующего блока применен интегратор, два раздельных входа которого через ключи, управляемые триггером, соединены с источииками разнополярных нанряженнй, а выход интегратора соединен с пороговым устройством, выход которого непосредственно подключен к одному из раздельных входов триггера и к ключу, через который преобразуемая случайная носледовательность 1мпульсов поступает на второй вход триггера, а также к формирователю выходных импульсов.

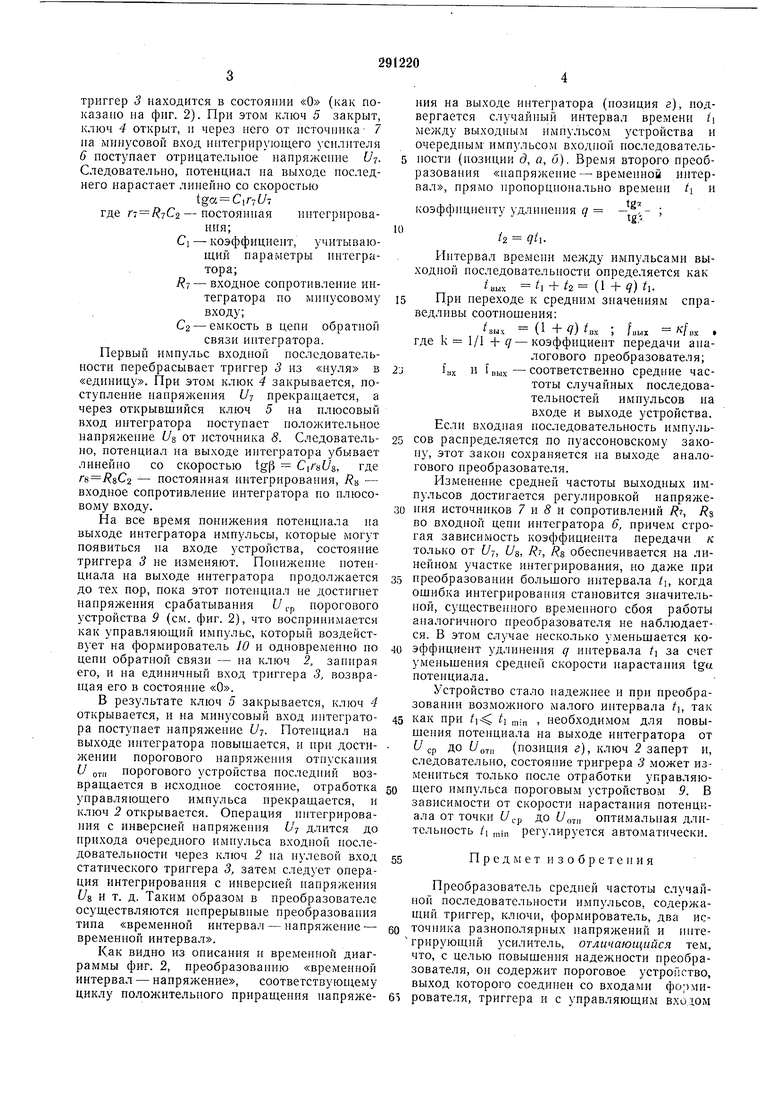

зователя; на фиг. 2 - времеиная диаграмма.

Источник случайиой последовательиости имиульсов подключеи к зажиму / преобразователя. Последовательность импульсов через ключ 2 поступает па нулевой вход статического триггера 3, который но нулевому выходу управляет ключом 4, но единнчно.му выходу - ключом 5. Состояние триггера 3 определяет очередность подачи на раздельные входы интегрирующего усилителя 6 отрицатель юго потеициала от источника напряжения 7 через ключ 4 на минусовый вход или положительного потенциала от источника напряжений 6 через ключ 5 иа плюсовый вход интегрирующего усилителя 6. Выход усилителя 6 соедииен с нороговым устройством (триггером Шмитта) Я выход которого неносредственио соединен с ценью управления ключа 2, единичным входом триггера 3 п с формирователем выходных имнульсов 10, вы.чод которого является выходом устройства.

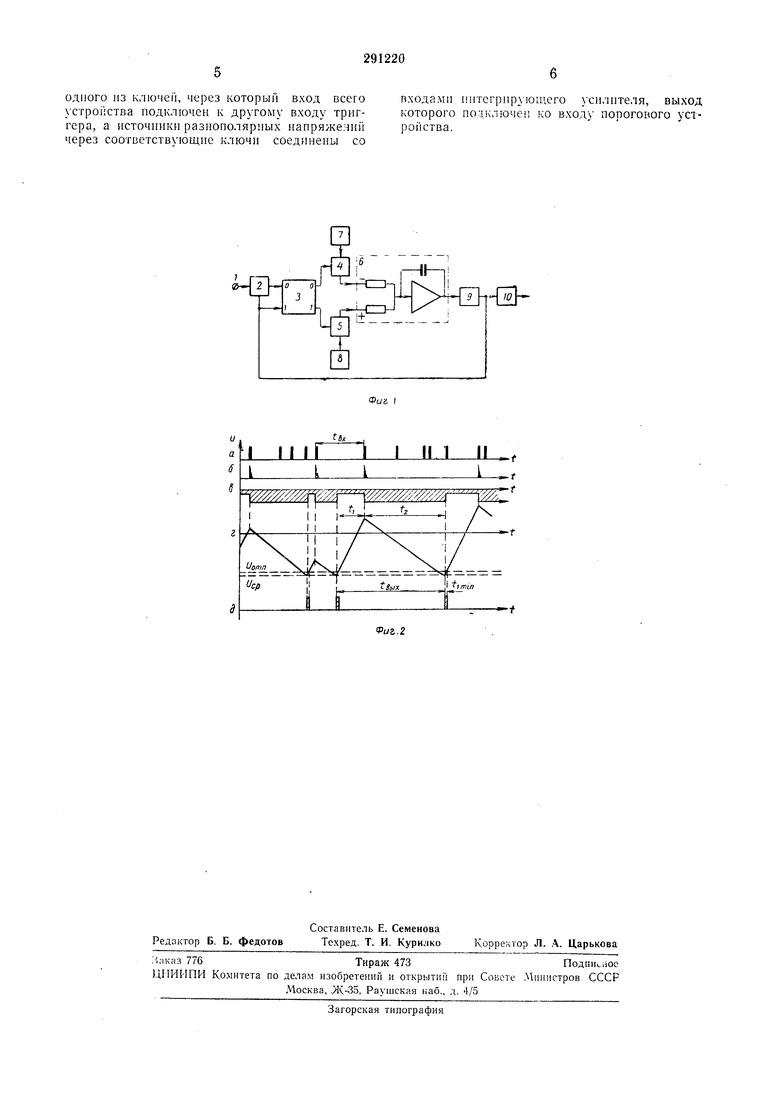

На временной диаграмме (фнг. 2) буквамн обозначены; а - входная случа шая последовательность импульсов, б - выход ключа 2, в

- состояние триггера 3 по нулевому выходу, г - выход интегратора 6, д - выходная случайная пос.тедовательность импу.тьсов (представлены импульсами порогового устройства 9).

триггер 3 находится в состоянии «О (как показано на фиг. 2). При этом ключ 5 закрыт, ключ 4 открыт, и через него от источника 7 иа минусовой вход ннтегрнрующего усилителя 6 поступает отрицательное наиряже1Н1е UT. Следовательно, потенциал иа выходе последнего нарастает лииейно со скоростью

tga-C /-7t/7

где r- RiCz - постоянная интегрирования;

С - коэффициент, учитывающий параметры интегратора;

- входное сопротивление интегратора по минусовому входу; Cz - емкость в цепп обратной

связи интегратора.

Первый импульс входной последовательности перебрасывает триггер 3 из «нуля в «единицу. При этом клюк 4 закрывается, поступление напряжения U прекращается, а через открывшийся ключ 5 на плюсовый вход интегратора поступает положительное напряжепие U от источника 8. Следовательно, потенциал на выходе интегратора убывает линейно со скоростью tgfi - ,, где - постоянная интегрирования, RS - входное сопротивление интегратора по плюсовому входу.

На все время понижения потенциала на выходе интегратора импульсы, которые могут появиться на входе устройства, состояние триггера 3 не изменяют. Понижение нотенциала иа выходе интегратора продолжается до тех пор, пока этот потенциал не достигнет нанряжения срабатывания ( порогового устройства 9 (см. фиг. 2), что воспринимается как управляющий импульс, который воздействует на формирователь 10 и одновременно но цепи обратной связи - на ключ 2, запирая его, и на единичный вход триггера 3, возвращая его в состояние «О.

В результате ключ 5 закрывается, ключ 4 открывается, и на минусовый вход интегратора поступает напряжение Uj. Потенциал на выходе интегратора повыщается, и при достижеиии порогового напряжения отпускаиия и отп порогового устройства последний возвращается в исходное состояние, отработка управляющего импульса прекращается, и ключ 2 открывается. Операция интегрироваиия с инверсией напряжения 6 длится до прихода очередного импульса входной последовательности через ключ 2 иа иулевой вход статического триггера 3, затем следует операция интегрирования с инверсией иапряжеиия t/8 и т. д. Таким образом в преобразователе осуществляются непрерывные преобразования типа «временной интервал - напряжение - временной интервал.

ния иа выходе интегратора (позиция г), подвергается случайный интервал времени /i между выходным имнульсом устройства и очередным- импульсом входной иоследователь5 ности (позиции д, а, б). Время второго преобразования «напряжение - временной интервал, прямо пропорционально времени /i и

коэфф1щнеиту удлинения 9 te-

/2 gii.

Иитервал времени между импульсами выходной носледовательности определяется как

/аых 1 + /2 (1 ) 1.

при переходе к средним значениям справедливы соотиощения:

вых (1 Ь ) вх j /иых Чек

где k 1/1 4-(7 - коэффициент передачи аиалогового преобразователя;

IBX и I аьк-соответственно средние частоты случайных последовательностей импульсов на входе и выходе устройства. Если входная последовательность импульсов распределяется по пуассоновскому закону, этот закон сохраняется иа выходе аналогового преобразователя.

Изменение средней частоты выходных импульсов достигается регулировкой иапряжеиия источников 7 и S и сопротивлений /, R, во входной цепи интегратора 6, причем строгая зависимость коэффициента передачи к только от Uj, Us, Rj, Rs обеспечивается на линейном участке интегрирования, но даже нри нреобразованни больщого интервала ь когда ощибка иитегрирования стаиовится значительной, существенного временного сбоя работы аналогичного преобразователя не наблюдается. В этом случае несколько уменьшается коэффициент удлинения q иитервала t за счет уменьщення средней скорости нарастания tga иотеициала.

Устройство стало иадежнее и при преобразовании возможного малого интервала f}, так как при ii min . необходимом для повыщення потенциала на выходе интегратора от и f.p до иg, (позиция г), ключ 2 заперт и, следовательно, состояпие тригрера 3 может измениться только после отработки управляющего импульса пороговым устройством 9. В зависимости от скорости иарастания потенциала от точки t/cp до f/oTii оптимальпая длительность /I ,„;„ регулируется автоматически.

Предмет изобретения

55

Преобразователь средней частоты случайной последовательности импульсов, содержащий триггер, ключн, формирователь, два ис60 точиика разнополярных напряжений и пнтегрирующий усилитель, отличающийся тем, что, с целью повышения надежности нреобразователя, он содеря ит пороговое устроГютво, выход которого соединен со входами формное рователя, триггера и с управляющим входом

одного из ключей, через который вход всего устройства подключен к другому входу триггера, а источники разиополярных напряжений через соответствующие ключи соединены со

входами иитегрнрующего усилителя, выход которого подключе 1СО входу аорогоЕюго устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU342296A1 |

| Устройство для запуска цифровых интеграторов | 1981 |

|

SU991424A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| СПОСОБ ИЗМЕРЕНИЯ КОЛИЧЕСТВА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ ПОСТОЯННОГО ТОКА | 1996 |

|

RU2103696C1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347028A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU947958A1 |

| Интегратор | 1982 |

|

SU1062726A1 |

| Измеритель среднеквадратического значения напряжения одиночного импульса случайной формы и длительности | 1987 |

|

SU1429054A1 |

| Преобразователь перемещения в напряжение | 1989 |

|

SU1837391A1 |

| Преобразователь фазового сдвига в временной интервал | 1984 |

|

SU1239628A1 |

ts.

I II II 111,

Авторы

Даты

1971-01-01—Публикация